# SCHOOL OF ELECTRICAL AND ELECTRONICS

# DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

# BASIC ELECTRICAL AND ELECTRONICS ENGINEERING-SEEA1101

# UNIT I DC CIRCUITS

# UNIT – I

# **DC CIRCUITS**

Electrical Quantities, Ohm's law, Kirchoff's laws, Resistors in series and parallel combinations, Current and Voltage division rules, Node and Mesh Analysis.

# ELECTRICAL QUANTITIES – DEFINITIONS, SYMBOLS AND UNITS

## • Charge:

A body is said to be charged positively, if it has deficit of electrons. It is said to be charged negatively if it has excess of electrons. The charge is measured in Coulombs and denoted by Q (or) q.

# 1 Coulomb = Charge on $6.28 \times 10^{18}$ electrons.

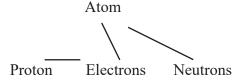

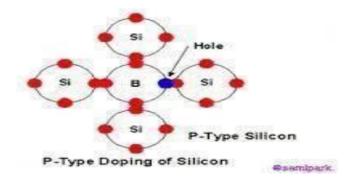

#### • Atom:

To understand the basic concepts of electric current, we should know the Modern Electron Theory. Consider the matter which is in the form of solid, liquid (or) gas. Smallest particle of matter is molecule. Minute Particles are called molecules, which are themselves made up of still minute particles known as Atoms.

Atom: Minute tiny Particles with the central Part Nucleus.

#### Figure 1.1

These are the types of tiny Particles in an Atom.

**Protons**: It is charged with positive charge.

Neutron: It is uncharged and hence it is neural.

**Electron**: It is revolving around nucleus. It is charged with small and constant amount of negative charge.

In an Atom, No of electrons = No of Protons

## • Electric Potential:

When a body is charged, either electrons are supplied on it (or) removed from it. In both cases the work is done. The ability of the charged body to do work is called electric potential. The charged body has the capacity to do, by moving the other charges by either attraction (or) repulsion.

The greater the capacity of a charged body to do work, the greater is its electric potential. And the work done, to charge a body to 1 Colomb is the measure of electric potential.

Electric potential, V=  $\frac{\text{Work done}}{\text{Charge}} = \frac{W}{Q}$

W = Work done per unit charge.

Q = Charge measured in Coulombs.

Unit of electric potential is **Joules** / **Coulomb** (or) Volt. If W = 1 joule; Q = 1 Coulomb, then V = 1/1 = 1 Volt.

A body is said to have an electric potential of 1 Volt, if one Joule of work is done to charge a body to one Coulomb. Hence greater the Joules / Coulomb on a charged body, greater is electric potential.

#### • Potential Difference:

The difference in the potentials of two charged bodies is called potential difference.

Consider two charged bodies A and B having Potentials of 5 Volts and 3 Volts respectively.

Potential Difference is +2v.

Unit of potential difference is Volts.

Potential difference is sometimes called Voltage.

#### • Electric Current:

Flow of free electrons through a conductor is called electric current. Its unit is Ampere (or) Coulomb / sec.

Current, (I) =

$$\frac{\text{Charge}(q)}{\text{Sec Time}(t)} = \frac{q}{t}$$

Coulombs /

In differential form,  $i = \frac{dq}{dt}$  Coulombs / Sec

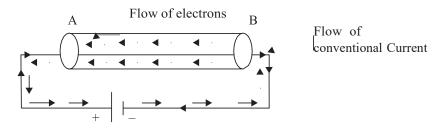

Consider a conducting material like metal, say Copper. A large number of free electrons are available. They move from one Atom to the other at random, before an electric force is applied. When an electric potential difference is applied across the metallic conductors, free electrons start moving towards the positive terminal of the cell. This continuous flow of electrons forms electric current. According to modern electronic theory, the direction of conventional current is form positive terminal to negative terminal through the external circuit.

Figure 1.2

Thus, a wire is said to carry a current of 1 Ampere when charge flows through it at the rate of one Coulomb per second.

#### • Resistance:

Consider a conductor which is provided some potential difference. The free electrons start moving in a particular direction. While moving, the free electrons may collide with some Atoms (or) Molecules. They oppose the flow of electrons. Resistance is defined as the property of the substance due to which restricts the flow of electrons through the conductor. Resistance may, also be defined as the physical property of the substance due to which it opposes (or) restricts the flow of electricity (i.e. electrons) through it. Its unit is Ohms.

A wire is said to have a resistance of 1 ohm if a potential difference of 1V across the ends causes current of 1 Amp to flow through it (or) a wire is said to have a resistance of 1 ohm if it releases 1 Joule, when a current of 1A flows through it.

#### • Laws of Resistance:

The electrical resistance (R) of a metallic conductor depends upon the various Factors as given below,

- (i) It is directly proportional to length l, ie, R  $\alpha$  l

- (ii) It is inversely proportional to the cross sectional area of the Conductor, ie, R  $\alpha \frac{l}{\Lambda}$

- (iii) It depends upon the nature of the material of the conductor.

- (iv) It depends upon the temperature of the conductor.

From the First three points and assuming the temperature to remain constant, we get,

$$R \alpha \frac{1}{A}$$

$$R = \rho \frac{1}{A}$$

$\rho$  ('Rho') is a constant of proportionality called **Resistivity** (or) Specific Resistance of the material of the conductor. The value of  $\rho$  depend upon the nature of the material of the conductor.

# • Specific Resistance (or) Resistivity:

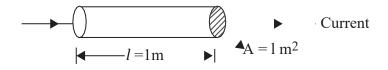

Resistance of a wire is given by  $R = \rho \frac{1}{A}$

If l = 1 metre,  $A = 1m^2$  then,  $R = \rho$ . The resistance offered by a wire of length 1 metre and across sectional area of Cross-section of  $1m^2$  is called the Resistivity of the material of the wire.

#### Figure 1.3

If a cube of one meter side is taken instead of wire,  $\rho$  is defined as below., Let l = 1 metre, A = 1 m<sup>2</sup>, then  $R = \rho$ . "Hence, the resistance between the opposite faces of 1 metre cube of the given material is called the resistivity of that material". The unit of resistivity is ohm-metre RA  $\Omega m^2$

$$[\rho = \underline{\qquad} = \underline{\qquad} = \Omega m (ohm-metre) ]l$$

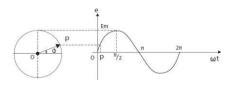

Current

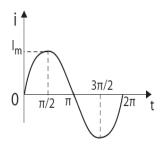

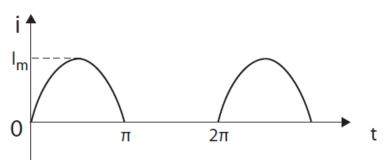

Current

Im

Current

Im

Current

Figure 1.4

# • Conductance (or) Specific Conductance:

Conductance is the inducement to the flow of current. Hence, Conductance is the reciprocal of resistance. It is denoted by symbol G.

$$G = \frac{1}{R} = \frac{A}{\rho l} = \sigma \frac{A}{l}$$

G is measured in mho Symbol for its unit is (U)

$$\sigma = \frac{1}{\rho}$$

Here,  $\sigma$  is called the Conductivity (or) Specific Conductance of the material

#### • Conductivity (or ) Specific Conductance:

Conductivity is the property (or) nature of the material due to which it allows flow of current through it.

$$G = \sigma \frac{A}{l}$$

(or)  $\sigma = G \frac{l}{A}$

Substituting the units of various quantities we get

$$\sigma = \frac{\text{mho*m}}{\text{m}^2} = \text{mho/metre}$$

... The S.I unit of Conductivity is mho/metre.

#### • Electric Power:

The rate at which the work is done in an electric circuit is called electric power.

Electric Power =

$$\frac{\text{Work done in an electric circuit}}{\text{Time}}$$

When voltage is applied to a circuit, it causes current to flow through it. The work done inmoving the electrons in a unit time is called Electric Power. The unit of Electric Power is Joules/sec (or) Watt.  $< \Upsilon P = VI = I^2 R = V^2 / R'_f$

#### • Electrical Energy:

The total work done in an electric circuit is called electrical energy.

ie, Electrical Energy = (Electrical Power)\*(Time)

Electrical Energy = I<sup>2</sup>Rt =

$$\frac{V^2}{R}t$$

Electrical Energy is measured in Kilowatt hour (kwh)

**Problem 1.1** The resistance of a conductor  $1 \text{ mm}^2$  in cross section and 20 m long is 0.346  $\Omega$ . Determine the specific resistance of the conducting material.

# **Given Data**

Area of cross-section A = 1 mm<sup>2</sup> Length, 1 = 20 m Resistance, R = 0.346  $\Omega$

**Formula used:** Specific resistance of the Conducting Material,  $R = \frac{\rho l}{\rho}$

$$\Rightarrow \rho = \frac{RA}{l}$$

**Solution:** Area of Cross-section,  $A = 1mm^2$

$$= 1 * 10^{-6} m^2$$

A

$$\rho = \frac{1*10^{-6} * 0.346}{20} = 1.738*10^{-8} \,\Omega m$$

Specific Resistance of the conducting Material,  $\rho = 1.738^{*}10^{-8} \Omega m$ .

**Problem 1.2** A Coil consists of 2000 turns of copper wire having a crosssectional area of 1 mm<sup>2.</sup> The mean length per turn is 80 cm and resistivity of copper is 0.02  $\mu\Omega$ m at normal working temperature. Calculate the resistance of the coil.

# Given data:

No of turns = 2000 Length / turn = 80 cm =0.8 m

Resistivity, =  $0.02 \ \mu\Omega m = 0.02*10^{-6} \ \Omega m = 2*10^{-8} \ \Omega m$ Cross sectional area of the wire, A=  $1 mm^2 = 1*10^{-6}m^2$

# Solution:

Mean length of the wire, l = 2000\*0.8 = 1600 m.We know that,  $R = \rho \frac{l}{A}$ Substituting the Values,  $R = \frac{2*10^{-8}*1600}{1*10^{-6}} = 32\Omega$ Resistance of the coil =  $32\Omega$  **Problem 1.3** A wire of length 1m has a resistance of  $2\Omega$ . What is the resistance of the second wire, whose specific resistance is double that of first, if the length of wire is 3m and the diameter is double that of first?

#### **Given Data:**

For the first wire:  $l_1 = 1m$ ,  $R_1 = 2 \Omega$ ,  $\rho_1 = \rho$  (say)  $d_1 = d$  (say)

For the Second wire:  $l_2 = 3m$ ,  $d_2 = 2d$ ,  $\rho_2=2\rho$

#### Solution:

$$\frac{R_{2}}{2} = \rho_{2} \frac{l_{2}}{A_{2}} - \frac{2\rho^{*}3}{\frac{\pi(2d)^{2}}{4}} = \frac{6\rho}{\pi d^{2}}$$

(2)

Dividing equation (1) by (2),

$$\frac{\underline{4\rho}}{\pi d^2} \xrightarrow{\pi} \frac{d^2}{6\rho} \xrightarrow{4} \frac{R}{R_2} \xrightarrow{R_2} \frac{R}{R_2}$$

$$R = \frac{6R_1}{4} = \frac{6^* 2}{4} = 3 \Omega$$

$$R_2 = 3 \Omega$$

The Resistance of the second wire,  $R_2 = 3 \Omega$

**Problem 1.4** A Rectangular copper strip is 20 cm long, 0.1 cm wide and 0.4 cm thick. Determine the resistance between (i) opposite ends and (ii) opposite sides. The resistivity of copper is  $1.7*10^{-6} \Omega$ cm.

(i) Opposite Ends Wide, w = 0.1 cm Thickness, t = 0.4 cm Length, 1 = 20 cm (ii) Opposite Sides: Wide, w = 0.1 cm Thickness, t = 20 cm Length, 1 = 0.4 cm (a) Area =  $w^*t = 0.1^* 0.4 = 0.04cm^2$   $R_1 = \frac{\rho l}{A} = \frac{1.7 * 10^{-6} * 20}{0.04} = 0.85 * 10^{-3} \Omega$   $R_1 = 0.85 m \wedge$  [Opposite ends, referring to Figure 1.5] Area  $A = w^*t = 0.1^* 20 = -20cm^2$

Area,

$$A = w^* t = 0.1^* 20 = -20 cm^2$$

$R_2 = \frac{1.7 * 10^{-6} * 0.4}{2} = 0.34 * 10^{-6} \Omega$  [Opposite Sidesi referring to Figure 1.6]

$R_2 = 0.34 \mu \Omega$

**Problem 1.5** A silver wire of length 12m has a resistance of  $0.2\Omega$ . Find the specific resistivity of the material. The cross-sectional area of the wire is  $0.01 \text{ cm}^2$ .

$R = \frac{\rho l}{A} \implies \text{length, } 1 = 12\text{m}$ Resistance, R = 0.2Ω  $A = 0.01\text{ cm}^2$   $\rho = \frac{RA}{l} = \frac{0.2 * 0.01*10^{-4}}{12}$   $\rho = 1.688*10^{-8} \Omega m$

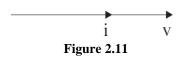

# **OHM'S LAW AND ITS LIMITATIONS**

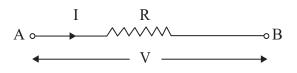

The relationship between DC potential difference (V) current (I) and Resistance (R) in a DC circuit was first discovered by the scientist George Simon Ohm, is called Ohm's law.

#### • Statement:

The ratio of potential difference between any two points of a conductor to the current following between them is constant, provided the physical condition

Where, R is the resistance between the two points of the conductor.

It can also be stated as, provided Resistance is kept constant, current is directly proportional to the potential difference across the ends of the conductor.

Power,

$$P = V * I = I^{2} R = \frac{V^{2}}{R}$$

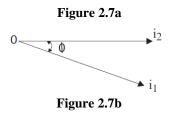

#### • Illustration:

Let the potential difference between points A and B be V volts and current flowing be I Amp. Then,  $\frac{V}{I}$  = Constant ,  $\frac{V}{I} = R$  (say)

Figure 1.7

We know that, if the voltage is doubled (2V), the current flowing will also be doubled (2I). So, the ratio  $\frac{V}{I}$  remains the same (ie, R). Also when voltage is measured in volts, current in ampere, then resistance will be in ohms.

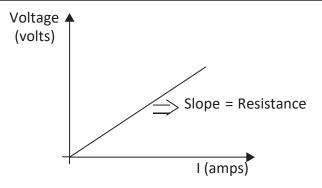

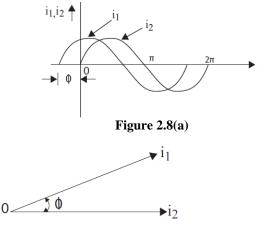

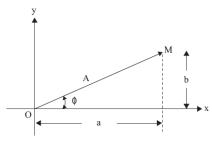

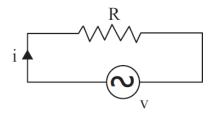

#### • Graphical representation of Ohm's law

[Slope line of the graph represents the resistance]

Figure 1.8

## • Limitations in ohm's law:

- (i) Ohm's law does not apply to all non-metallic conductors. For eg. Silico Carbide.

- (ii) It also does not apply to non-linear devices such as Zener diode, etc.

- (iii) Ohm's law is true for metal conductor at constant temperature. If the temperature changes the law is not applicable.

- Problems based on ohm's law:

**Problem 1.6**. An electric heater draws 8A from 250V supply. What is the power rating? Also find the resistance of the heater element.

## Given data:

Current, I = 8AVoltage, V = 250V

# Solution:

Power rating, P = VI = 8\*250 = 2000 WattResistance (R)  $= \frac{V}{I} = \frac{250}{8} = 31.25 \Omega$

**Problem 1.7** What will be the current drawn by a lamp rated at 250V, 40W, connected to a 230 V supply. **Given Data:**

Rated Power = 40 W Rated Voltage = 250 V

# Solution:

Resistance,

$$R = \frac{V^2}{P} = \frac{250^2}{40} = 1562.5 \ \Omega$$

Current,  $I = \frac{V}{P} = \frac{230}{1562.5} = 0.1472 \ A$

**Problem 1.8** A Battery has an emf of 12.8 volts and supplies a current of 3.24 A. What is the resistance of the circuit? How many Coulombs leave the battery in 5 minutes?

#### Solution:

$\frac{V}{C} = \frac{12.8}{Circuit Resistance, R} = 4 \Omega$  I 3.24 Charge flowing in 5 minutes = Current × time in seconds Charge flowing in 5 minutes =  $3.24 \times 5 \times 60 = 960$  Coulomb

**Problem 1.9** If a resistor is to dissipate energy at the rate of 250W, find the resistance for a terminal voltage of 100V.

# Given data:

Power = 250W Voltage = 100V

#### Solution:

Resistance,

$$R = \frac{V^2}{\rho} = \frac{100^2}{250} = 40 \Omega$$

$R = 40 \Omega$ .

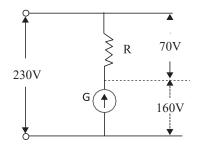

**Problem 1.10** A voltmeter has a resistance of, 20,200  $\Omega$ . When connected in series with an external resistance across a 230 V supply, the instrument reads 160 V. What is the value of external resistance?

The voltage drop across external resistance, R

$V_R = 230 - 160 = 70V$ Circuit current,  $I = \frac{160}{20,000} = \frac{1}{125}$ We know that, V = IR70 = IR $70 = \frac{1}{125}R$  $R = 8750 \Omega$

# **COMBINATION OF RESISTORS**

• Introduction:

The closed path followed by direct Current (DC) is called a DC Circuit A d.c circuit essentially consist of a source of DC power (eg. Battery, DC generator, etc.) the conductors used to carry current and the load. The load fora DC circuit is usually a resistance. In a DC circuit, loads (i.e, resistances) may be connected in series, parallel, series – parallel. Hence the resistor has to be connected in the desired way for getting the desired resistance.

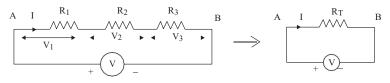

# Resistances in series (or) series combination

The circuit in which resistances are connected end to end so that there is one path for the current flow is called **series circuit**. The voltage source is connected across the free ends. [A and B]

Figure 1.10

In the above circuit, there is only one closed path, so only one current flows through all the elements. In other words, if the Current is same through all the resistors, the combination is called series combination.

# • To find equivalent Resistance:

Let, V = Applied voltage I = Source current = Current through each element  $V_{1,} V_{2}, V_{3}$  are the voltage across  $R_{1}, R_{2}$  and  $R_{3}$  respectively.

By Ohms law,

$$V_1 = IR_1$$

$V_2 = IR_2$  and  $V_3 = IR_3$

But

$V = V_1 + V_2 + V_3 = IR_1 + IR_2 + IR_3 = I$  ( $R_1 + R_2 + R_3$ )

$V = I(R_1 + R_2 + R_3)$

$V = IR_T$

$V = R_T$

$T$

The ratio of  $\binom{V_I}{}$  is the total resistance between points A and B and is called the total (or) equivalent resistance of the three resistances

$$R_T = R_1 + R_2 + R_3$$

Also,  $\frac{1}{G_T} = \frac{1}{G_1} + \frac{1}{G_2} + \frac{1}{G_3}$  (In terms of conductance)

$\therefore$  Equivalent resistance (R<sub>T</sub>) is the sum of all individual resistances.

# • Concepts of series circuit:

- i. The current is same through all elements.

- ii. The voltage is distributed. The voltage across the resistor is directly proportional to the current and resistance.

- iii. The equivalent resistance  $(R_T)$  is greater than the greatest individual resistance of that combination.

- iv. Voltage drops are additive.

- v. Powers are additive.

- vi. The applied voltage is equals to the sum of different voltage drops.

# Voltage Division Technique: (or) To find V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub> interms of V and R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>:

Equivalent Resistance,  $R_T = R_1 + R_2 + R_3$ By ohm's low,  $I = \frac{V}{R_T} = \frac{V}{R_1 + R_2 + R_3}$

$$V_1 = IR_1 = \frac{V}{R_T} R_1 = \frac{VR_1}{R_1 + R_2 + R_3}$$

$$V_{2} = IR_{2} = \frac{V}{R_{T}} R_{2} = \frac{VR_{2}}{R_{1} + R_{2} + R_{3}}$$

$$V_{3} = IR_{3} = \frac{V}{R_{T}} R_{3} = \frac{VR_{3}}{R_{1} + R_{2} + R_{3}}$$

: Voltage across any resistance in the series circuit,

$$\Rightarrow V_x = \frac{R_x}{R}V$$

**Note:** If there are n resistors each value of R ohms in series, then the total Resistance is given by,

$$R_T = n * R$$

## • Applications:

- \* When variable voltage is given to the load, a variable resistance (Rheostat) is connected in series with the load. Example: Fan regulator is connected in series with the fan.

- \* The series combination is used where many lamp of low voltages are to be operated on the main supply. Example: Decoration lights.

- \* When a load of low voltage is to be operated on a high voltage supply, a fixed value of resistance is connected in series with the load.

## • Disadvantage of Series Circuit:

- \* If a break occurs at any point in the circuit, no current will flow and the entire circuit becomes useless.

- \* If 5 numbers of lamps, each rated 230 volts are to be connected in series circuit, then the supply voltage should be 5 x 230 = 1150 volts. But voltage available for lighting circuit in each and every house is only 230 V. Hence, series circuit is not practicable for lighting circuits.

- \* Since electrical devices have different current ratings, they cannot be connected in series for efficient operation.

#### Problems based on series combination:

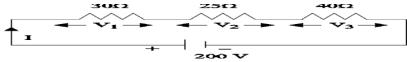

**Problem 1.11** Three resistors 30  $\Omega$ , 25  $\Omega$ , 45  $\Omega$  are connected in series across 200V. Calculate (i) Total resistance (ii) Current (iii) Potential difference across each element.

Figure 1.13 19

(i) Total Resistance  $(R_T)$

$$R_T = R_1 + R_2 + R_3$$

$$R_T = 30 + 25 + 45 = 100 \ \Omega$$

(ii) Current,  $I = \frac{V}{R_T} = \frac{200}{100} = 2 \ A$

(iii) Potential difference across each element,

$$V_1 = IR_1 = 2 * 30 = 60 V$$

$$V_2 = IR_2 = 2 * 25 = 50 V$$

$$V_3 = IR_3 = 2 * 45 = 90 V$$

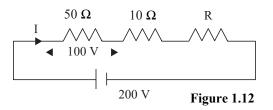

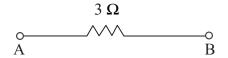

Problem 1.12 Find the value of 'R' in the circuit diagram, given below.

We know that,  $V_1 = IR_1$

$$I = V_1 / R_1 = 100/50 = 2 A$$

Similarly,  $V_2 = IR_2 = 2 * 10 = 20 V$

.

Total voltage drop,  $V = V_1 + V_2 + V_3$  $V_3 = V - (V_1 + V_2) = 200 - (100 + 20)$

$$V_{3} = V - (V_{1} + V_{2}) = 200 - (100 + 20)$$

$$V_{3} = 80 V$$

$$V_{3} = IR_{3}, R_{3} = V_{3} / I = 80/2 = 40 \Omega$$

$$V_{3} = R_{3} = 40 \Omega$$

**Problem 1.13** A 100W, 200V bulb is put in series with a 60W bulb across a supply. What will be the current drawn? What will be the voltage across the 60W bulb? What will be the supply voltage?

Figure 1.13 20

Sathyabama Institute of Science & Technology

Power dissipated in the first bulb,  $P_1 = V_1 I$ Current,  $I = P_1 / V_1 = 100/200 = 0.5 A$

Power dissipated in the second bulb,  $P_2 = V_2I$ Voltage across the 60 W bulb,

$$V = \frac{P_2}{2} = \frac{P_2}{I} = \frac{60}{0.5} = 120V$$

The supply voltage,  $V = V_1 + V_2 = 200 + 120$

$$V = 320V$$

The supply voltage, V = 320 V.

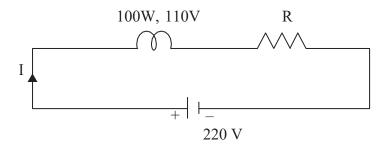

**Problem 1.14** An incandescent lamp is rated for 110V, 100W. Using suitable resistor how can you operate this lamp on 220V mains.

# Figure 1.14

Rated current of the lamp,  $I = \frac{Power}{Voltage} = \frac{100}{110} = 0.909$ A, I = 0.909A

For satisfactory operation of the lamp, Current of 0.909A should flow. When the voltage across the lamp is 110V, then the remaining voltage must be across R

Supply voltage =

$$V = 220$$

Volts

Voltage across  $R = V - 110$  Volts

ie,  $V_R = 220 - 110 = 110V$

By ohm's law,  $V_R = IR$

110 = 0.909 R $R = 121 \Omega$  **Problem 1.15** The lamps in a set of decoration lights are connected in series. If there are 20 lamps and each lamp has resistance of  $25\Omega$ , calculate the total resistance of the set of lamp and hence calculate the current taken from a supply of 230 volts.

| Given Data: | Supply voltage, $V = 230$ volts                                             |

|-------------|-----------------------------------------------------------------------------|

|             | Resistance of each lamp, $R = 25 \Omega$<br>No of lamps in series, $n = 20$ |

| Solution:   | Total Resistance, $R_T = n * R = 20 * 25$<br>$R_T = 500 \Omega$             |

Current from supply.  $I = \frac{V}{R_T} = \frac{230}{500} = 0.46 \ A$

**Problem 1.16** The field coil of a d.c generator has a resistance of  $250\Omega$  and is supplied from a 220 V source. If the current in the field coil is to be limited to 0.44 A. Calculate the resistance to be connected in series with the coil.

Given Data: Source voltage, V = 220 volts, I = 0.44 AField coil resistance,  $R_f = 250 \Omega$

**Solution:** Let the resistance in series with  $R_f$  be R in Ohms.

Total resistance,

$$R_T = R_f + R = 250 + R$$

Current,  $I = 0.44 A$

By ohm's law,  $R_T = \frac{V}{I} = \frac{220}{0.44} = 500 \Omega$

$R = 500 - 250 = 250 \Omega$

$R = 250 \Omega$

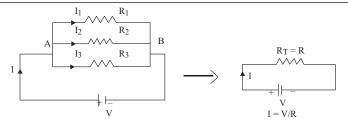

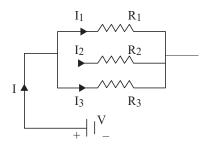

#### **Resistance in Parallel (or) Parallel Combination**

If one end of all the resistors are joined to a common point and the other ends are joined to another common point, the combination is said to be parallel combination. When the voltage source is applied to the common points, the voltage across each resistor will be same. Current in the each resistor is different and is given by ohm's law.

Let  $R_1$ ,  $R_2$ ,  $R_3$  be three resistors connected between the two common terminals A and B, as shown in the Figure 1.15(a)..

Figure 1.15

$$I = \frac{V}{R} \tag{1}$$

Let I<sub>1</sub>, I<sub>2</sub>, I<sub>3</sub> are the currents through R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> re *V* spectively. By ohm's law,

$$\begin{bmatrix} I_1 = \frac{V}{R}, I_2 = \frac{V}{R}, I_3 = \frac{V}{R} \end{bmatrix}$$

(2)

Total current is the sum of three individual currents,

$$I_T = I = I_1 + I_2 + I_3 \tag{3}$$

Substituting the above expression for the current in equation (3),

$$\frac{V}{R} = \frac{V}{R_1} + \frac{V}{R_2} + \frac{V}{R_3}$$

$$\frac{1}{R} = \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}$$

Referring to Figure (1.15(b)),  $R_T = R$

$$\frac{1}{R} = \frac{1}{R_T} \frac{1}{R_1} + \frac{1}{R_1} + \frac{1}{R_2} \frac{1}{R_3}$$

(4)

Hence, in the case of parallel combination the reciprocal of the equivalent resistance is equal to the sum of reciprocals of individual resistances. Multiplying both sides of equation (4) by  $V^2$ , we get

$$\frac{V^2}{R} = \frac{V^2}{R_1} + \frac{V^2}{R_2} + \frac{V^3}{R_3}$$

ie, Power dissipated by R = Power dissipated by  $R_1$  + Power dissipated by  $R_2$ + Power dissipated by  $R_3$  We know that reciprocal of Resistance is called as conductance.

Conductance = 1 / Resistance

[G = 1/R]

Equation (4) can be written as,

$G = G_1 + G_2 + G_3$

## • Concepts of Parallel Circuit:

- Voltage is same across all the elements.

- All elements will have individual currents, depends upon the resistance of element.

- The total resistance of a parallel circuit is always lesser than the smallest of the resistance.

- If n resistance each of R are connected in parallel then,

$$\frac{1}{R_T} = \frac{1}{R_1} + \frac{1}{R_2} + \dots \dots n terms$$

$$\frac{1}{R_T} = \frac{n}{R}$$

(or)

$$R_T = \frac{R}{n}$$

- Powers are additive.

- Conductance are additive.

- Branch currents are additive.

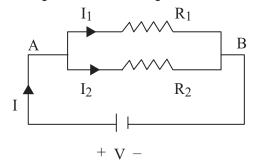

## • Current Division Technique:

Case (i) When two resistances are in parallel:

Two resistance  $R_1$  and  $R_2$  ohms are connected in parallel across a battery of V (volts) Current through  $R_2$  is  $I_2$  and through  $R_2$  is  $I_2$ . The total current is I.

Figure 1.16

To express  $I_1$  and  $I_2$  interms of I,  $R_1$  and  $R_2$  (or) to find branch currents  $I_1$ ,  $I_2$ :

$$I_2 R_2 = I_1 R_1$$

$$I_2 = \frac{I_1 R_1}{R_2}$$

(1)

(2)

Also, the total current,  $I = I_1 + I_2$

Substituting (1) in (2),

$$I_1 + \frac{I_1 R_1}{R_2} = I$$

$\frac{I_1 R_2 + I_1 R_1}{R_2} = I$

$I_1 (R_1 + R_2) = IR_2$

$I_1 = \frac{IR_2}{(R_1 + R_2)^2}$

Similarly,  $I_2 = \frac{IR_1}{(R_1 + R_2)}$

To find the equivalent Resistance, (RT) :

$$\frac{1}{R} = \frac{1}{R_T} = \frac{1}{R_1} + \frac{1}{R_2} \Longrightarrow \frac{1}{R_T} = \frac{R_2 + R_1}{R_1 R_2}$$

$$R_T = \frac{R_1 R_2}{R_1 + R_2}$$

Hence, the total value of two resistances connected parallel is equal to their product divided by their sum i.e.,

Equivalent Resistance =  $\frac{\text{Product of the two Resistance}}{\text{Sum of the two Resistane}}$

**Case (ii)** When three resistances are connected in parallel. Let  $R_1$ ,  $R_2$  and  $R_3$  be resistors in parallel. Let I be the supply current (or) total current.  $I_1$ ,  $I_2$ , and  $I_3$  are the currents through the resistors  $R_1$ ,  $R_2$  and  $R_3$ .

Figure 1.17

To find the equivalent Resistance (RT):

$$\frac{1}{R} = \frac{1}{R_T} = \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}$$

$$\frac{1}{R_T} = \frac{R_1 R_2 + R_2 R_3 + R_3 R_1}{R_1 R_2 R_3}$$

$$R_T = \frac{\frac{R_1 R_2 R_3}{R_1 R_2 R_3 + R_1 R_2 R_3}$$

## To find the branch currents I1, I2 and I3:

We know that,

$$I_1 + I_2 + I_3 = I$$

(1)

Also,  $I_3 R_3 = I_1 R_1 = I_2 R_2$

From the above expression, we can get expressions for  $I_2$  and  $I_3$  interms of  $I_1$  and substitute them in the equation (1)

$$I_{2} = \frac{I_{1}R_{1}}{R_{2}}; I_{3} = \frac{I_{1}R_{1}}{R_{3}}$$

$$I_{1} + \frac{I_{1}R_{1}}{R_{2}} + \frac{I_{1}R_{1}}{R_{3}} = I$$

$$I_{1} (1 + \frac{R}{R_{2}} + \frac{R_{1}}{R_{3}}) = I$$

$$\frac{I_{1}(R_{2}R_{3} + R_{3}R_{1} + R_{1}R_{2})}{R_{2}R_{3}} = I$$

$$I_{1} = \frac{I(R_{2}R_{3})}{(R_{1}R_{2} + R_{2}R_{3} + R_{3}R_{1})}$$

Similarly we can express I<sub>2</sub> and I<sub>3</sub> as,

$$I_{2} = \frac{I(R_{1}R_{3})}{(R_{1}R_{2} + R_{2}R_{3} + R_{3}R_{1})}$$

$$I_{3} = \frac{I(R_{1}R_{3})}{(R_{1}R_{2} + R_{2}R_{3} + R_{3}R_{1})}$$

#### • Advantages of parallel circuits:

- \* The electrical appliances rated for the same voltage but different powers can be connected in parallel without affecting each other's performance.

- \* If a break occurs in any one of the branch circuits, it will have no effect on the other branch circuits.

# • Applications of parallel circuits:

- \* All electrical appliances are connected in parallel. Each one of them can be controlled individually will the help of separate switches.

- \* Electrical wiring in Cinema Halls, auditoriums, House wiring etc.

# Comparison of series and parallel circuits:

| Series Circuit                          | Parallel Circuit                                                                 |

|-----------------------------------------|----------------------------------------------------------------------------------|

| The current is same through all the     | The current is divided, inversely                                                |

| elements.                               | proportional to resistance.                                                      |

| The voltage is distributed. It is       | The voltage is the same across each                                              |

| proportional to resistance.             | element in the parallel combination.                                             |

| The total (or) equivalent resistance    | Reciprocal of the equivalent                                                     |

| is equal to sum of individual           | resistance is equal to sum of                                                    |

| resistance, ie. $R_T = R_1 + R_2 + R_3$ | reciprocals of individual                                                        |

| Hence, the total resistance is greater  | resistances, ie, $\underline{1} = \underline{1} + \underline{1} + \underline{1}$ |

| than the greatest resistance in the     | $\overline{R_T}$ $\overline{R_1}$ $\overline{R_2}$ $\overline{R_3}$              |

| circuit.                                | Total resistance is lesser than the                                              |

|                                         | smallest resistances in the circuit.                                             |

| There is only one path for the flow     | There are more than one path for                                                 |

| of current.                             | the flow of current.                                                             |

# • Problems based on parallel combinations:

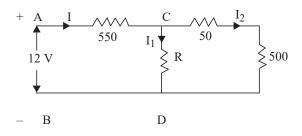

**Problem 1.17** What is the value of the unknown resistor R shown in Figure 1.18. If the voltage drop across the  $500\Omega$  resistor is 2.5V. All the resistor are in ohms.

# Figure 1.18

**Given Data:**

$$V_{500} = 2.5V$$

$$I = \frac{V_{500}}{2} = \frac{2.5}{500} = 0.005A$$

$$V_{50} = \text{Voltage across } 50 \ \Omega$$

$$V_{50} = I_2 R = 0.005 * 50 = 0.25 \text{ V}$$

$$V_{CD} = V_{50} + V_{500} = 0.25 + 2.5 = 2.75 \text{ V}$$

$$V_{550} = \text{Drop across } 550\Omega = 12 - 2.75 = 9.25 \text{ V}$$

$$I = \frac{V_{550}}{R} = \frac{9.25}{550} = 0.0168A$$

$$I = I_1 + I_2 \rightarrow I_1 = I - I_2 = 0.0168 - 0.005$$

$$I_1 = 0.0118A$$

$$R = \frac{V_{CD}}{I_1} = \frac{2.75}{0.0118} = 232.69 \ \Omega$$

$R = 232.69 \ \Omega$

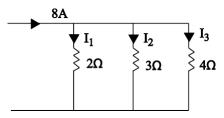

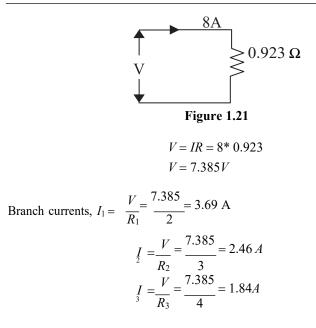

**Problem 1.18** Three resistors 2  $\Omega$ , 3  $\Omega$  and 4  $\Omega$  are in parallel. How will be a total current of 8A is divided.

Figure 1.19

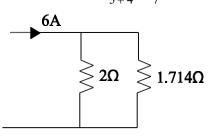

This given circuit can be reduced as, 3  $\Omega$  and 4  $\Omega$  are connected in parallel. Its equivalent resistances are,  $\frac{3*4}{3+4} = \frac{12}{7} = 1.714 \Omega$

# Figure 1.20

$1.714\,\Omega$  and  $2\,\Omega$  are connected in parallel, its equivalent resistance is 0.923  $\Omega$

$$\frac{1.714 * 2}{2 + 1.714} = 0.923$$

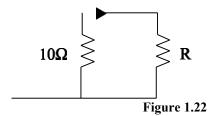

**Problem 1.19** What resistance must be connected in parallel with  $10\Omega$  to give an equivalent resistance of  $6\Omega$

R is connected in parallel with 10  $\Omega$  Resistor to given an equivalent resistance of 6  $\Omega.$

$$\frac{10 * R}{10 + R} = 6$$

$$10R = (10 + R)6$$

$$10R = 60 + 6R$$

$$10R - 6R = 60$$

$$R = \frac{60}{4} = 15 \Omega$$

$$R = 15 \Omega$$

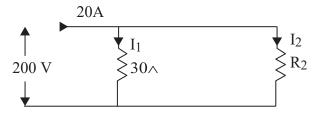

**Problem 1.20** Two resistors  $R_1$  and  $R_2$  are connected in Parallel and a Voltage of 200V DC is applied to the terminals. The total current drawn is 20A,  $R_1$ =30  $\Omega$ . Find  $R_2$  and power dissipated in each resistor, for the figure 1.23.

Figure 1.23

# **Given Data:**

$$V = 200V, I = 20A, R_{1} = 30 \Omega$$

Solution:  $I_{1} = \frac{V}{R_{1}} = \frac{200}{30} = 6.667 A$

$$I_{1} + I_{2} = I$$

$I_{2} = I - I_{1}$

$= 20 - 6.667 = 13.33 A$

$$IR$$

$I = R + R$

$1 = 2$

$13.33 = \frac{20 * 30}{30 + R_{2}}$

$(30 + R_{2})13.33 = 600$

$13.33R_{2} = 600 - 400$

$13.33R_{2} = 200$

$$R = \frac{200}{13.33} = 15 \Omega$$

Power dissipated in 30  $\Omega$ ,  $P_{1} = VI_{1} = 200*6.667$

$P_{1} = 1333 W$

Power dissipated in 15  $\Omega$ ,  $P_{2} = VI_{2}$

$P_{2} = 200*13.33 = 2667$

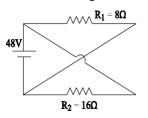

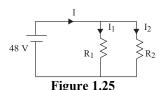

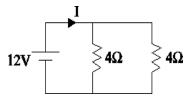

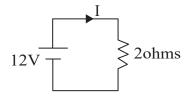

**Problem 1.21** Calculate the current supplied by the battery in the given circuit as shown in the figure 1.24.

Figure 1.24

Solution: The above given circuit can be redrawn as,

R<sub>1</sub> and R<sub>2</sub> are in parallel across the voltage of 48 volts. Equivalent Resistance,  $R_T = \frac{R_1 R_2}{R_1 + R_2} = \frac{8*16}{8+16} = \frac{16}{3} \Omega$   $R_T = 5.33 \wedge$  $I = \frac{V}{R} = \frac{48}{5.33} = 9A$

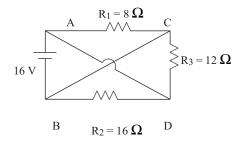

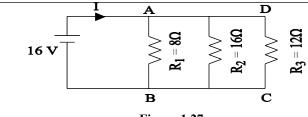

**Problem 1.22** Calculate the total resistance and battery current in the given circuit

Figure 1.26

The given above circuit can be re-drawn as,

Sathyabama Institute of Science & Technology

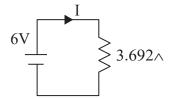

8  $\Omega$ , 16  $\Omega$ , 12  $\Omega$  are connected in parallel. Its equivalent resistance,  $R^{T} = \frac{R_{1}R_{2}R_{3}}{RR + R R + R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R R + R + R R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R + R$

Figure 1.28

$$R_T = \frac{8^*6^*12}{128 + 192 + 96} = 3.692 \ \Omega$$

$$R_T = 3.692 \ \Omega$$

$$I = \frac{V}{R} = \frac{16}{3.692} = 4.33A$$

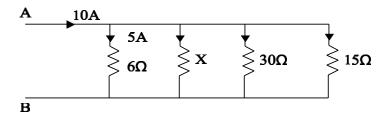

Problem 1.23 In the Circuit shown in the figure 1.29, calculate

- (i) The current in all resistors.

- (ii) The value of unknown resistance 'x'

- (iii) The equivalent resistance between A and B.

**Solution:** As all the resistors are in parallel, the voltage across each one is same. Give that current through 6  $\Omega$ , ie,  $I_{6 \Omega} = 5A$

Voltage across 6  $\Omega = 5 \times 6 = 30$  volts. Hence, current through 30  $\Omega$ ,  $I_{30} = \frac{V_{30}}{R} = \frac{30}{30} = 1A$ Similarly, current through 15  $\Omega$ ,  $I_{15} = \frac{V_{15}}{R} = \frac{30}{15} = 2A$ Total Current,  $I = I_6 + I_x + I_{30} + I_{15}$   $10 = 5 + I_x + 1 + 2$  $I_x = 2A$

Hence, the current flowing through the 'X' Resistor is,  $I_X = 2 A$ Value of the Resistor 'X' is given by,

$$X = \frac{30}{I_{\rm x}} = \frac{30}{2} = 15 \ \Omega$$

Let, the equivalent resistance across  $AB = R_T$

$$\frac{1}{R_T} = \frac{1}{6} + \frac{1}{x} + \frac{1}{30} + \frac{1}{15}$$

$$\frac{1}{R_T} = \frac{5 + 2 + 1 + 2}{30} = \frac{1}{3}$$

$$R_T = 3 \Omega$$

# Series — Parallel Combination

As the name suggests, this circuit is a combination of series and parallel circuits. A simple example of such a circuit is illustrated in Figure 1 30.  $R_3$  and  $R_2$  are resistors connected in parallel with each other and both together are connected in series with  $R_1$ .

Figure 1.30

Equivalent Resistance: R<sub>T</sub> for parallel combination.

$$R_p = \frac{R_2 R_3}{R_2 + R_3}$$

Total equivalent resistance of the circuit is given by,

$$R_T = R_1 + R_P$$

$$_T R = R_1 + \frac{R_2 R_3}{R_2 + R_3}$$

Voltage across parallel combination =  $I * \frac{R_2 R_3}{R_2 + R_3}$

# • Problems based on Series – Parallel Combination:

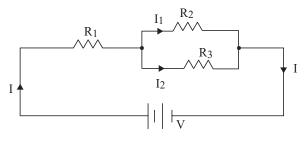

**Problem 1.24** In the circuit, find the current in all the resistors. Also calculate the supply voltage.

Figure 1.31

Voltage across  $15 \land$ ,  $V_{15} = I_{15} \times R = 8 \times 15 = 120V$

Resistors 2  $\Omega$ , 5  $\Omega$ , 10  $\Omega$  are connected in parallel, it equivalent resistance is given by,

$$R = \frac{2*5*10}{2\times5+5\times10+10\times2} = 1.25 \ \Omega$$

Voltage across the parallel Combination is given by

$$V_p = V_2 = V_5 = V_{10} = I \times R_P = 8 \times 1.25 = 10V$$

Total supply Voltage,  $V = V_{15}+V_p$

$$V = 120 + 10 = 130$$

V

$V = 130$ V

Hence, the Current through the parallel combination of the resistors are given by,

by, Current through 2  $\Omega$  resistor,  $I = \frac{V_2}{R} = \frac{10}{5} = 5A$ Current through 5  $\Omega$  Resistor,  $I = \frac{V_5}{R} = \frac{10}{5} = 2A$ Current through 10  $\Omega$  Resistor,  $I = \frac{V_{10}}{R} = \frac{10}{10} = 1A$

The Current of 8A across the parallel combination is divided as 5A, 2A, and 1A.

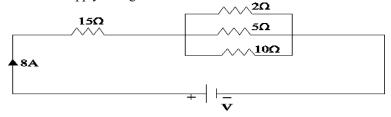

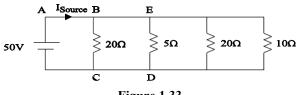

**Problem 1.25** Calculate the equivalent resistance offered by the circuit to the voltage source and also find its source current

Figure 1.32

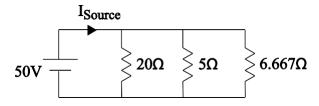

Solution: The given above circuit can be re-drawn as

Figure 1.33

20  $\Omega$  and 10  $\Omega$  resistors are connected in parallel, its equivalent resistance is given by,  $\frac{20 * 10}{20 + 10} = 6.667 \Omega$

The given circuit is reduced as,

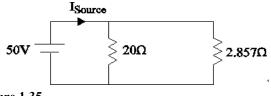

Figure 1.34

6.667 Ω and 5 Ω resistors are connected in parallel, its equivalent resistance is given by,  $\frac{6.667*5}{6.667+5} = 2.857 \Omega$

The circuit is reduced as,

Figure 1.35

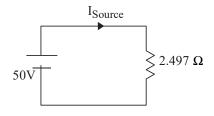

20  $\Omega$  and 2.857  $\Omega$  are connected in parallel. It equivalent resistance is,  $\frac{20 * 2.857}{20 + 2.857} = 2.497 \ \Omega$

The Circuit is re-drawn as,

Figure 1.36

Hence the equivalent resistance of the Circuit is  $R_T$ = 2.497  $\Omega$  =2.5  $\Omega$

Source Current of the Circuit is given by,

$$I_{\text{source}} = \frac{V}{R} = \frac{50}{2.5} = 20A$$

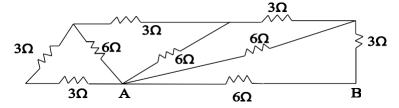

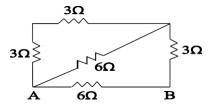

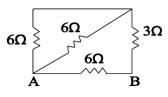

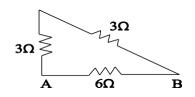

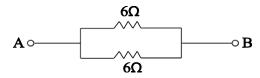

Problem 1.26 Find the equivalent resistance between the terminals A and B.

Figure 1.34

# Solution:

3  $\Omega$  and 3  $\Omega$  are connected in Series, it equivalent resistance is,  $(3 + 3) = 6 \Omega$ . The Circuit gets reduced as

Figure 1.38

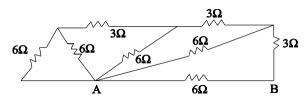

6  $\Omega$  and 6  $\Omega$  are connected in parallel. The circuit gets reduced as,

3  $\Omega$  and 3  $\Omega$  are connected in series (3 + 3 = 6  $\Omega$ ). The reduced Circuit is,

Figure 1.40

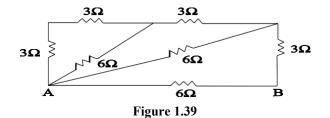

6 Ω and 6 Ω are connected in parallel. Its equivalent resistance,  $\frac{6^*6}{6+6} = 3 \Omega$

The circuit can be reduced as,

Figure 1.41

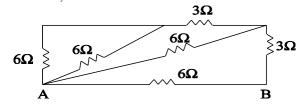

3  $\Omega$  and 3  $\Omega$  are connected in series.  $(3 + 3 = 6 \Omega)$ .

Figure 1.42

6 Ω and 6 Ω are connected in parallel. It equivalent resistance,  $\frac{6*6}{6+6} = 3 \Omega$ 6 + 6

Figure 1.43

3  $\Omega$  and 3  $\Omega$  are connected in series, the reduced Circuit is 3 + 3 = 6  $\Omega$

Figure 1.44

6  $\Omega$  and 6  $\Omega$  are connected in parallel.

$\frac{6^{*6}}{6+6}$  = 3  $\Omega$ . The equivalent resistance between the terminals A and B given by  $R_{AB}$  = 3  $\Omega$ .

Figure 1.45

$\therefore R_{AB} = 3 \Omega$

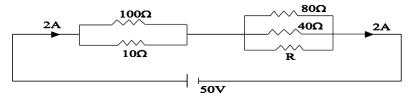

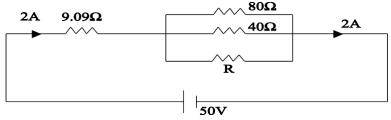

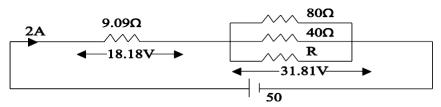

**Problem 1.27** Determine the value of R if the power dissipated in 10  $\Omega$  resistor is 90 W.

# Solution:

$100 \Omega$  and  $10 \Omega$  are connected in parallel.

Its equivalent resistance is,  $\frac{100 * 10}{100 + 10} = 9.09 \Omega$

The circuit is reduced as,

Figure 1.47

Current of 2A flows through the 9.09  $\Omega$  resistor. Voltage across 9.09  $\Omega$  is given by,

$$V_{9.09} = I_{9.09} \times R$$

$$V_{9.09} = 2 \times 9.09 = 18.18V$$

Similarly voltage across the unknown resistor V<sub>R</sub>,

$$V_R = V - V_{9.09} = 50 - 18.18 = 31.818V$$

#### Figure 1.48

Hence the Current through 40  $\Omega$ , 80  $\Omega$  resistors can be found out with the voltage drop of 31.818V across it.

$$I_{80} = \frac{V_R}{80} = \frac{31.818}{80} = 0.397 A$$

$$I_{40} = \frac{V_R}{40} = \frac{31.818}{40} = 0.7954 A$$

Hence current through the unknown resistor R is I<sub>R</sub>,

$$I_R = I - [I_{80} + I_{40}]$$

$$I_R = 2 - (0.397 + 0.7954) = 0.8075A$$

Hence, the value of the unknown Resistor R is given by

$$R = \frac{V_R}{I_R} = \frac{31.818}{0.8075} = 39.4 \ \Omega$$

The value of the unknown resistor R is given by,  $R = 39.4 \Omega$ .

Problem 1.28 Calculate the following for the circuits given,

Figure 1.49

- (i) Total resistance offered to the Source.

- (ii) Total Current from the Source.

- (iii) Power Supplied by the Source.

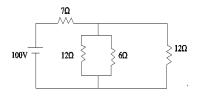

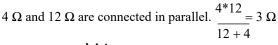

**Solution:** 12  $\Omega$  and 6  $\Omega$  are connected in Parallel.

Its equivalent resistance,  $\frac{12*6}{12+6} = 4 \Omega$ . The reduced circuit is given as, 7 $\Omega$ 100V 4 $\Omega$ 12 $\Omega$

# Figure 1.50

Figure 1.51

7  $\Omega$  and 3  $\Omega$  are connected in series, 7 + 3 = 10 $\Omega$

Total resistance offered to the Source,  $R = 10 \Omega$

Sathyabama Institute of Science & Technology

Total Current from the Source,  $I = \frac{100}{10} = 10 \text{ A}$

$$I = 10A$$

Power supplied by the Source,  $P = I^2 R = 10^2 \times 10 = 1000 W$

#### P = 1000W.

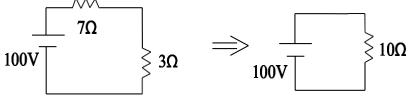

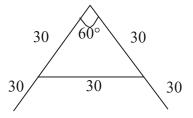

**Problem 1.29** A letter A is Constructed of an uniform wire of 1  $\Omega$  resistance per cm. The signs of the letter are 60cm long and the cross piece is 30cm long, Apex angle 60°. Find the resistance of the letter between two ends of the legs.

Figure 1.52

#### Solution:

The given circuit can be redrawn as,

Figure 1.53

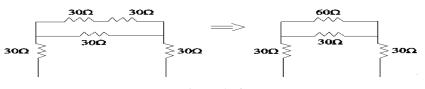

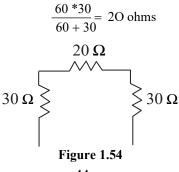

60  $\Omega$  and 30  $\Omega$  are connected in parallel

44

Equivalent Resistance =  $80 \Omega$ .

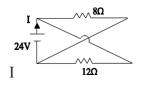

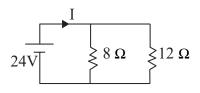

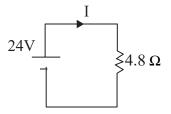

Problem 1.30 Find the current supplied by the battery.

Figure 1.55

# Solution:

The given circuit can be re-drawn as,

Figure 1.56

8  $\Omega$  and 12  $\Omega$  connected in parallel.

$$\frac{8^{*12}}{8+12} = 4.8 \ \Omega$$

Reduced circuit is,

Figure 1.57

Current,  $I = \frac{V}{R} = \frac{24}{4.8} = 5A$ I = 5A **Problem 1.31** Find the current supplied by the battery for the figure shown below.

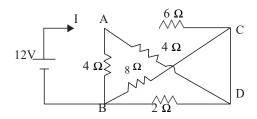

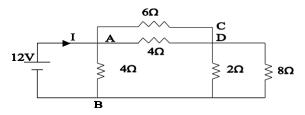

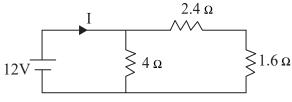

Figure 1.58

# Solution:

The given above circuit can be redrawn as,

4  $\Omega$  and 6  $\Omega$  are connected in parallel.  $\frac{6^* 4}{6+4} = 2.4 \Omega$

Similarly, 2  $\Omega$  and 8  $\Omega$  are connected in parallel.

$$\frac{2^{*8}}{8+2} = 1.6 \Omega$$

The reduced circuit can be re drawn as,

Figure 1.60

2.4  $\Omega$  and 1.6  $\Omega$  are connected in series. 2.4 +1.6 = 4  $\Omega$

## Figure 1.61

4 Ω and 4 Ω are connected in parallel  $\frac{4^* 4}{4+4} = 2 Ω$

The reduced circuit is,

Figure 1.62

$$I = \frac{V}{R} = \frac{12}{2} = 6A$$

Current I, supplied by the battery = 6A.

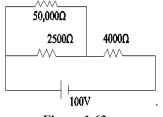

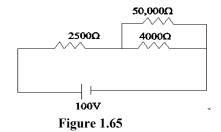

**Problem 1.32** Two Resistors  $R_1 = 2500 \Omega$  and  $R_2 = 4000 \Omega$  are joined in series and connected to a 100v supply. The voltage drop across  $R_1$  and  $R_2$  are measured successively by a voltmeter having a resistance of 50,000  $\Omega$ . Find the sum of the Reading.

## Solution:

Case (i) A voltmeter is connected across 2500  $\Omega$ .

Figure 1.63

2500  $\Omega$  and 50,000  $\Omega$  are connected is parallel.

$\frac{2500 * 50000}{2500 + 50000} = 2381$  ohms

#### Figure 1.64

2381  $\Omega$  and 4000  $\Omega$  are connected in series. 2381+ 4000 = 6381  $\Omega$

Current  $I = \frac{V}{R} = \frac{100}{6381} = 0.01567 \text{A}$

Voltage drop across, the Resister  $R_1$  is measured by connecting a voltmeter having resistance of 50,000 across  $R_1$ . Hence  $V_A$  be voltage drop across  $R_1$

$$V_A = IR = 0.01567 * 2381$$

$V_A = 37.31$ V

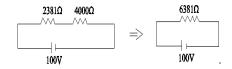

Case (ii) Voltmeter is connected across 4000  $\Omega$ .

4000  $\Omega$  and 50,000  $\Omega$  are connected in parallel.

$\frac{4000 * 50000}{4000 + 50000} = 3703.7$ ohms

Current,

$$I = \frac{V}{R} = \frac{100}{6203.7} = 0.0161 \text{ A}$$

Voltage drop across the resistor  $R_2$  is measured by connecting a voltmeter having resistance of 50000 across  $R_2$ . Hence,  $V_B$  be the voltage drop across  $R_2$ .

$$V_B = IR = 0.6161*3703.7$$

$V_B = 59.7$ V

The total voltage drop =  $V_A + V_B$

$$V = 37.31 + 59.7$$

$V = 97 \text{ V}$

**Problem 1.33** Find the value of 'R' and the total current when the total power dissipated in the network is 16W as shown in the figure.

#### Solution:

Total Power (P) = 16w Total Current,  $I = P = \frac{16}{2} = 2A$

Total Resistance,  $\begin{pmatrix} V & 8 \\ R & P \\ I^2 & I^2 \\ I^2$

Total Resistance between A and B is given by,

$$R_{AB} = \frac{2*8}{2+8} + \frac{4*R}{4+R}$$

$$4 = 1.6 + \frac{4R}{4+R}$$

$$4(4+R) = 1.6(4+R) + 4R R = 6 \Omega.$$

# **KIRCHOFF'S LAWS**

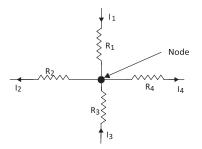

## Kirchhoff's current law

The kirchoff's current law states that the algebraic sum of currents in a node is zero.

It can also be stated that "sum of incoming currents is equal to sum of outgoing currents."

Kirchhoff's current law is applied at nodes of the circuit. A node is defined as two or more electrical elements joined together. The electrical elements may be resistors, inductors capacitors, voltage sources, current sources etc.

Consider a electrical network as shown below.

Figure 1.68

Four resistors are joined together to form a node. Each resistor carries different currents and they are indicated in the diagram.

- $I_1 \rightarrow$  Flows towards the node and it is considered as positive current. (+  $I_1$ )

- $I_2 \rightarrow$  Flows away from the node and it is considered as negative current. (-  $I_2$ )

- $I_3 \rightarrow$  Flows towards the node and it is considered as positive current.  $(+I_3)$

- $I_4 \rightarrow$  Flows away from the node and hence it is considered as negative current (-I<sub>4</sub>)

Applying KCL at the node, by diffinition-1 algebraic sum of currents in a node is zero.

$$+I_1 - I_2 + I_3 - I_4 = 0 \tag{1}$$

taking the  $I_2 \& I_4$  to other side

$$I_1 + I_3 = I_2 + I_4 \tag{2}$$

From equation (2) we get the definition -2. Where  $I_1 \& I_3$  are positive currents (Flowing towards the node)  $I_2 \& I_4$  are negative currents. (Flowing away from the node).

## Kirchoff's voltage Law: (KVL)

Kirchhoff's voltage law states that "sum of the voltages in a closed path (loop) is zero".

In electric circuit there will be closed path called as loops will be present.

The KVL is applied to the closed path only the loop will consists of voltage sources, resistors, inductors etc.

In the loop there will be voltage rise and voltage drop. This voltage rise and voltage drop depends on the direction traced in the loop. So it is important to understand the sign convention and the direction in which KVLis applied (Clock wise Anti clock wise).

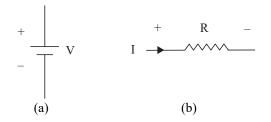

#### • Sign Conventions

#### Figure 1.69

Consider a battery source V as shown in the figure 1.69(a). Here positive of the battery is marked with + sign and negative of the battery is marked with - sign.

When we move from + sign to - sign, it is called voltage drop. When we move from - sign to + sign, it is called as voltage rise. When KVL is applied in Anti clockwise direction as shown above it is called as voltage drop. A voltage drop is indicated in a loop with "—" sign (-V)

For the same battery source if the KVL is applied in clock wise direction we move from - sign to + sign. Hence it is called as Voltage Rise. A Voltage rise indicated in the loop with + sign. (+V).

Similarly in the resistor the current entry point is marked as positive (+ sign) and current leaving point is marked as negative sign. (- sign).

For the resistor shown in the diagram above, if KVL is applied in clock wise direction then it is called as voltage drop. Voltage drop in KVL equation must be indicated with negative sign (-).  $\therefore$  –IR.

For the resistor shown in the diagram above, if KVL is applied in anti clockwise direction then it is called as voltage rise. A voltage rise is indicated in the KVL equation as positive. i.e. + IR.

In short the above explanation is summarized below in a Table.

Sathyabama Institute of Science & Technology

| S.No. | Element | KVL in clockwise     | KVL in anticlockwise                           |

|-------|---------|----------------------|------------------------------------------------|

|       |         | •                    | <b>←</b>                                       |

| 1.    | + _     | + _                  | + _                                            |

|       |         | Drop                 | Rise<br>+V                                     |

| 2.    |         | I + R►<br>Drop<br>IR | ↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓ |

- Procedure for KVL:

- \* Identify the loops and Name them.

- \* Mark the branch currents and name them.

- \* Apply the sign convention.

- \* Select a loop & apply KVL either in clockwise or Anticlockwise and frame the equation.

- \* Solve all the equations of the loop.

# • Problems based on Kirchhoff's laws

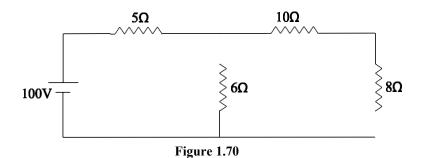

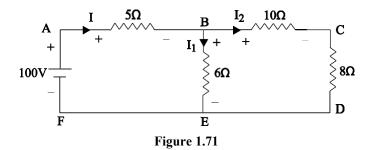

**Problem 1.34** For the given circuit find the branch currents and voltages by applying KVL.

# Solution:

Consider loop ABEF & Apply KVL in CLK wise direction  $100 - 5I - 6I_1 = 0$

But  $I = I_1 + I_2$

$$100 - 5(I_1 + I_2) - 6I_1 = 0$$

$$100 - 5I_1 - 5I_2 - 6I_1 = 0$$

$$-11I_1 - 5I_2 + 100 = 0$$

$$11I_1 + 5I_2 = 100$$

(1)

Consider loop BCDEB & Apply KVL in CLK wise direction

$$-10I_2 - 8I_2 + 6I_1 = 0$$

$$-18I_2 + 6I_1 = 0$$

$$6I_1 = 18I_2$$

$$I_1 = 3I_2$$

(2)

Sub  $I_1$  in equ (1)

$$11 (3 I_2) + 5 I_2 = 100$$

$$33 I_2 + 5 I_2 = 100$$

$$38 I_2 = 100$$

$$I_2 = \frac{100}{38} = 2.63 Amps.$$

$$I_2 = 2.63 \ Amps$$

Sub  $I_2$  in equ (2)

$I_1 = 3(2.63) = 7.89$ Amps  $I_1 = 7.89$ Amps  $I = I_1 + I_2 = 10.52$ I = 10.52Amps.

Voltage Across  $5 \land = 5 \land I = 5 \land 10.52$  = 52.6 voltsVoltage Across  $6 \land = 6 \land I_1 = 6 \land 7.89$  = 47.34 voltsVoltage Across  $10 \land = 10 \land I_2 = 10 \land 2.63$  = 26.3 voltsVoltage Across  $8 \land = 8 \land I_2 = 8 \land 2.63$ = 21.04 volts

## (**O**r)

# The above problem can be solved by applying KVL in Anti clock wise directions.

Consider loop ABEF & Apply KVL in anti clock wise direction

$$6I_1 + 5I - 100 = 0$$

But  $I = I_1 + I_2$

$$6I_1 + 5(I_1 + I_2) -100 = 0$$

$$6I_1 + 5I_1 + 5I_2 = 100$$

$$11I_1 + 5I_2 = 100$$

(3)

Consider loop BCDEB & Apply KVL in anti clockwise direction

$$\begin{aligned} 8I_2 + \ 10I_2 - \ 6I_1 &= 0\\ 18I_2 &= \ 6I_1 \\ I_1 &= \ 3I_2 \end{aligned} \tag{4}$$

equations (3) & (1) are identical

equations (2) & (4) are identical

Hence we get the same answer irrespective of directions of applying KVL.

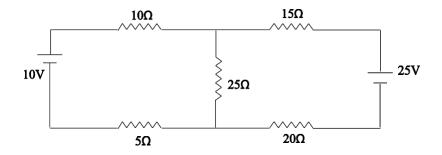

**Problem 1.35** Calculate the branch current in 15  $\Omega$  resistor by Applying kirchhoff's law

Figure 1.72

Figure 72 battery voltage value 25 volt missing

## Solution:

Name the loop and Mark the current directions

## Figure 1.73

Consider the loop ABEFA & apply KVL in CLK wise

$$10 - 10I_1 - 25(I_1 + I_2) - 5I_1 = 0$$

$$10 - 10I_1 - 25I_1 - 25I_2 - 5I_1 = 0$$

$$- 40I_1 - 25I_2 + 10 = 0$$

$$40I_1 + 25I_2 = 10$$

(1)

Consider the loop BCDEB and Apply KVL in CLK wise direction

Consider the loop BCDEB and Apply KVL in CLK wise direction

$$15I_{2} - 25 + 20I_{2} + 25(I_{1} + I_{2}) = 0$$

$$15I_{2} - 25 + 20I_{2} + 25(I_{1} + I_{2}) = 0$$

$$15I_{2} - 25 + 20I_{2} + 25I_{1} + 25I_{2} = 0$$

$$25I_{1} + 60I_{2} - 25 = 0$$

$$25I_{1} + 60I_{2} = 25 \dots(2)$$

Solve (1) & (2) & find I<sub>2</sub> alone (1) × 25  $\Rightarrow$  1000  $I_1$ +625 $I_2$  = 25 (2) × 40  $\Rightarrow$  1000  $I_1$ + 2400 $I_2$ (A) - (B)  $\Rightarrow$  -1775  $I_2$ = -750  $I_2$ = 0.42 Amps. Current in 15  $\Omega$  resistor is 0.42Amps.

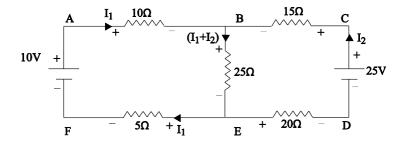

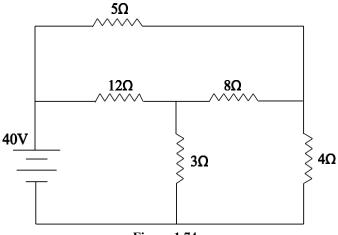

**Problem 1.36** For the given network find the branch current in 8  $\Omega$  and voltage across the 3  $\Omega$  by applying KVL

Figure 1.74

## Solution:

Name the loop and mark the current directions and apply sign convention.

Figure 1.75

Consider loop ABDA and apply KVL

$$-8I_1 + 8$$

$$12I_1 - 3I_2 + 40 = 0$$

$$12I_1 + 3I_2 = 40$$

Consider loop BCDB and apply KVL

$$-8(I_1 - I_2) - 4(I_1 - I_2 + I_3) + 3 I_2 = 0$$

Sathyabama Institute of Science & Technology

$$\begin{array}{c} I_2 - 4I_1 + 4 \ I_2 - 4 \ I_3 + 3 \ I_2 = 0 \\ -12I_1 + 15I_2 - 4I_3 = 0 \end{array} (1) \\ (2). \end{array}$$

Consider loop ABCA and apply KVL

$$-12I_1 - 8(I_1 - I_2) + 5I_3 = 0$$

-12I\_1 - 8I\_1 + 8I\_2 + 5I\_3 = 0

-20I\_1 + 8I\_2 + 5I\_3 = 0 (3)

Solve equ (2) & (3) and cancel out  $I_3$

(2) x 5

$$\Rightarrow$$

-60 I<sub>1</sub>+ 75 I<sub>2</sub> - 20 I<sub>3</sub> = 0

(3) x 4  $\Rightarrow$  -80 I<sub>1</sub>+32 I<sub>2</sub> + 20 I<sub>3</sub> = 0

we equations  $\Rightarrow$  140 I<sub>4</sub> + 107I<sub>5</sub> = 0 (4)

Add the above two equations  $\Rightarrow -140 I_1 + 107I_2 = 0$  (4)

Solve equ (4) & (1) and find  $I_1$  &  $I_2$

$$12I_1 + 3I_2 = 40$$

(1)

-140I\_1 + 107I\_2 = 0 (4)

(1) x 107

$$\Rightarrow$$

1284I<sub>1</sub>+ 321I<sub>2</sub> = 4280

(4) x 3  $\Rightarrow$  - 420I<sub>1</sub>+ 321I<sub>2</sub> = 0

Subtract the above two 1704 I<sub>1</sub> = 4280

$I_1 = 2.51 \text{ Amps}$

Sub  $I_1$  in (4)

$$-140 \times 2.51 + 107I_2 = 0$$

-351.4 + 107I\_2 = 0

107I\_2 = 351.4

$I_2 = 3.28 \text{ Amps}$

Current in 8  $\Omega$  resistor = I<sub>1</sub>- I<sub>2</sub> = 2.51- 3.28 = -0.77 Amps. Negative sign indicates that current flows in the opposite direction of our assumption.

Voltage in 3  $\Omega$  resistor = 3I<sub>2</sub> = 3 × 3.28 = 9.84 volts

Note: Since there are 3 loops three unknown currents  $I_1$ ,  $I_2$  and  $I_3$  should be named in the loop.

**Problem 1.37** For the given network shown below find the branch currents by applying KVL and also find the voltage across 5  $\Omega$  resistor.

Figure 1.76

**Solution:** Name the loop and assume the branch currents.

Figure 1.77

Consider the loop ABDA and apply KVL.

$$-4I_1 - 5 I_3 + I_2 = 0$$

$$-4 I_1 + I_2 - 5 I_3 = 0$$

(1)

Consider the loop BCDB and apply KVL.

$$-3(I_1 - I_3) + 3(I_3 + I_2) + 5I_3 = 0$$

$-3I_1 + 3I_3 + 3I_3 + 3I_2 + 5I_3 = 0$

$-3I_1 + 3I_2 + 11I_3 = 0$  (2)

Consider the loop ADCA and apply KVL.

$$-6(I_1 + I_2) - I_2 - 3(I_3 + I_2) + 50 = 0$$

$$-6I_1 - 6I_2 - I_2 - 3I_3 - 3I_2 = -50$$

$$-6I_1 - 10I_2 - 3I_3 = -50$$

$$6I_1 + 10I_2 + 3I_3 = 50$$

(3)

From eqn is (1) & (2) Cancel  $I_3$

$$4I_1 + I_2 - 5I_3 = 0 \tag{4}$$

$$-3I_1 + 3I_2 + 11I_3 = 0 \tag{5}$$

(4) x 3

$$\Rightarrow -12I_1 + 3I_2 - 15I_3 = 0$$

(5) x 4  $\Rightarrow -12I_1 + 12I_2 - 44I_3 = 0$

By subtracting the above two equations  $-9I_2-59I_3=0$   $9I_2=-59I_3$

$$I_2 = -6.56I_3$$

(6)

-3I\_1+3I\_2 + 11I\_3 = 0 (7)

$$6I_1 + 10I_2 + 3I_3 = 50 \tag{8}$$

(7) x 2

$$\Rightarrow$$

-6I<sub>1</sub>+ 6I<sub>2</sub>+ 22I<sub>3</sub> = 0

(8)  $\Rightarrow$  6I<sub>1</sub>+ 10I<sub>2</sub> + 3I<sub>3</sub> = 50

By adding the above two equations

$$16I_2 + 28I_3 = 50$$

(9)

Sub eqn (6) in (9)

$$16 (-6.56 I_3) + 25 I_3 = 50$$

$-104.96 + 25 I_3 = 50$

$I_3 = -0.625 \text{ Amps}$  (10)

Sub eqn (10) in (6)

$I_2 = -6.56 \text{ x} (-0.625)$

$I_2 = 4.1 \text{ Amps}$  (7)

Sub (10) & (11) in eqn (8)

$6I_1 + 10I_2 + 3I_3 = 50$

$6I_1 + 10 (4.1) + 3 (-0.625) = 50$

$6I_1 = 10.875$

$I_1 = 1.81 \text{ Amps}$

Current in 6  $\Omega$  resistor =  $(I_1 + I_2) = (1.81 + 4.1) = 5.91$  Amps Current in 4  $\Omega$  resistor =  $I_1 = 1.81$  Amps Current in 5  $\Omega$  resistor =  $I_3 = -0.625$  Amps Current in 3  $\Omega$  resistor =  $(I_1 - I_3) = 1.81 + 0.625 = 2.44$  Amps Current in 3  $\Omega$  resistor =  $(I_3+I_2) = 3.475$  Amps Current in 1  $\Omega$  resistor =  $I_2 = 4.1$  Amps.

Voltage Across 5  $\Omega$  resistor= 5 × 0.625 = 3.13 volts.

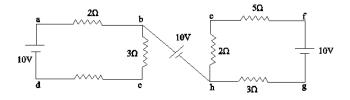

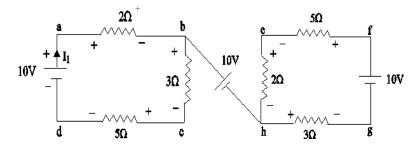

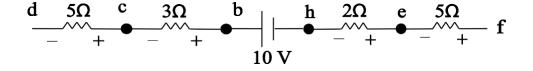

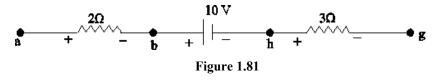

**Problem 1.38** For the Circuit shown below determine voltages (i)  $V_{df}$  and (ii) $V_{ag}$

Figure 1.78

## Solution:

Mark the current directions and mark the polarity

Apply KVL to loop abcda  $10 -2I_1 -3I_1 -5I_1 = 0$   $-10I_1 = -10$  $I_1 = 1$  Amps

Apply KVL to loop efghe  $5I_2 - 10 + 3I_2 + 2I_2 = 0$  $10I_2 = 10$  $I_2 = 1$  Amps

To find  $V_{df}$ : Trace the path  $V_{df}$

Figure 1.80

Sathyabama Institute of Science & Technology

$$V_{df} = -5(I_1 - 3I_1 + 10 + 2I_2 + 5I_2)$$

$$V_{df} = -5 - 3 + 10 + 2 + 5$$

$$V_{df} = 9 \text{ Volts.}$$

$$V_{df} = -9 \text{ Volts [} \therefore \text{ because - sign on d side + on f side]}$$

To find Vag:

Apply KVL to the above Trace  $\begin{array}{c} -2I_1 \text{--}10 - 3I_2 = V_{ag} \\ V_{ag} = -2 - 10 - 3 \\ V_{ag} = -15 \end{array}$

$V_{ag} = 15$  Volts. (With a side + w.r.t g)

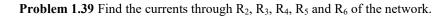

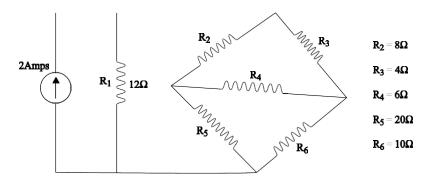

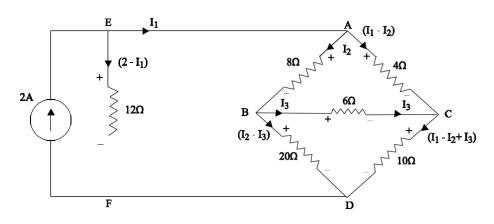

Figure 1.82

| $R_2 = 8 \Omega$    |

|---------------------|

| R <sub>3</sub> =4 Ω |

| R <sub>4</sub> =6 Ω |

| $R_5 = 20 \Omega$   |

| $R_6 = 10 \Omega$   |

## Solution:

Name the circuit and mark the current directions and polarity as shown below

Figure 1.83

Apply KVL to the loop ACBA.

$$\begin{array}{c} -4(I_1-I_2)+6I_3+8I_2=0.\\ -4I_1+4I_2+6I_3+8I_2=0\\ -4I_1+12I_2+6I_3=0 \end{array} \tag{1}$$

Apply KVL to the loop BCDB

$$-6I_3 -10 (I_1 - I_2 + I_3) + 20 (I_2 - I_3) = 0$$

$-6I_3 - 10I_1 + 10I_2 - 10I_3 + 20I_2 - 20I_3 = 0$

$-10I_1 + 30I_2 - 36I_3 = 0$  (2)

Apply KVL to loop EABDFE

$$-8 I_2 - 20 (I_2 - I_3) + 12 (2 - I_1) = 0$$

$$-8 I_2 - 20 I_2 + 20 I_3 + 24 - 12 I_1 = 0$$

$$-28 I_2 + 20 I_3 + 24 - 12 I_1 = 0$$

$$-12 I_1 - 28 I_2 + 20 I_3 = -24$$

$$12 I_1 + 28 I_2 - 20 I_3 = 24$$

(3)

Solving equ. (1) (2) & (3). We get  $I_1 = 1.125$  Amps  $I_2 = 0.375$  Amps  $I_3 = 0$  Amps

$\begin{array}{l} \ddots \ \mbox{Current in } R_2 = 0.375 \ \mbox{Amps} \\ R_3 = 0.75 \ \mbox{Amps} \\ R_4 = 0 \ \mbox{Amps} \\ R_5 = 0.375 \ \mbox{Amps} \\ R_6 = 0.75 \ \mbox{Amps} \\ \end{array}$

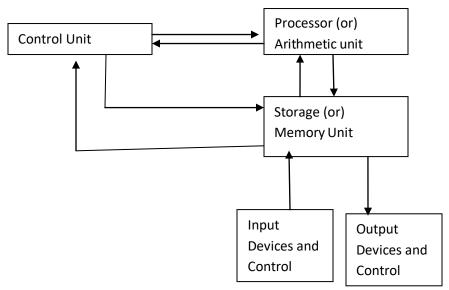

# NODAL ANALYSIS

- In nodal analysis, node equations relating node voltages are obtained for a multi node network.

- These node voltages are derived from kirchoff's current law (KCL)

- In this method the number of equations required to be solved is N-1, where N is the number of nodes.

- A node is a junction in a network where three or more branchesmeet. One of the nodes in a network is regarded as reference (datum) node and the potential of the other nodes are defined with reference to the datum node.

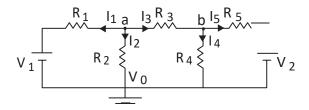

#### Case I.

Consider figure 1 Let the voltages at nodes a and b be  $V_a$  and  $V_b$ . Applying Kirchoff's current law (KCL) at node 'a' we get

#### Figure 1.84

Where

$$I_1 + I_2 + I_3 = 0$$

(1)

$I_1 = \frac{V_a - V_1}{R_a}; I_2 = \frac{V_a - V_0}{R_a}; I_3 = \frac{V_a - V_b}{R_a};$

Substituting in equ. (1)

$$\frac{V_a - V_1}{R_1} + \frac{V_a - V_0}{R_2} + \frac{V_a - V_b}{R_3} = 0$$

On simplifying  $[V_0 = 0]$

Similarly for node b we have

$$I_{4} + I_{5} = I_{3} \dots (3)$$

$$I_{4} = \frac{V_{b} - V_{o}}{R_{4}}; I_{5} = \frac{V_{b} - V_{2}}{R_{5}}$$

On substituting in equ (3)

$$\frac{V_{b}-V_{o}}{R_{4}}+\frac{V_{b}-V_{2}}{R_{5}}=\frac{V_{a}+V_{b}}{R_{3}}$$

$$h$$

$$y$$

S

а

а b а т

а

r S i

t y

$\underline{\mathbf{V}}_{0} = 0$  [reference node]

$$V_{b}\left[\frac{1}{R_{3}} + \frac{1}{R_{4}} + \frac{1}{R_{5}}\right] - V_{a}\left[\frac{1}{R_{3}}\right] = \frac{V_{2}}{R_{5}} \dots \dots \dots (4) \qquad \qquad \begin{matrix} U \\ n \\ i \end{matrix}$$

Solving equations (2) and (4) we get the values as  $\underbrace{V_{a}}_{e}$  and  $\underbrace{V_{b}}_{e}$ .

Method for solving Va and Vb by Cramers rule.

$$\begin{pmatrix} \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3} & -\frac{1}{R_3} \\ -\frac{1}{R_3} & \frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5} \end{pmatrix} \begin{bmatrix} V_a \\ V_b \end{bmatrix} = \begin{bmatrix} \frac{V_1}{R_1} \\ \frac{V_2}{R_2} \end{bmatrix}$$

$$\Delta = \begin{pmatrix} \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3} \end{pmatrix} \begin{pmatrix} \frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5} \end{pmatrix} - \begin{pmatrix} -\frac{1}{R_3} \end{pmatrix} \begin{pmatrix} -\frac{1}{R_3} \end{pmatrix} \begin{pmatrix} -\frac{1}{R_3} \end{pmatrix}$$

To find  $\Delta_1$

$$\begin{pmatrix} \frac{V_1}{R_1} & \frac{-1}{R_3} \\ \frac{V_2}{R_5} & \frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5} \end{pmatrix}$$

$$\Delta_1 = \left(\frac{V_1}{R_1}\right) \left(\frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5}\right) - \left(\frac{-1}{R_3}\right) \left(\frac{V_2}{R_5}\right)$$

To find  $\Delta_2$ ,

$$\begin{pmatrix} \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3} & \frac{V_1}{R_1} \\ \frac{-1}{R_3} & \frac{V_2}{R_5} \end{pmatrix}$$

$$\Delta_2 = \left(\frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}\right) \left(\frac{V_2}{R_5}\right) - \left(\frac{-1}{R_3}\right) \left(\frac{V_1}{R_1}\right)$$

To find y<sub>a</sub>:

To find vb:

$$V_a = \frac{\Delta_1}{\Delta};$$

$V_b = \frac{\Delta_2}{\Delta}$

Hence  $\underline{V}_{a}$  and  $\underline{V}_{b}$  are found.

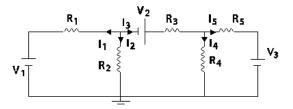

CASE II:

Consider fig 2

Let the voltages at nodes a and b be  $\underbrace{V_{a}}_{a} and \ V_{b.}$

The node equation at node a are

$$I_1 + I_2 + I_3 = 0$$

Where

$$I_1 = \frac{V_a - V_1}{R_1}$$

;  $I_2 = \frac{V_a}{R_2}$ ;  $I_3 = \frac{V_a + V_2 - V_b}{R_3}$

$$\frac{V_a - V_1}{R_1} + \frac{V_a}{R_2} + \frac{V_a + V_2 - V_b}{R_3} = 0$$

Simplifying

$$\frac{V_a}{R_1} - \frac{V_1}{R_1} + \frac{V_a}{R_2} + \frac{V_a}{R_3} + \frac{V_2}{R_3} - \frac{V_b}{R_3} = 0$$

Combining the common terms.

The nodal equations at node b are

$$I_3 = I_4 + I_5$$

$$\frac{V_a + V_2 - V_b}{R_3} = \frac{V_b}{R_4} + \frac{V_b - V_3}{R_5}$$

On simplifying

$$\frac{V_a}{R_3} + \frac{V_2}{R_3} - \frac{V_b}{R_3} = \frac{V_b}{R_4} + \frac{V_b}{R_5} - \frac{V_3}{R_5}$$

$$\frac{V_a}{R_3} - V_b \left[ \frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5} \right] = -\frac{V_3}{R_5} - \frac{V_2}{R_3}$$

$$-\frac{V_a}{R_3} + V_b \left[ \frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5} \right] = \frac{V_3}{R_5} + \frac{V_2}{R_3}$$

(6)

Solving equ (5) and (6) we get  $\underline{V}_{a}$  and  $\underline{V}_{b}$

#### Method to solve $\underline{\mathbf{V}}_{a}$ and $\mathbf{V}_{b}$ .

Solve by cramers rule.

$$\begin{pmatrix} \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3} & \frac{-1}{R_3} \\ \frac{-1}{R_3} & \frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5} \end{pmatrix} \begin{bmatrix} V_a \\ V_b \end{bmatrix} = \begin{bmatrix} \frac{V_1}{R_1} - \frac{V_2}{R_3} \\ \frac{V_2}{R_3} + \frac{V_3}{R_5} \end{bmatrix}$$

$$\Delta = \left(\frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}\right) \left(\frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5}\right) - \left(-\frac{1}{R_3}\right) \left(-\frac{1}{R_3}\right)$$

$$\Delta_1 = \begin{pmatrix} \frac{V_1}{R_1} - \frac{V_2}{R_3} & -\frac{1}{R_3} \\ \frac{V_2}{R_3} + \frac{V_3}{R_5} & \frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5} \end{pmatrix}$$

$$\left(\frac{V_1}{R_1} - \frac{V_2}{R_3}\right) \left(\frac{1}{R_3} + \frac{1}{R_4} + \frac{1}{R_5}\right) - \left(-\frac{1}{R_3}\right) \left(\frac{V_2}{R_3} + \frac{V_3}{R_5} - \frac{V_3}{R_5}\right)$$

$$\Delta_{2} = \begin{pmatrix} \frac{1}{R_{1}} + \frac{1}{R_{2}} + \frac{1}{R_{3}} & \frac{V_{1}}{R_{1}} - \frac{V_{2}}{R_{3}} \\ \frac{-1}{R_{3}} & \frac{V_{2}}{R_{3}} + \frac{V_{3}}{R_{5}} \end{pmatrix}$$

$$\Delta_{2} = \begin{pmatrix} \frac{1}{R_{1}} + \frac{1}{R_{2}} + \frac{1}{R_{3}} \end{pmatrix} \begin{pmatrix} \frac{V_{2}}{R_{3}} + \frac{V_{3}}{R_{5}} \end{pmatrix} - \begin{pmatrix} -\frac{1}{R_{3}} \end{pmatrix} \begin{pmatrix} \frac{V_{1}}{R_{1}} - \frac{V_{2}}{R_{3}} \end{pmatrix}$$

$$\Delta_{a} = \frac{\Delta_{1}}{\Delta}; \qquad \Delta_{b} = \frac{\Delta_{2}}{\Delta}$$

Hence  $\underline{V}_{a}$  and  $\underline{V}_{b}$  are found.

(case iii)

Let the voltages at nodes a and b be  $\underbrace{V_a}_{a}$  and  $\underbrace{V_b}_{b}$  as shown in fig

Node equations at node <u>a</u> are

Similarly Node equations at node b

$$I_3 + I_5 = I_4$$

Solving eqn (7) and (8)

Va and Vb has been found successfully.

#### Problems

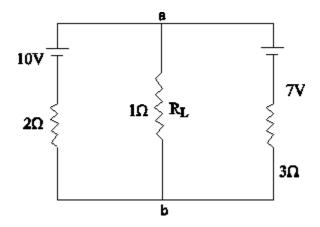

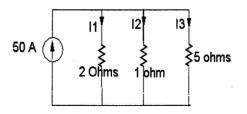

1) Two batteries having emf of 10V and 7V and internal resistances of 2 $\Omega$  and 3 $\Omega$  respectively,

are connected in parallel across a load of resistance  $1\Omega$ . Calculate

(i) The individual battery currents

(ii) The current through the load

(iii) The Voltage across the load

## Solution:

Step 1) Select the nodes and mark the nodes

Step 2) Select the datum or reference node.

<fig 84>

$\underline{b}$  is the ground node  $\underline{V}_{\underline{b}} = 0$

Step 3: Mark the currents  $I_{1,a} I_2 \& I_3$

Step 4: Write the node equations for node a and solve for Va.

$I_{1} + I_{2} + I_{3} = 0 \dots (1)$   $I_{1} = \frac{V_{a} - 10}{2} \dots (2)$   $I_{2} = \frac{V_{a}}{1} \dots (3)$

Substituting (2), (3) & (4) in (1)

$$\frac{V_a - 10}{2} + V_a + \frac{V_a - 7}{3} = 0$$

$$V_a \left[ \frac{1}{2} + 1 + \frac{1}{3} \right] = \frac{10}{2} + \frac{7}{3}$$

$$1.83 \ V_a = 7.33$$

$$V_a = 4 \ V$$

/

(i) Individual battery currents

$$I_{1} = \frac{V_{a} - 10}{2} = \frac{4 - 10}{2}$$

$$= -3A$$

Ans: I<sub>1</sub>=3 A

$$I_{3} = \frac{V_{a} - 7}{3} = \frac{4 - 7}{3} = -1$$

Ans: I<sub>3</sub> = 1A

(ii) Current through the load

$$I_L = I_{1-2} = \frac{V_a}{1} = 4A$$

(iii)Voltage across the load

$$V_L = V_a - V_b$$

$$= 4 - 0$$

$$V_L = 4 V$$

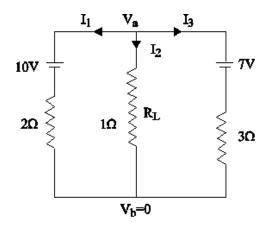

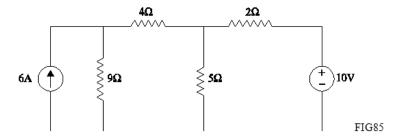

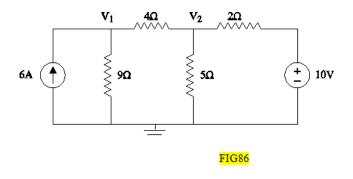

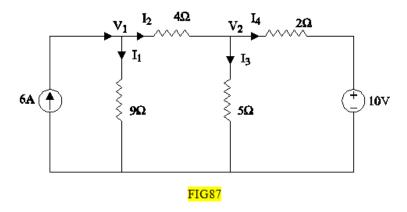

2) Write the node voltage equation and calculate the currents in each branch for the network.

Step 1: To assign voltages at each node

$V_1 \& V_2$  are active nodes  $V_3$  is a reference node on datum node. Hence  $V_3 = 0$ .

Step 2: Mark the current directions in all the branches.

Step 3: Write the node equations for node (1) and (2)

Node 1

$$I_{1} + I_{2} = 6$$

$$\frac{v_{1}}{9} + \frac{v_{1} - v_{2}}{4} = 6$$

$$V_{1} \left[ \frac{1}{9} + \frac{1}{4} \right] - V_{2} \left[ \frac{1}{4} \right] = 6 \dots (1)$$

Node 2:

$$I_2 = I_3 + I_4$$

$$\frac{V_1 - V_2}{4} = \frac{V_2}{5} + \frac{V_2 - 10}{2}$$

$$V_1 \left[ \frac{1}{4} \right] = V_2 \left[ \frac{1}{4} + \frac{1}{5} + \frac{1}{2} \right] - \frac{10}{2}$$

$$-V_1 \left[ \frac{1}{4} \right] + V_2 \left[ \frac{1}{4} + \frac{1}{5} + \frac{1}{2} \right] = \frac{10}{2} \qquad (2)$$

Step 4: Solving equ (1) and (2) and finding  $V_1$  and  $V_2$  by Cramers rule,

$$\begin{bmatrix} \frac{1}{9}, \frac{1}{4} & -\frac{1}{4} \\ -\frac{1}{4} & \frac{1}{5}, \frac{1}{4}, \frac{1}{2} \\ -\frac{1}{2} & \frac{1}{5}, \frac{1}{4}, \frac{1}{2} \end{bmatrix} \begin{bmatrix} \frac{V_1}{V_2} \end{bmatrix} = \begin{bmatrix} \frac{6}{5} \end{bmatrix}$$

$$\begin{pmatrix} .36 & -.25 \\ -.25 & .95 \end{pmatrix} \begin{bmatrix} \frac{V_1}{V_2} \end{bmatrix} = \begin{bmatrix} \frac{6}{5} \end{bmatrix}$$

$\Delta=0.2795$

To find  $\Delta_1$

$$\begin{pmatrix} 6 & -.25 \\ 5 & .95 \end{pmatrix} = 6.95$$

$V_1 = \frac{6.95}{.279} = 24.86\upsilon$

To find  $\Delta_2$

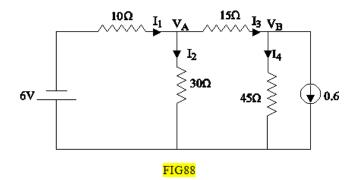

Hence currents in all the branches are found. **Problem 1.42** Use the Nodal Method to find  $V_{ba}$  and current through 30  $\Omega$

resistor in the circuit shown

At node A

$$\frac{V_A + 6}{10} + \frac{V_A}{30} + \frac{V_A - V_B}{15} = 0$$

$$V_A \left[ \frac{1}{10} + \frac{1}{30} + \frac{1}{15} \right] - \frac{V_B}{15} = -0.6$$

At node B

$$\begin{split} \frac{V_B - V_A}{15} + \frac{V_B}{45} & \pm 0.6 = 0 \\ V_B \left[ \frac{1}{15} + \frac{1}{45} \right] - \frac{V_A}{15} & = -0.6 \\ \left( \frac{1}{10} + \frac{1}{30} + \frac{1}{15} - \frac{1}{15} \right) \\ - \frac{1}{15} & \frac{1}{15} + \frac{1}{45} \right) \left[ \frac{V_A}{V_B} \right] = \begin{bmatrix} -0.6 \\ -0.6 \end{bmatrix} \\ \Delta &= \begin{bmatrix} 0.2 & -0.066 \\ -0.066 & 0.088 \end{bmatrix} = \begin{bmatrix} 0.0176 - 4.35 \times 10^{-3} \end{bmatrix} \\ \Delta &= \begin{bmatrix} 0.01324 \end{bmatrix} \\ \Delta &= 0.01324 \\ \Delta_1 &= \begin{bmatrix} -0.6 & -\frac{1}{15} \\ -0.6 & \frac{1}{15} + \frac{1}{45} \end{bmatrix} = -0.093 \\ \Delta_1 &= \begin{bmatrix} -0.053 - 0.04 \end{bmatrix} = -0.093 \\ V_A &= \frac{\Delta_1}{\Delta} = -\frac{0.093}{0.01324} = -7.02V \\ \Delta_2 &= \begin{bmatrix} 0.2 & -0.6 \\ -0.066 & -0.6 \end{bmatrix} \\ \Delta_2 &= (-0.12 - 0.0396] \\ \Delta_2 &= -0.1596 \\ V_2 &= \frac{\Delta_2}{\Delta} = \frac{-0.1596}{0.01324} = -12.05V \\ V_{5a} &= V_A - V_B = -7 + 12 = 5V \end{split}$$

$$I_2 = \frac{V_A}{30} = \frac{-7}{30} = -0.233A$$

$$I_2 = -0.233A$$

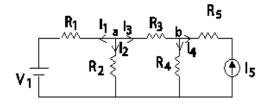

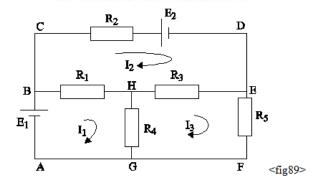

#### Maxwell's Mesh method (Loop method).

This method was first proposed by Maxwell simplifies the solution of several networks. In this method, KVL is used. In any network, the number of independent loop equations will be

$$m = l - (j - 1)$$

Where 1 is the number of branches and j is the number of junctions.

Let us consider the circuit shown in fig(). for writing the mesh equations. It has

Number of junctions = 4 (B, H, E, G).

Number of branches = 6 (AB, BC, CD, DE, EF, HG).

In the above figure we shall name the three loop currents  $I_{1,l_{n}}$  I<sub>2</sub> and I<sub>3</sub>. The directions of the loop current are arbitrarily chosen. Note that the actual current flowing through R<sub>4</sub> is (I<sub>1</sub>- I<sub>3</sub>) in a downward direction and R<sub>1</sub> is (I<sub>1</sub>- I<sub>2</sub>) from left to Right

Apply KVL for the first loop ABHGA,

$$E_1 - R_1 (I_1 - I_2) - R_4 (I_1 - I_3) = 0$$

Apply KVL for the loop BEDC,

$$-R_{2} I_{2} - E_{2} - R_{3} (I_{2} - I_{3}) - R_{1} (I_{2} - I_{1}) = 0$$

$$R_{2} I_{2, \dots} + R_{3} (I_{2} - I_{3}) + R_{1} (I_{2} - I_{1}) = -E_{2}$$

$$\therefore - R_{1} I_{1} + (R_{1} + R_{2} + R_{3}) I_{2} - R_{3} I_{3} = -E_{2} \dots \dots (2)$$

$$\begin{bmatrix} R_{11} & R_{12} & R_{13} \\ R_{21} & R_{22} & R_{23} \\ R_{31} & R_{32} & R_{33} \end{bmatrix} \begin{bmatrix} I_{1} \\ I_{2} \\ I_{3} \end{bmatrix} = \begin{bmatrix} E_{1} \\ E_{2} \\ E_{3} \end{bmatrix} \dots \dots (5)$$

It can be seen that the diagonal elements of the matrix is the sum of the resistances of the mesh, where as the off diagonal <u>elements</u> are the negative of the sum of the resistance common to the loop.

Thus,

$R_{ii}$  = the sum of the resistances of loop i.

$R_{ij} = \begin{cases} -\sum (\text{Resistance common to the loop i and loop j,} \\ \text{if } I_i \text{ and } I_j \text{ are in opposite direction in common resistances}) \\ +\sum (\text{Resistance common to the loop i and loop j,} \\ \text{if } I_i \text{ and } I_i \text{ are in same direction in common resistances}) \end{cases}$

The above equation is only true when all the mesh currents are taken in clockwise direction. The sign of voltage vector is decided by the considered current direction. If the mesh current is entering into the positive terminal of the voltage source, the direction of voltage vector elements will be negative otherwise it will be positive.

Equation (5) can be solved by Cramer's rule as

$$\Delta_{1} = \begin{bmatrix} E_{1} & R_{12} & R_{13} \\ E_{2} & R_{22} & R_{23} \\ E_{3} & R_{32} & R_{33} \end{bmatrix}; \qquad \Delta_{2} = \begin{bmatrix} R_{11} & E_{1} & R_{13} \\ R_{21} & E_{2} & R_{23} \\ R_{31} & E_{3} & R_{33} \end{bmatrix};$$

$$\Delta_{3} = \begin{bmatrix} R_{11} & R_{12} & E_{1} \\ R_{21} & R_{22} & E_{2} \\ R_{31} & R_{32} & E_{3} \end{bmatrix}; \qquad \Delta = \begin{bmatrix} R_{11} & R_{12} & R_{13} \\ R_{21} & R_{22} & R_{23} \\ R_{31} & R_{32} & R_{33} \end{bmatrix};$$

$$I_{1} = \frac{\Delta_{1}}{\Delta}; \qquad I_{2} = \frac{\Delta_{2}}{\Delta}; \qquad I_{3} = \frac{\Delta_{3}}{\Delta}$$

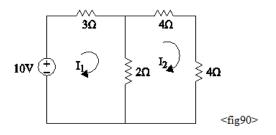

#### Problems:

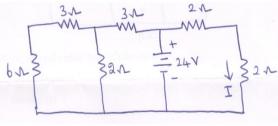

1) Find the branch currents of fig () using Mesh current method

Solution:

Method 1:

Apply KVL for the first loop,

$10 - 3I_1 - 2(I_1 - I_2) = 0$  $5I_1 - 2I_2 = 10$  .....(1)

Apply KVL for the second loop,

$-4I_2 - 4I_2 - 2(I_2 - I_1) = 0$  $-2I_1 + 10I_2 = 10$ (2)

Solve eqn (1) & (2), we get

(1) X 5  $\Rightarrow$  25I<sub>1</sub> - 10I<sub>2</sub> = 50 .....(3)

$(2) \implies -2I_1 + 10I_2 = 0$

$(3) + (2) \Rightarrow \qquad 23 I_1 = 50$

$$I_1 = \frac{50}{23} = 2.174 \text{ A}$$

Sub  $I_1$  in (2)

$$I_{2} = \frac{2 \times 2.174}{10} = 0.435 \text{ A}$$

$$I_{3}\Omega = 2.174 \text{ A}$$

$$I_{2}\Omega = I_{1} - I_{2} = 1.739 \text{ A}$$

$$I_{4}\Omega = 0.435 \text{ A}$$

Method 2:

$R_{11}$  = Sum of resistances of loop 1 = 3+2 =5 $\Omega$

$R_{12}$  = - (common resistance between loop 1 and loop 2) = -2 $\Omega$

$= R_{21}$

$R_{22} = Sum \text{ of resistance is loop } 2 = 4 + 4 + 2 = 10$

E2 = 0  $\begin{bmatrix} 5 & -2 \\ -2 & 10 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} 10 \\ 0 \end{bmatrix}$   $\Delta = \begin{vmatrix} 5 & -2 \\ -2 & 10 \end{vmatrix} = 50 - 4 = 46$   $\Delta_1 = \begin{vmatrix} 10 & -2 \\ 0 & 10 \end{vmatrix} = 100$   $\Delta_2 = \begin{vmatrix} 5 & 10 \\ -2 & 0 \end{vmatrix} = 20$   $\Delta = 100$

$$I_1 = \frac{\Delta_1}{\Delta} = \frac{100}{46} = 2.174A$$

$$I_2 = \frac{\Delta_2}{\Delta} = \frac{20}{46} = 0.435A$$

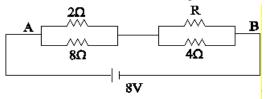

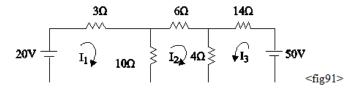

2) Find the loop currents for the network shown in figure below by using Loop Analysis.

Solution

For loop 1,

$3I_1 + 10(I_1 - I_2) = 20$

$13I_1 - 10I_2 = 20$  .....(1)

For loop 2,

$$10(I_2 - I_1) + 6I_2 + 4(I_2 + I_3) = 0$$

$$10I_2 - 10I_1 + 6I_2 + 4I_2 + 4I_3 = 0$$

$$\div 2 \implies -5I_1 + 10I_2 + 2I_3 = 0 \dots \dots (2)$$

For loop 3,

$$4(I_3 + I_2) + 14I_3 = 50$$

$$4I_2 + 18I_3 = 50$$

$$2 \Rightarrow 2I_2 + 9I_3 = 25 \dots (3)$$

$$\begin{bmatrix} 13 & -10 & 0 \\ -5 & 10 & 2 \\ 0 & 2 & 9 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \\ I_3 \end{bmatrix} = \begin{bmatrix} 20 \\ 0 \\ 25 \end{bmatrix}$$

$$\Delta = \begin{vmatrix} 13 & -10 & 0 \\ -5 & 10 & 2 \\ 0 & 2 & 9 \end{vmatrix}$$

$$\Delta = 13(90 - 4) + 10(-45 - 0)$$

$$= 668$$

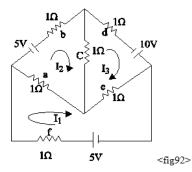

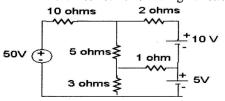

For loop 1,

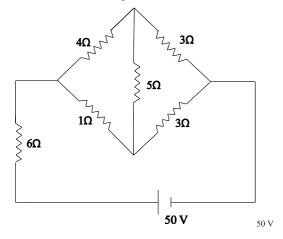

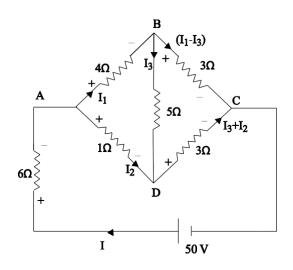

$$10I_1 + 5(I_1 + I_2) + 3(I_1 - I_3) = 50$$

$$18I_1 + 5I_2 - 3I_3 = 50$$

(1)

For loop 2,

$$2I_2 + 5(I_2 + I_1) + 1(I_2 + I_3) = 10$$

$$5I_1 + 8I_2 + I_3 = 10$$

.....(2)

For loop 3,

$$3(I_3 - I_1) + 1(I_3 + I_{2,\lambda}) = -5$$

$$-3I_1 + I_2 + 4I_3 = -5 \dots (3)$$

$$\begin{bmatrix} 18 & 5 & -3 \\ 5 & 8 & 1 \\ -3 & 1 & 4 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \\ I_3 \end{bmatrix} = \begin{bmatrix} 50 \\ 10 \\ -5 \end{bmatrix}$$

$$-12 (250) + 10 (-125) + 20 (-10)$$

$$\Delta = \begin{bmatrix} 18 & 5 & -3 \\ 5 & 8 & 1 \\ -3 & 1 & 4 \end{bmatrix}$$

$$= 18 (32 - 1) - 5 (20 + 3) - 3(5 + 24)$$

$$= 356$$

$$\Delta_3 = \begin{vmatrix} 18 & 5 & 50 \\ 5 & 8 & 10 \\ -3 & 1 & -5 \end{vmatrix}$$

$$= 18 (-40 - 10) - 5 (-25 + 30) + 50(5 + 24)$$

$$= -900 - 25 + 1450$$

$$= 525$$

$$I_3 = \frac{\Delta I_3}{\Delta} = \frac{525}{356} = 1.47.4$$

Solution

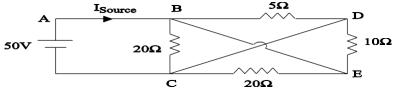

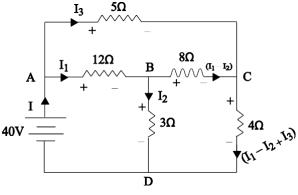

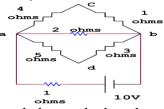

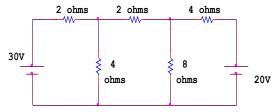

4) Determine the currents in various elements of the bridge circuit as shown below.

Solution

For loop 1,

$$1I_1 + 1(I_1 - I_2) + 1(I_1 - I_3) = 5$$

$3I_1 - I_2 - I_3 = 5$  .....(1)

For loop 2,

$$1I_2 + 1(I_2 - I_3) + 1(I_2 - I_1) = 5$$

- $I_1 + 3I_2 - I_3 = 5$ .....(2)

For loop 3,