# SCHOOL OF ELECTRICAL AND ELECTRONICS

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

# **UNIT – I – DIGITAL DESIGN USING VERILOG HDL– SECA3021**

# UNIT-I (DIGITAL DESIGN USING VERILOG HDL)

Hardware modeling with the Verilog HDL: Encapsulation, modeling primitives, Types of Modelling. Logic system, Data types and operators. Behavioral descriptions in verilog HDL. Styles for Synthesis of combinational logic and sequential logic. HDL based Synthesis – Technology Independent design

Verilog HDL is a hardware description language that can be used to model a digital system at many levels of abstraction ranging from the algorithmic level to the gate level to the switch level. The complexity of the digital system being modeled could vary from that of a simple gate to a complete electronic digital system, or anything in between. The digital system can be described hierarchically and timing can be explicitly modeled within the same description.

## 1.1 Typical Design Flow

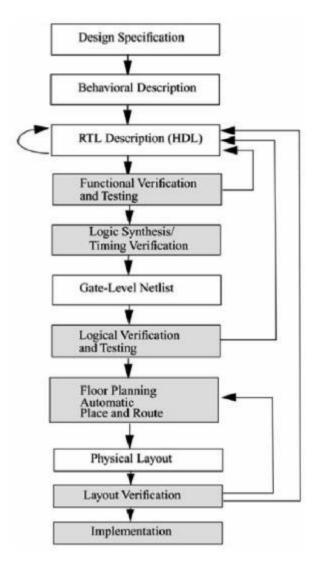

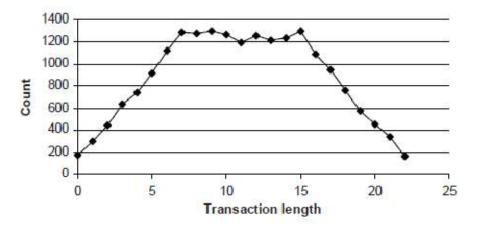

A typical design flow for designing VLSI IC circuits is shown in Figure 2.1. Un shaded blocks show the level of design representation; shaded blocks show processes in the design flow.

The design flow shown in Figure 1.1 is typically used by designers who use HDLs. In any design, specifications are written first. Specifications describe abstractly the functionality, interface, and overall architecture of the digital circuit to be designed. At this point, the architects do not need to think about how they will implement this circuit. A behavioral description is then created to analyze the design in terms of functionality, performance, compliance to standards, and other high-level issues. Behavioral descriptions are often written with HDLs

The behavioral description is manually converted to an RTL description in an HDL. The designer has to describe the data flow that will implement the desired digital circuit. From this point onward, the design process is done with the assistance of EDA tools.

Logic synthesis tools convert the RTL description to a gate-level netlist. A gatelevel netlist is a description of the circuit in terms of gates and connections between them. Logic synthesis tools ensure that the gate-level netlist meets timing, area, and power specifications. The gatelevel netlist is input to an Automatic Place and Route tool, which creates a layout. The layout is verified and then fabricated on a chip.

Figure 1.1: Typical Design Flow

# **1.2 Design Methodologies**

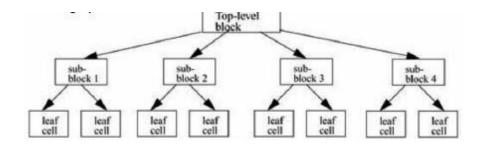

There are two basic types of digital design methodologies: a top-down design methodology and a bottom-up design methodology. In a top-down design methodology, we define the top-level block and identify the sub-blocks necessary to build the top-level block. We further subdivide the sub-blocks until we come to leaf cells, which are the cells that cannot further be divided. Figure 1.2 shows the top-down design process.

Figure 1.2: Top-down Design Methodology

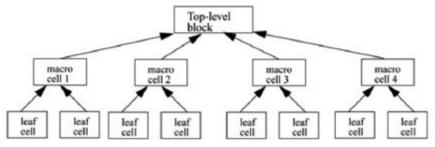

In a bottom-up design methodology, we first identify the building blocks that are available to us. We build bigger cells, using these building blocks. These cells are then used for higher-level blocks until we build the top-level block in the design. Figure 1.3 shows the bottom-up design process

Figure 1.3: Bottom-up Design Methodology

# 1.2.1 Levels for design description

Verilog supports designing at many different levels of abstraction. Three of them are veryimportant:

- Behavioral level

- Register-Transfer LevelGate Level

**Behavioral Level:** This level describes a system by concurrent algorithms (Behavioral). Each algorithm itself is sequential, that means it consists of a set of instructions that are executed one after the other. Functions, Tasks and Always blocks are the main elements. There is no regard to the structural realization of the design.

**Register-Transfer Level:** Designs using the Register-Transfer Level specify the characteristics of a circuit by operations and the transfer of data between the registers. An explicit clock is used. RTL design contains exact timing bounds: operations are scheduled to occur at certain times. Modern RTL code definition is "Any code that is synthesizable is called RTL code".

**Gate Level:** Within the logic level the characteristics of a system are described by logical links and their timing properties. All signals are discrete signals. They can only have definite logical values ('0', `1', `X', `Z`). The usable operations are predefined logic primitives (AND, OR, NOT etc gates). Using gate level modeling might not be a good idea for any level of logic design. Gate level code is generated by tools like synthesis tools and this netlist is used for gate level simulation and for backend.

# 1.3 Data types

Verilog HDL has two groups of data types a) Net type: A net type represents a physical connection between structural elements. Its value is determined from the value of its drivers such as a continuous assignment or a gate output. If no driver is connected to a net, the net defaults to a value of z. b)Variable type: A variable type represents an abstract data storage element. It is assigned values only within an always statement or an initial statement, and its value is saved from one assignment to the next. A variable type has a default value of x.

Net types

Here are the different kinds of nets that belong to the net data type

wire, tri, wor, trior, wand, triand, trieg, tri1 tri0, supply0, supply1

# **1.3.1 Variable types:**

There are five different kinds of variable types reg, integer, time, real, realtime

**Register:** Registers represent data storage elements. Registers retain value until another value is placed onto them. Register data types are commonly declared by the keyword reg. The default value for a reg data type is x.

**Integer:** An integer is a general purpose register data type used for manipulating quantities. Integers are declared by the keyword integer. Although it is possible to use reg as a general-purpose variable, it is more convenient to declare an integer variable for purposes such as counting. The default width for an integer is the host-machine word size, which is implementation- specific but is at least 32 bits. Registers declared as data type reg store values as unsigned quantities, whereas integers store values as signed quantities.

**Real:** Real number constants and real register data types are declared with the keyword real. They can be specified in decimal notation (e.g., 3.14) or in scientific notation (e.g., 3e6, which is  $3 \times 106$ ). Real numbers cannot have a range declaration, and their default value is 0. When a realvalue is assigned to an integer, the real number is rounded off to the nearest integer.

**Time:** Verilog simulation is done with respect to simulation time. A special time register data type is used in Verilog to store simulation time. A time variable is declared with the keyword time. The width for time register data types is implementation specific but is at

least 64 bits. The system function \$time is invoked to get the current simulation time.

**Arrays:** Arrays are allowed in Verilog for reg, integer, time, real, realtime and vector register data types. Multi-dimensional arrays can also be declared with any number of dimensions. Arrays of nets can also be used to connect ports of generated instances. Each element of the array canbe used in the same fashion as a scalar or vector net.

# **1.4 Styles of Modelling:**

**1.4.1 Gate Level Modelling:** The Built-in Primitive Gates: The following built-in primitive gates are available in Verilog HDL.

- i. Multiple-input gates: and, nand, or,nor,xor,xnor

- ii. Multiple-output gates: buf, not

- iii. Tristate gates: buflfO, bufifl, notifO, notifl

- iv. Pull gates: pullup, pulldown Multiple-input

- v. MOS switches: cmos, nmos, pmos, rcmos, rnmos, rpmos

- vi. Bidirectional switches: tran, tranifO, tranifl, rtran, rtranifO, rtranifl

A gate can be used in a design using a gate instantiation. Here is a simple format of a gate instantiation. gate\_type[ instance\_name ] ( terml , term2 , . . . , termN);

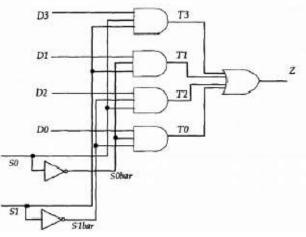

Example: 4x1 Multiplexer:

**Figure 1.4 Multiplexer**

moduleMUX4x1 (Z, DO, Dl, D2, D3, SO, Si); output Z; 10 input DO, Dl, D2, D3, SO, SI; and (TO, DO, SObar, Slbar), (Tl, Dl, SObar, S1), (T2, D2, SO, Slbar), (T3, D3, SO, S1); not (SObar,SO), (Slbar, S1); or (Z, TO, Tl, T2, T3); endmodule

# 1.4.2 Dataflow Modeling

For small circuits, the gate-level modeling approach works very well because the numbers of gates is limited and the designer can instantiate and connect every gate individually. Also, gate-level modeling is very intuitive to a designer with a basic knowledge of digital logic design. However, in complex designs the number of gates is very large. Thus, designers can design more effectively if they concentrate on implementing the function at a level of abstraction higher than gate level. Dataflow modeling provides a powerful way to implement a design. Verilog allows a circuit to be designed in terms of the data flow between registers and how a design processes data rather than instantiation of individual gates. Later in this chapter, the benefits of dataflow modeling will become more apparent. With gate densities on chips increasing rapidly, dataflow modeling has assumed great importance. No longer can companies devote engineering resources to handcrafting entire designs with gates. Currently, automated tools are used to create a gate-level circuit from a dataflow design description. This process is called logic synthesis. Dataflow modeling has become a popular design approach as logic synthesis tools have become sophisticated. This approach allows the designer to concentrate on optimizing the circuit in terms of data flow. For maximum flexibility in the design process, designers typically use a Verilog description style that combines the concepts of gate-level, data flow, and behavioral design. In the digital design community, the term RTL (Register Transfer Level) design is commonly used for a combination of dataflow modeling and behavioral modeling.

# **Example:**

```

Master Slave Flip-flop:

module MSDFF DF (D, C, Q, Qbar);

input D, C;

output Q, Qbar;

wireNotC, NotD, NotY, Y, Dl, D2, Ybar, Yl, Y2;

assignNotD = \sim D;

assign Note = \sim C;

assign NotY = \sim Y;

assign D1 = -(D \& C);

assign D2 = \sim (C \& NotD);

assign Y = \sim (Dl St Ybar);

assign Ybar = \sim (Y & D2);

assign Yl = \sim (y \& Note);

assign Y2 = - (NotY&NotC);

assign Q = \sim (Qbar&Yl);

assignQbar = \sim (Y2 & Q);

endmodule

```

# 8 bit Magnitude Comparator:

moduleMagnitudeComparator (A, B, AgtB, AeqB, AltB);

parameter BUS= 8;

parameter EQ\_DELAY = 5, LT\_DELAY = 8, GT\_DELAY = 8;

input [1 : BUS]A, B;

outputAgtB, AeqB, AltB;

assign %EQ\_DELAY AeqB = A == B; 19

assign \$GT\_DELAY AgtB = A > B;

assign \$LT\_DELAY AltB = A < B;

endmodule</pre>

# 1.4.3 Behavioral Modeling:

Behavioral modeling is the highest level of abstraction in the Verilog HDL. The other modeling techniques are relatively detailed. They require some knowledge of how hardware or hardware signals work. The abstraction in this modeling is as simple as writing the logic in C language. This is a very powerful abstraction technique. All that a designer need is the algorithm of the design, which is the basic information for any design. Most of the behavioral modeling is done using two important constructs: initial and always. All the other behavioral statements appear only inside these two structured procedure constructs.

# **Example:**

# 4x1 Multiplexer

```

module mux4( input a, b, c, d

input [1:0] sel,

output out );

always @(a or b or c or d or sel)

begin

if(sel==0)

out = a;

else if (sel==1)

out = b;

else if (sel==2)

out = c;

else if (sel == 3)

out = d;

end

endmodule

```

# D flip-flop

module RisingEdge\_DFlipFlop(D,clk,Q);

input D; // Data input

input clk; // clock input

output Q; // output Q always @(posedgeclk) 27 begin Q <= D; end endmodule

# Shift Register (Serial In Serial Out)

module shift (C, SI, SO); input C,SI; output SO; reg [7:0] tmp; always @(posedge C) begin tmp = tmp<< 1; tmp[0] = SI; end assign SO = tmp[7]; endmodule

## **Procedural Assignments:**

Procedural assignments are for updating reg, integer, time, and memory variables. There is a significant difference between procedural assignment and continuous assignment as described below –

Continuous assignments drive net variables and are evaluated and updated whenever an input operand changes value.

Procedural assignments update the value of register variables under the control of the procedural flow constructs that surround them.

The right-hand side of a procedural assignment can be any expression that evaluates to a value. However, part-selects on the right-hand side must have constant indices. The lefthand side indicates the variable that receives the assignment from the right-hand side. The left-hand side of a procedural assignment can take one of the following forms

- register, integer, real, or time variable

- An assignment to the name reference of one of these data types. bit-select of a register, integer, real, or time variable

- An assignment to a single bit that leaves the other bits untouched. part-select of a register, integer, real, or time variable

- A part-select of two or more contiguous bits that leaves the rest of the bits untouched. For the part-select form, only constant expressions are legal. memory element – A single word of a memory. Note that bit-selects and part-selects are illegal on memory element references. concatenation of any of the above

- A concatenation of any of the previous four forms can be specified, which effectively

partitions the result of the right-hand side expression and assigns the partition parts, in order, to the various parts of the concatenation.

**Nonblocking (RTL) Assignments:** The non-blocking procedural assignment allows you to schedule assignments without blocking the procedural flow. You can use the non-blocking procedural statement whenever you want to make several register assignments within the same time step without regard to order or dependence upon each other.

<lvalue> <= <timing\_control> <expression>

Where lvalue is a data type that is valid for a procedural assignment statement,  $\leq$  is the non-blocking assignment operator, and timing control is the optional intra-assignment timing control. The timing control delay can be either a delay control or an event control (for example, @(posedge clk)). The expression is the right-hand side value the simulator assigns to the left-hand side. The non-blocking assignment operator is the same operator the simulator uses for the less-than-orequal relational operator. The simulator interprets the  $\leq$  operator to be a relational operator when you use it in an expression, and interprets the  $\leq$  operator to be an assignment operator when you use it in a non-blocking procedural assignment construct. How the simulator evaluates non-blocking procedural assignments When the simulator encounters a non-blocking procedural assignment in two steps as follows –

The simulator evaluates the right-hand side and schedules the assignment of the new value to take place at a time specified by a procedural timing control.

The simulator evaluates the right-hand side and schedules the assignment of the new value to take place at a time specified by a procedural timing control. At the end of the time step, in which the given delay has expired or the appropriate event has taken place, the simulator executes the assignment by assigning the value to the left-hand side.

**Case Statement:** The case statement is a special multi-way decision statement that tests whether an expression matches one of a number of other expressions, and branches accordingly. The case statement is useful for describing, for example, the decoding of a microprocessor instruction. The case statement has the following syntax –

The case expressions are evaluated and compared in the exact order in which they are given. During the linear search, if one of the case item expressions matches the expression in parentheses, then the statement associated with that case item is executed. If all comparisons fail, and the default item is given, then the default item statement is executed. If the default statement is not given, and all of the comparisons fail, then none of the case item statements is executed.

Apart from syntax, the case statement differs from the multi-way if-else-if construct in two important ways –

The conditional expressions in the if-else-if construct are more general than comparing one expression with several others, as in the case statement.

The case statement provides a definitive result when there are x and z values in an expression.

**Looping Statements:** There are four types of looping statements. They provide a means of controlling the execution of a statement zero, one, or more times. forever continuously executes a statement. repeat executes a statement a fixed number of times. while executes a statement until an expression becomes false. If the expression starts out false, the statement is not executed at all. for controls execution of its associated statement(s) by a three-step process, as follows

- Executes an assignment normally used to initialize a variable that controls the number of loops executed Evaluates an expression

- if the result is zero, the for loop exits, and if it is not zero, the for loop executes its associated statement(s) and then performs step 3 Executes an assignment normally used to modify the value of the loopcontrol variable, then repeats step 2.

**Procedures:** Always and Initial Blocks All procedures in Verilog are specified within one of the following four Blocks. 1) Initial blocks 2) Always blocks 3) Task 4) Function The initial and always statements are enabled at the beginning of simulation. The initial blocks executes only once and its activity dies when the statement has finished. In contrast, the always blocks executes repeatedly. Its activity dies only when the simulation is terminated. There is no limit to the number of initial and always blocks that can be defined in a module. Tasks and functions are procedures that are enabled from one or more places in other procedures.

# **1.4.4 Structural Modelling:**

The structural model of Verilog HDL is described using:

- Gate instantiation

- UDP instantiation

- Module instantiation

Module: A module defines a basic unit in Verilog HDL. It is of the form:

module\_name ( port\_list );

Declarations\_and\_Statements

endmodule

The port list gives the list of ports through which the module communicates with the external modules.

**Ports:** A port can be declared as input, output or inout. A port by default is a net. However, it can be explicitly declared as a net. An output or an inout port can optionally be redeclared as a regregister. In either the net declaration or the register declaration the net or register must have the same size as the one specified in the port declaration. Here are some examples of declarations.

module Micro {PC, Instr, NextAddr);

// Port declarations:

input [3:1] PC;

output [1:8] Instr;

inout [16:1]NextAddr; // Redeclarations: wire [16:1] NextAddr; //Optional; but if specified must have same range as in its port declaration. reg [1:8] Instr; /\* Instr has been redeclared as a reg so that it can be assigned a value within an always statement or an initial statement. \*/ endmodule

**Module Instantiation**: A module can be instantiated in another module, thus creating hierarchy. A module instantiation statement is of the form:

module\_name instance\_name( port\_associations);

Port associations can be by position or by name; however, associations cannot be mixed. A

port association is of the form:

port\_expr // By position.

.PortName (port\_expr )// By name.

Where port\_expr can be any of the following:

i. an identifier (a register or a net)

ii. a bit-select

iii. a part-select

iv. a concatenation of the above

v. an expression (only for input ports)

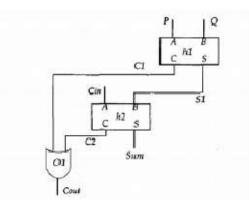

In positional association, the port expressions connect to the ports of the module in the specified order. In association by name, the connection between the module port and the port expression is explicitly specified and thus the order of port associations is not important. Here is an example of a full-adder built using two half-adder modules.

# Half Adder:

module HA (A, B, S, C); input A, B; output S, C; parameter AND\_DELAY = 1, XOR\_DELAY = 2; assign #XOR\_DELAY s=A ^ B; assign #AND\_ DELAY C= A & B; endmodule

# **Full Adder:**

module FA (P, Q, Cin, Sum, Cout); input P, Q, Cin; output Sum, Cout; parameter OR\_DELAY = 1; wire SI, CI, C2; //Two module instantiations: HA h1 (P, Q, S1, C1); // Associatingby position. HA h2 (.A(Cin), .S(Sum), .B(S1), .C(C2)); //Associating by name. // Gate instantiation: or #OR\_DELAY 01 (Cout, CI, C2) ; endmodule

Figure 1.5: Full Adder using Two Half Adders

In the first module instantiation, HA is the name of the module, h1 is the instance name and ports are associated by position, that is, P is connected to module (HA) port A, Q is connected to module port B, S1 to S and C1 to module port C. In the second instantiation, the port association is by name, that is, the connections between the module (HA) ports and the port expressions are specified explicitly.

Example:

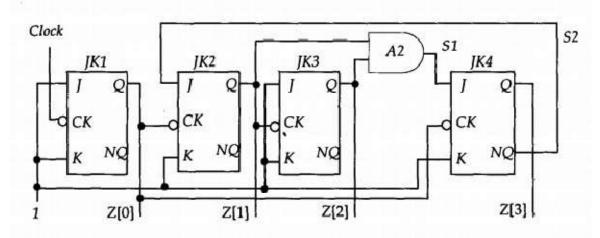

## **Decade Counter:**

**Figure 1.6: Decade Counter**

module Decade\_Ctr(Clock, Z); input Clock; output [0:3] Z; wire \$I, \$2; and A1 {\$I, Z[2], Z[1]);// Primitive gate instantiation. // Four module instantiations: JK\_FF JK1 (.J(1'b1), .K(1'b1), .ck(Clock), .Q(z[0]), .NQ ()), JK2 (.J(1'b1), .K(1'b1), .ck(Z[0]), .Q(z[1]), .NQ ()), JK3 (.J(1'b1), .K(1'b1), .ck(Z[1]), .Q(z[2]), .NQ ()), JK4 (.J(1'b1), .K(1'b1), .ck(Z[0]), .Q(z[1]), .NQ (\$2)); endmodule

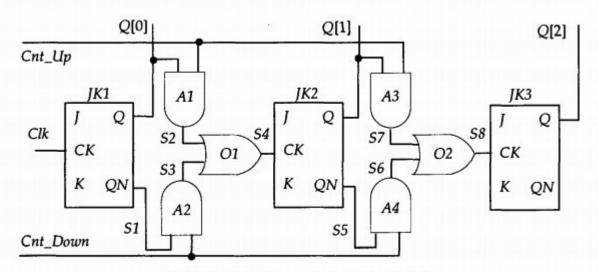

# **3-bit UP-DOWN counter**

(J,K inputs of all flip-flops connected to 1)

Figure 1.7: 3-bit UP-DOWN counter

moduleUp\_Down {Clk, Cnt\_Up, Cnt\_Down, Q); inputClk, Cnt\_Up, Cnt\_Down; output [0:2] Q; wire S1, S2, S3, S4, S5,S6, S7, S8; JK\_FF JK1 (l'bl, l'bl, Clk, Q[Q], S1), JK2 (l'bl, l'bl, S4, Q[1], S5), JK3 (l'bl, l'bl, S8, Q[2], ); and A1 (S2, Cnt\_Up, Q[Q]), A2 (S3, SI, Cnt\_Down), A3 (S7, Q[1], Cnt\_Up), A4 (S6, S5, Cnt\_Down); or 01 (S4, S2, S3), 02 (S8,S7, S6); endmodule

# **1.5 USER-DEFINED PRIMITIVES (UDP):**

The primitives available in Verilog are the entire gate or switch types. Verilog has the provision for the user to define primitives them. The designers occasionally like to use their own custom-built primitives when developing a design. Verilog provides the ability to define User-Defined Primitives (UDP). These primitives are self contained and do not instantiate other modules or primitives. UDPs are instantiated exactly like gate level primitives. UDPs are basically of two types combinational and sequential. A combinational UDP is used to define a combinational scalar

A combinational UDP accepts a set of scalar inputs and gives a scalar output. An inout declaration is not supported by a UDP. The UDP definition is on par with that of a module; that is, it is defined independently like a module and can be used in any other module.

primitiveudp\_and(out, a, b); output out; input a, b; table // a b: Out; 0 0: 0; 0 1: 0; 1 0: 0 1 1: 1; endtable endprimitive

Any sequential circuit has a set of possible states. When it is in one of the specified states, the next state to be taken is described as a function of the input logic variables and the present state.

primitive latch(q, d, clock, clear); // d-latch

output q; reg q; //q declared as reg to create internal storage

input d, clock, clear;

initial q = 0; //initialize output to value 0

table

//state table

//d clock clear: q : q+;

? ? 1 : ? : 0 ; //clear condition; 1 1 0 : ? : 1; //latchq =data=1 0 1 0 : ? : 0; //latchq =data=0 ? 0 0 : ? : - ; //retain original state if clock = 0 endtable endprimitive

# **Reference Books:**

- 1. Advanced Digital Design With the Verilog HDL, Michael D. Ciletti, 2nd Edition, PHI, ISBN: 978-0-07-338054-4 2015.

- 2. Digital Systems Design Using Verilog, Charles Roth, Lizy K. John, Byeong KilLee, Cengage Learning, ISBN-10: 1285051076, 2015.

- 3. Fundamentals of Digital Logic with Verilog Design, Stephen Brown and Zvonko Vranesic, 6th Edition, McGraw Hill publication, ISBN: 978–0–07–338054–4, 2014.

- System Verilog for Design A Guide to Using System Verilog for Hardware Design and Modeling, Stuart Sutherland, Simon David mann and Peter Flake, 2E, Springer Science, ISBN-13: 978-0387-3339-91, 2006.

- 5. System Verilog for Verification-A Guide to Learning the Testbench Language Features, C Spear, Springer Science, IEEE press, ISBN-13: 978-0387-2703-64,2006.

- 6. System Verilog golden reference guide-A concise guide to System Verilog Doulos, IEEE Standard-1800- 2009, Version 5.0,ISBN: 0-9547345-9-9, 2012.

- 7. Step-by-Step Functional Verification with System Verilog and OVM, SasanIman, Hansen Brown Publishing Company, ISBN-13: 978-0-9816-5621-2, 2008.

# **Questions to Practice:**

# PART -A

- 1 Describe in detail about the types of modelling

- 2 Identify the data types and its functions.

- 3 Describe in detail about synthesis in Verilog

- 4 Classify the Data Operators in Verilog

- 5 Develop a Verilog code for D Flip Flop using Behavioural modelling

# PART-B

- 1 Develop a Verilog code for shift registers using structural modelling

- 2 Classify how Data Types are used in Verilog HDL

- 3 Demonstrate in detail about the User defined Data Types

- 4 Develop a Verilog code for Ripple carry Adder using structural modelling

- 5 Develop a Verilog code for Up/Down Counter using structural modelling

- 6 Develop a Verilog code for Full Adder using two half adders using structural modelling

# SCHOOL OF ELECTRICAL AND ELECTRONICS

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

# **UNIT – II – INTRODUCTION TO SYSTEM VERILOG – SECA3021**

# **UNIT-II (INTRODUCTION TO SYSTEM VERILOG)**

System Verilog standards, Key System Verilog enhancements for hardware design. Advantages of System Verilog over Verilog, Data Types: Verilog data types, System Verilog data types, 2 - State Data types, Bit, byte, shortint, int, longint. 4 - State data types. Logic, Enumerated data types, User Defined data types, Struct data types, Strings, Packages, Type Conversion: Dynamic casting, Static Casting, Memories: Arrays, Dynamic Arrays, Multidimensional Arrays, Packed Arrays, Associative Arrays, Queues, Array Methods, Tasks and Functions: Verilog Tasks and Functions

#### 2.1 Introduction :

SystemVerilog is a standard set of extensions to the IEEE 1364- 2005 Verilog Standard (commonly referred to as "Verilog-2005"). The SystemVerilog extensions to the Verilog HDL that are described in this book are targeted at design and writing synthesizable models. These extensions integrate many of the features of the SUPERLOG and C languages. SystemVerilog also contains many extensions for the verification of large designs, integrating features from the SUPERLOG, VERA C, C++, and VHDL languages, along with OVA and PSL assertions. These verification assertions are in a companion book, SystemVerilog for Verification.

This integrated whole created by SystemVerilog greatly exceeds the sum of its individual components, creating a new type of engineering language, a Hardware Description and Verification Language or HDVL. Using a single, unified language enables engineers to model large, complex designs, and verify that these designs are functionally correct.

#### 2.2 Generations of the System Verilog standard:

A major portion of SystemVerilog was released as an Accellera standard in June of 2002 under the title of SystemVerilog 3.0. This initial release of the SystemVerilog standard allowed EDA companies to begin adding the SystemVerilog extensions to existing simulators, synthesis compilers and other engineering tools. The focus of this first release of the SystemVerilog standard was to extend the synthesizable constructs of Verilog, and to enable modeling hardware at a higher level of abstraction.

SystemVerilog began with a version number of 3.0 to show that SystemVerilog is the third major generation of the Verilog language. Verilog-1995 is the first generation, which represents the standardization of the original Verilog language defined by Phil Moorby in the early 1980s. Verilog-2001 is the second major generation of Verilog, and SystemVerilog is the third major generation.

Accellera continued to refine the SystemVerilog 3.1 standard by working closely with major Electronic Design Automation (EDA) companies to ensure that the SystemVerilog specification could be implemented as intended. A few additional modeling and verification constructs were also defined. In May of 2004, a final Accellera SystemVerilog draft was ratified by Accellera, and called System-Verilog 3.1a.

Prior to the donation of SystemVerilog 3.1a to the IEEE, the IEEESA had already begun work on the next revision of the IEEE 1364 Verilog standard. At the encouragement of Accellera, the IEEE-SA organization decided not to immediately add the SystemVerilog extensions to work already in progress for extending Verilog 1364. Instead, it was decided to keep the SystemVerilog extensions as a separate document. To ensure that the reference manual for the base Verilog language and the reference manual for the SystemVerilog extensions to Verilog remained synchronized, the IEEE-SA dissolved the 1364 Working Group and made the 1364 Verilog reference manual part of the responsibility of the 1800 SystemVerilog Working Group. The 1800 Working Group formed a subcommittee to update the 1364 Verilog standard in parallel with the specification of the P1800 SystemVerilog. For the most part, the work done on the 1364 revisions was limited to errata corrections and clarifications. Most extensions to Verilog were specified in the P1800 standard. The 1800 SystemVerilog Working Group released a ballot draft for an updated Verilog P1364 standard at the same time as the ballot draft for the new P1800 SystemVerilog standard. Both standards were approved at the same time.

# 2.3 Key SystemVerilog enhancements for hardware design

The following list highlights some of the more significant enhancements SystemVerilog adds to the Verilog HDL for the design and verification of hardware: This list is not intended to be all inclusive of every enhancement to Verilog that is in SystemVerilog. This list just highlights a few key features that aid in writing synthesizable hardware models.

- Interfaces to encapsulate communication and protocol checking within a design

- C like data types, such as int

- User-defined types, using typedef

- Enumerated types

- Type casting

- Structures and unions

- Packages for definitions shared by multiple design blocks

- External compilation-unit scope declarations

- ++, --, += and other assignment operators

- Explicit procedural blocks

- Priority and unique decision modifiers

- Programming statement enhancements

- Pass by reference to tasks, functions and modules

# 2.4 Packages

In Verilog, declarations of variables, nets, tasks and functions must be declared within a module, between the module...endmodule keywords. The objects declared within a module are local to the module. For modeling purposes, these objects should be referenced within the module in which they are declared. Verilog also allows hierarchical references to these objects from other modules for verification purposes, but these cross-module references do not represent

hardware behavior, and are not synthesizable. Verilog also allows local variables to be defined in named blocks (formed with begin...end or fork...join), tasks and functions. These declarations are still defined within a module, however, and, for synthesis purposes, only accessible within the module. Verilog does not have a place to make global declarations, such as global functions.

A declaration that is used in multiple design blocks must be declared in each block. This not only requires redundant declarations, but it can also lead to errors if a declaration, such as a function, is changed in one design block, but not in another design block that is supposed to have the same function. Many designers use include files and other coding tricks to work around this shortcoming, but that, too, can lead to coding errors and design maintenance problems.

SystemVerilog adds user-defined types, using typedef. It is often desirable to use the definition of user-defined types in multiple modules. Using Verilog rules, where declarations are always local to a module, it would be necessary to duplicate a user-defined type definition in each and every module in which the definition is used. Redundant local definitions would not be desirable for user-defined types.

## 2.4.1 Package definitions

To enable sharing a user-defined type definition across multiple modules, SystemVerilog adds packages to the Verilog language. The concept of packages is leveraged from the VHDL language. SystemVerilog packages are defined between the keywords package and endpackage.

The synthesizable constructs that a packages can contain are:

- parameter and localparam constant definitions

- const variable definitions

- typedef user-defined types

- Fully automatic task and function definitions

- import statements from other packages

- Operator overload definitions

Packages can also contain global variable declarations, static task definitions and static function definitions.

Packages can contain parameter, localparam and const constant declarations. The parameter and localparam constants are Verilog constructs. A const constant is a SystemVerilog constant. In Verilog, a parameter constant can be redefined for each instance of a module, whereas a localparam cannot be directly redefined. In a package, however, a parameter constant cannot be redefined, since it is not part of a module instance. In a package, parameter and localparam are synonymous.

## **Example:**

```

package definitions;

parameter VERSION = "1.1";

typedef enum {ADD, SUB, MUL} opcodes_t;

typedef struct {

logic [31:0] a, b;

opcodes_t opcode;

) instruction_t;

function automatic [31:0] multiplier (input [31:0] a, b);

// code for a custom 32-bit multiplier goes here

return a * b; // abstract multiplier (no error detection)

endfunction

endpackage

```

# 2.4.2 Referencing package contents

Modules and interfaces can reference the definitions and declarations in a package four ways:

- Direct reference using a scope resolution operator

- Import specific package items into the module or interface

- Wildcard import package items into the module or interface

- Import package items into the \$unit declaration space

SystemVerilog allows specific package items to be imported into a module, using an import statement. When a package definition or declaration is imported into a module or interface, that item becomes visible within the module or interface, as if it were a locally defined name within that module or interface. It is no longer necessary to explicitly reference the package name each time that package item is referenced.

# 2.4.3 Synthesis guidelines

When a module references a task or function that is defined in a package, synthesis will duplicate the task or function functionality and treat it as if it had been defined within the module. To be synthesizable, tasks and functions defined in a package must be declared as automatic, and cannot contain static variables. This is because storage for an automatic task or function is effectively allocated each time it is called. Thus, each module that references an automatic task or function in a package sees a unique copy of the task or function storage that is not shared by any other module. This ensures that the simulation behavior of the presynthesis reference to the package task or function will be the same as post-synthesis behavior, where the functionality of the task or function has been implemented within one or more modules. For similar reasons, synthesis does not support variables declarations in packages. In simulation, a package variable will be shared by all modules that import the variable. One module can write to the variable, and another module will see the new value. This type of inter-module communication without passing values through module ports is not synthesizable.

# 2.5 \$unit compilation-unit declarations

SystemVerilog adds a concept called a compilation unit to Verilog. A compilation unit is all source files that are compiled at the same time. Compilation units provide a means for software tools to separately compile sub-blocks of an overall design. A sub-block might comprise a single module or multiple modules. The modules might be contained in a single file or in multiple files. A sub-block of a design might also contain interface blocks and testbench program blocks.

SystemVerilog extends Verilog's declaration space by allowing declarations to be made outside of package, module, interface and program block boundaries. These external declarations are in a compilation-unit scope, and are visible to all modules that are compiled at the same time.

The compilation-unit scope can contain:

- Time unit and precision declarations

- Variable declarations

- Net declarations

- Constant declarations

- User-defined data types, using typedef, enum or class

- Task and function definitions

The following example illustrates external declarations of a constant, a variable, a user-defined

type, and a

function.

```

/********************** External declarations ******************/

parameter VERSION = "1.2a"; // external constant

// external variable (active low)

reg resetN = 1;

typedef struct packed

// external user-defined type

reg [31:0] address;

reg [31:0] data;

reg [ 7:0] opcode;

} instruction word t;

function automatic int log2 (input int n); // external function

if (n <=1) return(1);</pre>

10g2 = 0;

while (n > 1) begin

n = n/2;

log2++;

end

return (log2);

endfunction

```

A declaration in the compilation-unit scope is not the same as a global declaration. A true global declaration, such as a global variable or function, would be shared by all modules that make up a design, regardless of whether or not source files are compiled separately or at the same time.

SystemVerilog's compilation-scope only exists for source files that are compiled at the same time. Each time source files are compiled, a compilation-unit scope is created that is unique to just that compilation. For example, if module CPU and module controller both reference an externally declared variable called reset, then two possible scenarios exist:

• If the two modules are compiled at the same time, there will be a single compilationunit scope. The externally declared reset variable will be common to both modules.

• If each module were compiled separately, then there would be two compilation-unit scopes, possibly with two different reset variables.

In the latter scenario, the compilation that included the external declaration of reset would appear to compile OK. The other file, when compiled separately, would have its own, unique \$unit compilation space, and would not see the declaration of reset from the previous compilation. Depending on the context of how reset is used, the second compilation might fail, due to an undeclared variable, or it might compile OK, making reset an implicit net. This is a dangerous possibility! If the second compilation succeeds by making reset an implicit net, there will now be two signals called reset, one in each compilation. The two different reset signals would not be connected in any way.

# 2.5.1 Coding guidelines:

- Do not make any declarations in the \$unit space! All declarations should be made in named packages.

- When necessary, packages can be imported into \$unit. This is useful when a module or interface contains multiple ports that are of user-defined types, and the type definitions are in a package.

Directly declaring objects in the \$unit compilation-unit space can lead to design errors when files are compiled separately. It can also lead to spaghetti code if the declarations are scattered in multiple files that can be difficult to maintain, re-use, or to debug declaration errors.

#### 2.5.2 Variables and nets in the compilation-unit scope

There is an important consideration when using external declarations. Verilog supports implicit type declarations, where, in specific contexts, an undeclared identifier is assumed to be a net type (typically a wire type). Verilog requires the type of identifiers to be explicitly declared before the identifier is referenced when the context will not infer an implicit type, or when a type other than the default net type is desired.

This implicit type declaration rule affects the declaration of variables and nets in the compilation-unit scope. Software tools must encounter the external declaration before an identifier is referenced. If not, the name will be treated as an undeclared identifier, and follow the Verilog rules for implicit types.

The following example illustrates how source code order can affect the usage of a declaration external to the module. This example will not generate any type of compilation or elaboration error. For module parity\_gen, software tools will automatically infer parity as an implicit net type local to the module, since the reference to parity comes before the external declaration for the signal. On the other hand, module parity\_check comes after the external declaration of parity in the source code order. Therefore, the parity\_check module will use the external variable declaration.

# 2.5.3 Synthesis Guidelines

The synthesizable constructs that can be declared within the compilation- unit scope (external to all module and interface definitions) are:

- typedef user-defined type definitions

- Automatic functions

- Automatic tasks

- parameter and localparam constants

- Package imports

While not a recommended style, user-defined types defined in the compilation-unit scope are synthesizable. A better style is to place the definitions of user-defined types in named packages. Using packages reduces the risk of spaghetti code and file order dependencies.

Declarations of tasks and functions in the \$unit compilation-unit space is also not a recommended coding style. However, tasks and functions defined in \$unit are synthesizable. When a module references a task or function that is defined in the compilation-unit scope, synthesis will duplicate the task or function code and treat it as if it had been defined within the module. To be synthesizable, tasks and functions defined in the compilation-unit scope must be declared as automatic, and cannot contain static variables. This is because storage for an automatic task or function is effectively allocated each time it is called. Thus, each module that references an automatic task or function in the compilation-unit scope sees a unique copy of the task or function storage that is not shared by any other module. This ensures that the simulation behavior of the presynthesis reference to the compilation-unit scope task or function will be the same as post-synthesis behavior, where the functionality of the task or function has been implemented within the module.

A parameter constant defined within the compilation-unit scope cannot be redefined, since it is not part of a module instance. Synthesis treats constants declared in the compilation-unit scope as literal values. Declaring parameters in the \$unit space is not a good modeling style, as the constants will not be visible to modules that are compiled separately from the file that contains the constant declarations.

#### 2.6 Declarations in unnamed statement blocks

Verilog allows local variables to be declared in named begin...end or fork...join blocks. A common usage of local variable declarations is to declare a temporary variable for controlling a loop. The local variable prevents the inadvertent access to a variable at the module level of the same name, but with a different usage. The following code fragment has declarations for two variables, both named i. The for loop in the named begin block will use the local variable i that is declared in that named block, and not touch the variable named i declared at the module level.

```

module chip (input clock);

integer i; // declaration at module level

always @ (posedge clock)

begin: loop // named block

integer i; // local variable

for (i=0; i<=127; i=i+1) begin

...

end

end

end

endmodule</pre>

```

A variable declared in a named block can be referenced with a hierarchical path name that includes the name of the block. Typically, only a testbench or other verification routine would reference a variable using a hierarchical path. Hierarchical references are not synthesizable, and do not represent hardware behavior. The hierarchy path to the variable within the named block can also be used by VCD (Value Change Dump) files, proprietary waveform displays, or other debug tools, in order to reference the locally declared variable. The following testbench fragment uses hierarchy paths to print the value of both the variables named i in the preceding example:

```

module test;

reg clock;

chip chip (.clock(clock));

always #5 clock = ~clock;

initial begin

clock = 0;

repeat (5) @(negedge clock) ;

$display("chip.i = %0d", chip.i);

$display("chip.loop.i = %0d", chip.loop.i);

$finish;

end

endmodule

```

#### 2.6.1 Local variables in unnamed blocks

SystemVerilog extends Verilog to allow local variables to be declared in unnamed blocks. The syntax is identical to declarations in named blocks, as illustrated below:

Since there is no name to the block, local variables in an unnamed block cannot be referenced hierarchically. A testbench or a VCD file cannot reference the local variable, because there is no hierarchy path to the variable.

Declaring variables in unnamed blocks can serve as a means of protecting the local variables from external, cross-module references. Without a hierarchy path, the local variable cannot be referenced from anywhere outside of the local scope.

This extension of allowing a variable to be declared in an unnamed scope is not unique to SystemVerilog. The Verilog language has a similar situation. User-defined primitives (UDPs) can have a variable declared internally, but the Verilog language does not require that an instance name be assigned to primitive instances. This also creates a variable in an unnamed scope. Software tools will infer an instance name in this situation, in order to allow the variable within the UDP to be referenced in the tool's debug utilities. Software tools may also assign an inferred name to an unnamed block, in order to allow the tool's waveform display or debug utilities to reference the local variables in that unnamed block. The SystemVerilog standard neither requires nor prohibits a tool inferring a scope name for unnamed blocks, just as the Verilog standard neither requires nor prohibits the inference of instance names for unnamed primitive instances.

# 2.7 SystemVerilog Literal Values and Built-in Data Types

SystemVerilog extends Verilog's built-in variable types, and enhances how literal values can be specified. This chapter explains these enhancements and offers recommendations on proper usage. A number of small examples illustrate these enhancements in context. Subsequent chapters contain other examples that utilize SystemVerilog's enhanced variable types and literal values.

The enhancements presented in this chapter include:

- Enhanced literal values

- 'define text substitution enhancements

- Time values

- New variable types

- Signed and unsigned types

- Variable initialization

- Static and automatic variables

- Casting

- Constants

# 2.8 SystemVerilog variables

# 2.8.1 Object types and data types:

*Verilog Data Types:* The Verilog language has hardware-centric variable types and net types. These types have special simulation and synthesis semantics to represent the behavior of actual connections in a chip or system.

$\bullet$  The Verilog reg, integer and time variables have 4 logic values for each bit: 0, 1, Z and X.

• The Verilog wire, wor, wand, and other net types have 120 values for each bit (4-state logic plus multiple strength levels) and special wired logic resolution functions.

*System Verilog Data Types:* Verilog does not clearly distinguish between signal types, and the value set the signals can store or transfer. In Verilog, all nets and variables use 4-state values, so a clear distinction is not necessary. To provide more flexibility in variable and net types and the values that these types can store or transfer, the SystemVerilog standard defines that signals in a design have both a type and a data type.

Type indicates if the signal is a net or variable. SystemVerilog uses all the Verilog variable types, such as reg and integer, plus adds several more variable types, such as byte and int. SystemVerilog does not add any extensions to the Verilog net types.

Data type indicates the value system of the net or variable, which is 0 or 1 for 2state data types, and 0, 1, Z or X for 4-state data types. The SystemVerilog keyword bit defines that an object is a 2-state data type. The SystemVerilog keyword logic defines that an object is a 4-state data type. In the SystemVerilog-2005 standard, variable types can be either 2-state or 4-state data types, where as net types can only be 4-state data types.

# 2.8.2 SystemVerilog 4-state and 2-state variables

*The 4-state logic type:* The Verilog language uses the reg type as a general purpose variable for modeling hardware behavior in initial and always procedural blocks. The keyword reg is a misnomer that is often confusing to new users of the Verilog language. The term "reg" would seem to imply a hardware "register", built with some form of sequential logic flip-flops. In actuality, there is no correlation whatsoever between using a reg variable and the hardware that will be inferred. It is the context in which the reg variable is used that determines if the hardware represented is combinational logic or sequential logic. SystemVerilog uses the more intuitive logic keyword to represent a general purpose, hardware-centric data type.

```

logic resetN; // a 1-bit wide 4-state variable

logic [63:0] data; // a 64-bit wide variable

logic [0:7] array [0:255]; // an array of 8-bit

variables

```

The keyword logic is not actually a variable type, it is a data type, indicating the signal can have 4-state values. However, when the logic keyword is used by itself, a variable is implied. A 4-state variable can be explicitly declared using the keyword pair var logic.

For example: var logic [63:0] addr; // a 64-bit wide variable

A Verilog net type defaults to being a 4-state logic data type. A net can also be explicitly declared as a 4-state data type using the logic keyword.

For example: wire logic [63:0] data; // a 64-bit wide net

Semantically, a variable of the logic data type is identical to the Verilog reg type. The two keywords are synonyms, and can be used interchangeably (except that the reg keyword cannot be paired with net type keywords, as discussed in section 3.3.4 on page 47). Like the Verilog reg variable type, a variable of the logic data type can store 4-state logic values (0, 1, Z and X), and can be defined as a vector of any width.

Because the keyword logic does not convey a false implication of the type of hardware represented, logic is a more intuitive keyword choice for describing hardware when 4-state logic is required. In the subsequent examples in this book, the logic type is used in place of the Verilog

reg type (except when the example illustrates pure Verilog code, with no SystemVerilog enhancements).

*SystemVerilog 2-state variables:* SystemVerilog adds several new 2-state types, suitable for modeling at more abstract levels than RTL, such as system level and transaction level. These types include:

- bit a 1-bit 2-state integer

- byte an 8-bit 2-state integer, similar to a C char

- shortint a 16-bit 2-state integer, similar to a C short

- int a 32-bit 2-state integer, similar to a C int

- longint a 64-bit 2-state integer, similar to a C longlong

Variables of the reg or logic data types are used for modeling hardware behavior in procedural blocks. These types store 4-state logic values, 0, 1, Z and X. 4-state types are the preferred types for synthesizable RTL hardware models. The Z value is used to represent unconnected or tri-state design logic. The X value helps detect and isolate design errors. At higher levels of modeling, such as the system and transaction levels, logic values of Z and X are seldom required.

SystemVerilog allows variables to be declared as a bit data type. Syntactically, a bit variable can be used any place reg or logic variables can be used. However, the bit data type is semantically different, in that it only stores 2-state values of 0 and 1. The bit data type can be useful for modeling hardware at higher levels of abstraction. Variables of the bit data type can be declared in the same way as reg and logic types. Declarations can be any vector width, from 1-bit wide to the maximum size supported by the software tool (the IEEE 1364 Verilog standard defines that all compliant software tools should support vector widths of at least 216 bits wide).

## 2.9 Type casting

Verilog is a loosely typed language that allows a value of one type to be assigned to a variable or net of a different type. When the assignment is made, the value is converted to the new type, following rules defined as part of the Verilog standard. SystemVerilog adds the ability to cast a value to a different type. Type casting is different than converting a value during an assignment. With type casting, a value can be converted to a new type within an expression, without any assignment being made. The Verilog 1995 standard did not provide a way to cast a value to a different type. Verilog-2001 added a limited cast capability that can convert signed values to unsigned, and unsigned values to signed. This conversion is done using the system functions \$signed and \$unsigned.

#### **2.9.1** Static Casting:

SystemVerilog adds a cast operator to the Verilog language. This operator can be used to cast a value from one type to another, similar to the C language. SystemVerilog's cast operator goes beyond C, however, in that a vector can be cast to a different size, and signed values can be cast to unsigned or vice versa. To be compatible with the existing Verilog language, the syntax of SystemVerilog's cast operator is different than C's. <type>'(<expression>) — casts a value to any type, including user-defined types.

For Example:

```

7+ int' (2.0 * 3.0); // cast result of

// (2.0 * 3.0) to int,

// then add to 7

size casting <size>' (<expression>) - casts a value to any vector size. For

example:

logic [15:0] a, b, y;

y = a + b**16'(2); // cast literal value 2

// to be 16 bits wide

sign casting <sign>' (<expression>) - casts a value to signed or unsigned.

For example:

shortint a, b;

int

Y:

y = y - signed' ((a,b)); // cast concatenation

// result to a signed

// value

```

#### 2.9.1.1 Static casting and error checking:

The static cast operation is a compile-time cast. The expression to be cast will always be converted during run time, without any checking that the expression to be cast falls within the legal range of the type to which the value is cast. In the following example, a static cast is used to increment the value of an enumerated variable by 1. The static cast operator does not check that the result of state + 1 is a legal value for the next\_state enumerated type. Assigning an out of range value to next\_state using a static cast will not result in a compile-time or run-time error. Therefore, care must be taken not to cause an illegal value to be assigned to the next\_state variable.

```

typedef enum {S1, S2, S3} states_t;

states_t state, next_state;

always_comb begin

if (state != S3)

next_state = states_t'(state + 1);

else

next_state = S1;

end

```

## 2.9.2 Dynamic casting

The static cast operation described above is a compile-time cast. The cast will always be performed, without checking the validity of the result. When stronger checking is desired, SystemVerilog provides a new system function, \$cast, that performs dynamic, runtime checking on the value to be cast.

The \$cast system function takes two arguments, a destination variable and a source variable.

```

$cast( dest_var, source_exp );

For example:

int radius, area;

always @(posedge clock)

$cast(area, 3.154 * radius ** 2);

// result of cast operation is cast to

// the type of area

```

\$cast attempts to assign the source expression to the destination variable. If the assignment is invalid, a run-time error is reported, and the destination variable is left unchanged. Some examples that would result in an invalid cast are:

• Casting a real to an int, when the value of the real number is too large to be represented as an int (as in the example, above).

• Casting a value to an enumerated type, when the value does not exist in the legal set of values in the enumerated type list

## 2.10 User-Defined and Enumerated Types

SystemVerilog makes a significant extension to the Verilog language by allowing users to define new net and variable types. User-defined types allow modeling complex designs at a more abstract level that is still accurate and synthesizable. Using System- Verilog's user-defined types, more design functionality can be modeled in fewer lines of code, with the added advantage of making the code more self-documenting and easier to read.

The enhancements presented in this include:

- Using typedef to create user-defined types

- Using enum to create enumerated types

- Working with enumerated values

# 2.10.1 User Defined Types:

The Verilog language does not provide a mechanism for the user to extend the language net and variable types. While the existing Verilog types are useful for RTL and gate-level modeling, they do not provide C-like variable types that could be used at higher levels of abstraction. SystemVerilog adds a number of new types for modeling at the system and architectural level. In addition, SystemVerilog adds the ability for the user to define new net and variable types.

SystemVerilog user-defined types are created using the typedef keyword, as in C. Userdefined types allow new type definitions to be created from existing types. Once a new type has been defined, variables of the new type can be declared.

```

typedef int unsigned uint;

...

uint a, b; // two variables of type uint

```

Local typedef definitions: User-defined types can be defined locally, in a package, or externally, in the compilation-unit scope. When a user-defined type will only be used within a specific part of the design, the typedef definition can be made within the module or interface representing that portion of the design. Interfaces are presented in Chapter 10. In the code snippet that follows, a user-defined type called nibble is declared, which is used for variable declarations within a module called alu. Since the nibble type is defined locally, only the alu module can see the definition. Other modules or interfaces that make up the overall design are not affected by the local definition, and can use the same nibble identifier for other purposes without being affected by the local typedef definition in module alu.

*Shared typedef definitions:* When a user-defined type is to be used in many different models, the typedef definition can be declared in a package. These definitions can then be referenced directly, or imported into each module, interface or program block that uses the user-defined types.

A typedef definition can also be declared externally, in the compilation- unit scope. External declarations are made by placing the typedef statement outside of any module, interface or program block. For Example

It is also possible to import package definitions into the \$unit compilation- unit space. This can be useful when many ports of a module are of user-defined types, and it becomes tedious to directly reference the package name for each port declaration. Example illustrates importing a package definition into the \$unit space, for use as a module port type.

```

package chip types;

`ifdef TWO STATE

typedef bit dtype t;

èlse

typedef logic dtype t;

endif

endpackage

import chip types::dtype t; // import definition into $unit

module counter

(output dtype t [15:0] count,

input dtype t clock, resetN);

always @(posedge clock, negedge resetN)

if (!resetN) count <= 0;

else

count <= count + 1;

endmodule

```

If the package contains many typedefs, instead of importing specific package items into the \$unit compilation-unit space, the package can be wildcard imported into \$unit.

#### 2.11 Enumerated Types:

Enumerated types provide a means to declare an abstract variable that can have a specific list of valid values. Each value is identified with a user-defined name, or label. In the following example, variable RGB can have the values of red, green and blue:

```

enum {red,green,blue} RGB;

```

The Verilog language does not have enumerated types. To create pseudo labels for data values, it is necessary to define a parameter constant to represent each value, and assign a value to that constant. Alternatively, Verilog's 'define text substitution macro can be used to define a set of macro names with specific values for each name. The following example shows a simple state machine sequence modeled using Verilog parameter constants and 'define macro names: The parameters are used to define a set of states for the state machine, and the macro names are used to define a set of states for the state machine.

Example:

```

'define FETCH 3'h0

'define WRITE 3'h1

'define ADD 3'h2

'define SUB 3'h3

'define MULT 3'h4

'define DIV 3'h5

'define SHIFT 3'h6

'define NOP 3'h7

module controller (output reg

read, write,

input wire [2:0] instruction,

input wire clock, resetN);

parameter WAITE = 0,

LOAD = 1,

STORE = 2;

reg [1:0] State, NextState;

always @ (posedge clock, negedge resetN)

if (!resetN) State <= WAITE;

else

State <= NextState;

always @(State) begin

case (State)

WAITE: NextState = LOAD;

LOAD: NextState = STORE;

STORE: NextState = WAITE;

endcase

end

always @(State, instruction) begin

read = 0; write = 0;

if (State == LOAD && instruction == `FETCH)

read = 1;

else if (State == STORE && instruction == `WRITE)

write = 1;

end

endmodule

```

The variables that use the constant values—State and NextState in the preceding example—must be declared as standard Verilog variable types. This means a software tool cannot limit the valid values of those signals to just the values of the constants. There is nothing that would limit State or NextState in the example above from having a value of 3, or a value with one or more bits set to X or Z. Therefore, the model itself must add some limit checking on

the values. At a minimum, a synthesis "full case" pragma would be required to specify to synthesis tools that the state variable only uses the values of the constants that are listed in the case items. The use of synthesis pragmas, however, would not affect simulation, which could result in mismatches between simulation behavior and the structural design created by synthesis.

Example: State machine modeled with enumerated types

```

package chip_types;

typedef enum (FETCH, WRITE, ADD, SUB,

MULT, DIV, SHIFT, NOP ) instr t;

endpackage

import chip types::*; // import package definitions into $unit

module controller (output logic read, write,

input instr_t instruction,

input wire clock, resetN);

enum (WAITE, LOAD, STORE) State, NextState;

always ff @ (posedge clock, negedge resetN)

if (!resetN) State <= WAITE;

State <= NextState;

else

always comb begin

case (State)

WAITE: NextState = LOAD;

LOAD: NextState = STORE;

STORE: NextState = WAITE;

endcase

end

always comb begin

read = 0; write = 0;

if (State == LOAD && instruction == FETCH)

read = 1;

else if (State == STORE && instruction == WRITE)

write = 1;

end

endmodule

```

In this example, the variables State and NextState can only have the valid values of WAITE, LOAD, and STORE. All software tools will interpret the legal value limits for these enumerated type variables in the same way, including simulation, synthesis and formal verification.

#### 2.12 Arrays:

```

2.12.1 Unpacked arrays:

```

The basic syntax of a Verilog array declaration is: <data\_type> <vector\_size> <array\_name> <array\_dimensions> For example: reg [15:0] RAM [0:4095]; // memory array

Verilog-1995 only permitted one-dimensional arrays. A one-dimensional array is often referred to as a memory, since its primary purpose is to model the storage of hardware memory devices such as RAMs and ROMs. Verilog-1995 also limited array declarations to just the variable types reg, integer and time. Verilog-2001 significantly enhanced Verilog-1995 arrays by

allowing any variable or net type except the event type to be declared as an array, and by allowing multi-dimensional arrays. Beginning with Verilog-2001, both variable types and net types can be used in arrays.

```

// a 1-dimensional unpacked array of

// 1024 1-bit nets

wire n [0:1023];

// a 1-dimensional unpacked array of

// 256 8-bit variables

reg [7:0] LUT [0:255];

// a 1-dimensional unpacked array of

// 1024 real variables

real r [0:1023];

```

Verilog restricts the access to arrays to just one element of the array at a time, or a bitselect or part-select of a single element. Any reading or writing to multiple elements of an array is an error.

```

integer i [7:0][3:0][7:0];

integer j;

j = i[3][0][1]; // legal: selects 1 element

j = i[3][0]; // illegal: selects 8 elements

```

SystemVerilog refers to the Verilog style of array declarations as unpacked arrays. With unpacked arrays, each element of the array may be stored independently from other elements, but grouped under a common array name. Verilog does not define how software tools should store the elements in the array. For example, given an array of 8-bit wide elements, a simulator or other software tool might store each 8-bit element in 32-bit words.

SystemVerilog extends unpacked array dimensions to include the Verilog event type, and the SystemVerilog types: logic, bit, byte, int, longint, shortreal, and real. Unpacked arrays of user-defined types defined using typedef can also be declared, including types using struct and enum.

```

bit [63:0] d_array [1:128]; // array of vectors

shortreal cosines [0:89]; // array of floats

typedef enum {Mo, Tu, We, Th, Fr, Sa, Su} Week;

Week Year [1:52]; // array of Week types

```

SystemVerilog also adds to Verilog the ability to reference an entire unpacked array, or a slice of multiple elements within an unpacked array. A slice is one or more contiguously numbered elements within one dimension of an array. These enhancements make it possible to copy the contents of an entire array, or a specific dimension of an array into another array.

In order to directly copy multiple elements into an unpacked array, the layout and element type of the array or array slice on the lefthand side of the assignment must exactly match

the layout and element type of the right-hand side. That is, the element type and size and the number of dimensions copied must be the same.

### 2.12.2 Packed arrays

The Verilog language allows vectors to be created out of single-bit types, such as reg and wire. The vector range comes before the signal name, whereas an unpacked array range comes after the signal name.

SystemVerilog refers to vector declarations as packed arrays. A Verilog vector is a onedimensional packed array.

```

wire [3:0] select; // 4-bit "packed array"

reg [63:0] data; // 64-bit "packed array"

```

SystemVerilog adds the ability to declare multiple dimensions in a packed array.

logic [3:0][7:0] data; // 2-D packed array

SystemVerilog defines how the elements of a packed array are stored. The entire array must be stored as contiguous bits, which is the same as a vector. Each dimension of a packed array is a sub field within the vector. In the packed array declaration above, there is an array of 4 8-bit sub-arrays.

SystemVerilog also adds dynamic array types to Verilog:

- Dynamic arrays

- Associative arrays

- Sparse arrays

- Strings (character arrays)

Dynamically sized arrays are not synthesizable, and are intended for use in verification routines and for modeling at very high levels of abstraction.

### 2.13 Tasks and Functions:

SystemVerilog makes several enhancements to Verilog tasks and functions. These enhancements make it easier to model large designs in an efficient and intuitive manner.

### 2.13.1 Implicit task and function statement grouping:

In Verilog, multiple statements within a task or function must be grouped using begin...end. Tasks also allow multiple statements to be grouped using fork...join. SystemVerilog simplifies task and function definitions by not requiring the begin...end grouping for multiple statements. If the grouping is omitted, multiple statements within a task or function are executed sequentially, as if within a begin...end block.

```

function states_t NextState(states_t State);

NextState = State; // default next state

case (State)

WAITE: if (start) NextState = LOAD;

LOAD: if (done) NextState = STORE;

STORE: NextState = WAITE;

endcase

endfunction

```

### 2.13.2 Returning function values

In Verilog, the function name itself is an inferred variable that is the same type as the function. The return value of a function is set by assigning a value to the name of the function. A function exits when the execution flow reaches the end of the function. The last value that was written into the inferred variable of the name of function is the value returned by the function.

```

function [31:0] add_and_inc (input [31:0] a,b);

begin

add_and_inc = a + b + 1;

end

endfunction

```

System Verilog adds a **return** statement, which allows functions to return a value using **return**, as in C.

```

function int add_and_inc (input int a, b);

return a + b + 1;

endfunction

```

To maintain backward compatibility with Verilog, the return value of a function can be specified using either the return statement or by assigning to the function name. The return statement takes precedence. If a return statement is executed, that is the value returned. If the end of the function is reached without executing a return statement, then the last value assigned to the function name is the return value, as it is in Verilog. Even when using the return statement, the name of the function is still an inferred variable, and can be used as temporary storage before executing the return statement. For example:

```

function int add_and_inc (input int a, b);

add_and_inc = a + b;

return ++add_and_inc;

endfunction

```

### 2.13.3 Returning before the end of tasks and functions

In Verilog, a task or function exits when the execution flow reaches the end, which is denoted by endtask or endfunction. In order to exit before the end a task or function is reached using Verilog, conditional statements such as if...else must be used to force the execution flow to jump to the end of the task or function. A task can also be forced to jump to its end using the disable keyword, but this will affect all currently running invocations of a re-entrant task. The following example requires extra coding to prevent executing the function if the input to the function is less than or equal to 1.

```

function automatic int log2 (input int n);

if (n <=1)

log2 = 1;

else begin // skip this code when n<=1

log2 = 0;

while (n > 1) begin

n = n/2;

log2 = log2+1;

end

end

end

end

```

The SystemVerilog return statement can be used to exit a task or function at any time in the execution flow, without having to reach the end of the task or function. Using return, the example above can be simplified as follows:

```

function automatic int log2 (input int n);

if (n <=1) return 1; // abort function

log2 = 0;

while (n > 1) begin

n = n/2;

log2++;

end

endfunction

```

Using return to exit a task or function before the end is reached can simplify the coding within the task or function, and make the execution flow more intuitive and readable

### 2.13.4 Named task and function ends

SystemVerilog allows a name to be specified with the endtask or endfunction keyword. The syntax is:

```

endtask : <task_name>

endfunction : <function_name>

```

The white space before and after the colon is optional. The name specified must be the same as the name of the corresponding task or function. For example:

```

function int add_and_inc (int a, b);

return a + b + 1;

endfunction : add_and_inc

task automatic check_results (

input packet_t sent,

ref packet_t received,

ref logic done );

static int error_count;

...

endtask: check_results

```

Specifying a name with the endtask or endfunction keyword can help make large blocks of code easier to read, thus making the model more maintainable.

# 2.13.5 Empty tasks and functions

Verilog requires that tasks and functions contain at least one statement (which can be an empty begin...end statement group). SystemVerilog allows tasks and functions to be completely empty, with no statements or statement groups at all. An empty function will return the current value of the implicit variable that represents the name of the function. An empty task or function is a place holder for partially completed code. In a top-down design flow, creating an empty task or function can serve as documentation in a model for the place where more detailed functionality will be filled in later in the design flow.

# **Reference Books:**

- 1. Advanced Digital Design With the Verilog HDL, Michael D. Ciletti, 2nd Edition, PHI, ISBN: 978-0-07-338054-4 2015.

- 2. Digital Systems Design Using Verilog, Charles Roth, Lizy K. John, Byeong KilLee, Cengage Learning, ISBN-10: 1285051076, 2015.

- 3. Fundamentals of Digital Logic with Verilog Design, Stephen Brown and Zvonko Vranesic, 6th Edition, McGraw Hill publication, ISBN: 978–0–07–338054–4, 2014.

- System Verilog for Design A Guide to Using System Verilog for Hardware Design and Modeling, Stuart Sutherland, Simon David mann and Peter Flake, 2E, Springer Science, ISBN-13: 978-0387-3339-91, 2006.

- 5. System Verilog for Verification-A Guide to Learning the Testbench Language Features, C Spear, Springer Science, IEEE press, ISBN-13: 978-0387-2703-64,2006.

- 6. System Verilog golden reference guide-A concise guide to System Verilog Doulos, IEEE Standard-1800- 2009, Version 5.0,ISBN: 0-9547345-9-9, 2012.

- 7. Step-by-Step Functional Verification with System Verilog and OVM, SasanIman, Hansen Brown Publishing Company, ISBN-13: 978-0-9816-5621-2, 2008.

# **Questions to Practice:**

# PART -A

- 1 Identify how System Verilog is going to be a trendsetter in VLSI Industry

- 2 Identify the data types and its functions.

- 3 Describe in detail about static casting

- 4 Classify the use cases of arrays in System Verilog

- 5 Explain in detail about Empty Tasks and Functions

# PART-B

- 1 With the advent of VLSI Industry, Demonstrate how industry experts define the support of System Verilog

- 2 Classify how Data Types are used in System Verilog

- 3 Demonstrate in detail about the User defined Data Types

- 4 Demonstrate in detail about the impact of tasks and Functions in System Verilog

- 5 Enumerate Packed and Unpacked Arrays in detail.

# SCHOOL OF ELECTRICAL AND ELECTRONICS

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

**UNIT – III – CONNECTING THE TESTBENCH AND DESIGN– SECA3021**