# SCHOOL OF ELECTRICAL AND ELECTRONICS DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

UNIT - I Electronic Circuits-SECA1305

### **1.1 INTRODUCTION**

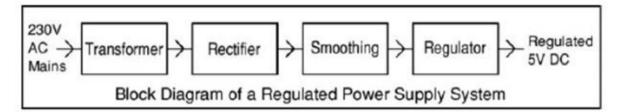

For the operation of most of the electronics devices and circuits, a d.c. source is required. So it is advantageous to convert domestic a.c. supply into d.c.voltages. The process of converting a.c. voltage into d.c. voltage is called as rectification. This is achieved with i) Step-down Transformer, ii) Rectifier,iii) Filter and iv) Voltage regulator circuits. These elements constitute d.c. regulated power supply shown in the Fig 1 below

Fig 1.1Block Diagram of regulated D.C Power Supply

- ✓ Transformer steps down 230V AC mains to low voltage AC.

- $\checkmark$  Rectifier converts AC to DC, but the DC output is varying.

- $\checkmark$  Smoothing smooth the DC from varying greatly to a small ripple.

- $\checkmark$  Regulator eliminates ripple by setting DC output to a fixed voltage.

The block diagram of a regulated D.C. power supply consists of step-down transformer, rectifier, filter, voltage regulator and load. An ideal regulated power supply is an electronics circuit designed to provide a predetermined d.c. voltage Vo which is independent of the load current and variations in the input voltage ad temperature. If the output of a regulator circuit is a AC voltage then it is termed as voltage stabilizer, whereas if the output is a DC voltage then it is termed as voltage regulator.

## **1.2 RECTIFIER**

Any electrical device which offers a low resistance to the current in one direction but a high resistance to the current in the opposite direction is called rectifier. Such a device is capable of converting a sinusoidal input waveform, whose average value is zero, into a unidirectional Waveform, with a nonzero average component. A rectifier is a device, which converts a.c. voltage (bi-directional) to pulsating d.c. voltage (Unidirectional).

### **1.2.1** Characteristics of a Rectifier Circuit:

Any electrical device which offers a low resistance to the current in one direction but a high resistance to the current in the opposite direction is called rectifier. Such a device is capable of converting a sinusoidal input waveform, whose average value is zero, into a unidirectional waveform, with a nonzero average component.

A rectifier is a device, which converts a.c. voltage (bi-directional) to pulsating d.c..Load currents: They are two types of output current. They are average or d.c. current and RMS currents.

Average or DC current: The average current of a periodic function is defined as the area of one cycle of the curve divided by the base. It is expressed mathematically as

i) Average value/dc value/mean value= Total time period/Area over one period

$$V_{dc} = \frac{1}{T} \int_{0}^{T} V d(wt)$$

**Effective (or) R.M.S current:** The effective (or) R.M.S. current squared of a periodic function of time is given by the area of one cycle of the curve, which represents the square of the function divided by the base.

$$V_{rms} = \sqrt{\frac{1}{T} \int_{0}^{T} V^2 d(wt)}$$

Peak factor: It is the ratio of peak value to RMS value

Form factor: It is the ratio of RMS value to average value

**Ripple Factor**: It is defined as ratio of R.M.S. value of a.c. component to the d.c. component in the output is known as "Ripple Factor".

$$\Gamma = \frac{V_{ac}}{V_{dc}}$$

$$V_{ac} = \sqrt{V_{rms}^2 - V_{dc}^2}$$

**Efficiency:** It is the ratio of d.c output power to the a.c. input power. It signifies, how efficiently the rectifier circuit converts a.c. power into d.c. power.

$$\eta = \frac{o / p \text{ power}}{i / p \text{ power}}$$

**Peak Inverse Voltage (PIV):** It is defined as the maximum reverse voltage that a diode can withstand without destroying the junction.

**Transformer Utilization Factor (UTF):**The d.c. power to be delivered to the load in a rectifier circuit decides the rating of the Transformer used in the circuit. So, transformer utilization factor is defined as

$$TUF = \frac{P_{dc}}{p_{ac(rated)}}$$

**% Regulation:** The variation of the d.c. output voltage as a function of d.c. load current is called regulation. The percentage regulation is defined as

## **1.3 CLASSIFICATION OF RECTIFIERS**

Using one or more diodes in the circuit, following rectifier circuits can be designed.

- 1) Half Wave Rectifier

- 2) Full Wave Rectifier

- 3) Bridge Rectifier

## **1.3.1 HALF-WAVE RECTIFIER:**

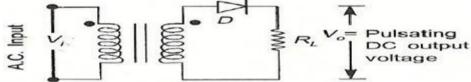

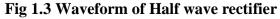

A Half – wave rectifier as shown in **fig 1.2** is one, which converts a.c. voltage into a pulsating voltage using only one half cycle of the applied a.c. voltage.

#### Fig 1.2 Half wave rectifier

The a.c. voltage is applied to the rectifier circuit using step-down transformer-rectifying element i.e., pn junction diode and the source of a.c. voltage, all connected is series. The a.c. voltage is applied to the rectifier circuit using step-down transformer

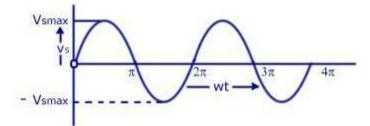

Let V=Vm sin (wt) The input to the rectifier circuit, Where Vm is the peak value of secondary a.c. voltage.

# 1.3.1.1 Operation:

For the positive half-cycle of input a.c. voltage, the diode D is forward biased and hence it conducts. Now a current flows in the circuit and there is a voltage drop across RL. The waveform of the diode current (or) load current is shown in fig 3. For the negative half-cycle of input, the diode D is reverse biased and hence it does not Conduct. Now no current flows in the circuit i.e., i=0 and Vo=0. Thus for the negative half-cycle no power is delivered to the load.

# 1.3.1.2 Analysis:

In the analysis of a HWR, the following parameters are to be analyzed.

- 1. DC output current

- 2. DC Output voltage

- 3. R.M.S. Current

- 4. R.M.S. voltage

- 5. Rectifier Efficiency  $(\eta)$

- 6. Ripple factor ( $\gamma$ ) 7. Peak Factor

- 8. % Regulation

- 9. Transformer Utilization Factor (TUF)

- 10. form factor

- 11. o/p frequency

Let a sinusoidal voltage Vi be applied to the input of the rectifier.

Then V=Vm sin (wt) Where Vm is the maximum value of the secondary voltage. Let the diode be idealized to piece-wise linear approximation with resistance Rf in the forward direction i.e., in the ON state and Rr (= $\infty$ ) in the reverse direction i.e., in the OFF state. Now the current 'i' in the diode (or) in the load resistance RL is given by V=Vm sin (wt)

#### i) AVERAGE VOLTAGE

$$V_{dc} = \frac{1}{T} \int_{0}^{T} V d(wt)$$

$$V_{dc} = \frac{1}{T} \int_{0}^{2\Pi} V(\alpha) d\alpha$$

$$V_{dc} = \frac{1}{2\Pi} \int_{\Pi}^{2\Pi} V(\alpha) d\alpha$$

$$V_{dc} = \frac{1}{2\Pi} \int_{0}^{2\Pi} V_m \sin(wt)$$

$$V_{dc} = \frac{V_m}{\Pi}$$

ii).AVERAGE CURRENT:

$$I_{dc} = \frac{I_m}{\Pi}$$

iii) <u>RMS VOLTAGE</u>:

$$V_{rms} = \sqrt{\frac{1}{T} \int_{0}^{T} V^{2} d(wt)}$$

$$V_{rms} = \sqrt{\frac{1}{2\Pi} \int_{0}^{2\Pi} (V_{m} sim(wt))^{2} d(wt)}$$

$$V_{rms} = \frac{V_m}{2}$$

IV) RMS CURRENT

$$I_{rms} = \frac{I_m}{\Pi}$$

V) PEAK FACTOR

$$Peak factor = \frac{peakvalue}{rmsvalue}$$

Peak Factor =

$$\frac{V_m}{(V_m/2)}$$

#### Peak Factor =2

# vi) FORM FACTOR

Form factor= $\frac{Rmsvalue}{averagevalue}$

Form factor=

$$\frac{(V_m/2)}{V_m/\Pi}$$

Form Factor =1.57

vii) Ripple Factor:

$$\Gamma = \frac{V_{ac}}{V_{dc}}$$

$$V_{ac} = \sqrt{V_{rms}^2 - V_{dc}^2}$$

$$\Gamma = \frac{\sqrt{V_{rms}^2 - V_{dc}^2}}{V_{ac}}$$

$$\Gamma = \sqrt{\frac{V_{rms}^2}{V_{dc}^2}} - 1$$

$$\Gamma = 1.21$$

viii) Efficiency ( $\eta$ ):

$$\eta = \frac{o / ppower}{i / ppower} *100$$

$$\eta = \frac{p_{ac}}{P_{dc}} *100$$

$\eta = 40.8$

## Ix ) Transformer Utilization Factor (TUF):

The d.c. power to be delivered to the load in a rectifier circuit decides the rating of the transformer used in the circuit. Therefore, transformer utilization factor is given as TUF =0.286. The value of TUF is low which shows that in half-wave circuit, the transformer is not fully utilized. If the transformer rating is 1 KVA (1000VA) then the half-wave rectifier can deliver 1000 X 0.287 = 287 watts to resistance load.

**x**) **Peak Inverse Voltage (PIV):** It is defined as the maximum reverse voltage that a diode can withstand without destroying the junction. The peak inverse voltage across a diode is the peak of the negative half- cycle. For half-wave rectifier, PIV is Vm.

## **1.3.1.3 DISADVANTAGES OF HALF-WAVE RECTIFIER:**

1. The ripple factor is high.

- 2. The efficiency is low.

- 3. The Transformer Utilization factor is low.

Because of all these disadvantages, the half-wave rectifier circuit is normally not used as a power rectifier circuit.

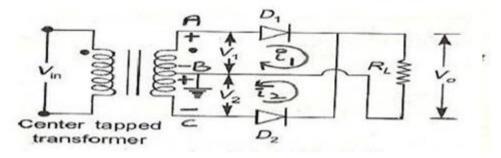

## **1.3.2.1 FULL WAVE RECTIFIER:**

A full-wave rectifier converts an ac voltage into a pulsating dc voltage using both half cycles of the applied ac voltage. In order to rectify both the half cycles of ac input, two diodes are used in this circuit. The diodes feed a common load RL with the help of a center-tap transformer. A center-tap transformer is the one, which produces two sinusoidal waveforms of same magnitude and frequency but out of phase with respect to the ground in the secondary winding of the transformer. The full wave rectifier is shown in the **Fig 1.4** below

Fig 1.4 Full wave rectifier

Fig. 1.5 shows the input and output wave forms of the ckt. During positive half of the input signal, anode of diode D1 becomes positive and at the same time the anode of diode D2 becomes negative. Hence D1 conducts and D2 does not conduct. The load current flows through D1 and the voltage drop across RL will be equal to the input voltage.

During the negative half cycle of the input, the anode of D1 becomes negative and the anode of D2 becomes positive. Hence, D1 does not conduct and D2 conducts. The load current flows through D2 and the voltage drop across RL will be equal to the input voltage. It is noted that the load current flows in the both the half cycles of ac voltage and in the same direction through the load resistance.

## a. AVERAGE VOLTAGE

$$V_{dc} = I_{dc}.R_L = \frac{2 \mathbf{I}_m}{\pi}.R_L \quad \text{We know } \mathbf{I}_m = \frac{V_m}{R_s + R_f + R_L}$$

$$\therefore V_{dc} = \frac{2.V_m R_L}{\pi(R_s + R_f + R_L)}$$

$$If(R_s + R_f) << R_L$$

$$V_{dc} = \frac{2V_m}{\pi} = 0.637 V_m.$$

## **b. AVERAGE CURRENT**

$$\frac{1}{2\pi} \int_{0}^{2\pi} i d\theta = \frac{1}{2\pi} \int_{0}^{2\pi} \mathbf{I}_{m} \sin \theta d\theta$$

$$= \frac{\mathbf{I}_{m}}{2\pi} \left[ \int_{0}^{\pi} \sin \theta d\theta - \int_{\pi}^{2\pi} \sin \theta d\theta \right]$$

$$= \frac{\mathbf{I}_{m}}{2\pi} \left[ (-2)(-2) \right]$$

$$= \frac{\mathbf{I}_{m}}{2\pi} \cdot 4 = \frac{2\mathbf{I}_{m}}{\pi} = 0.637 \, \mathbf{I}_{m} \, .$$

$$\mathbf{I}_{dc} = 0.637 \, \mathbf{I}_{m} \, .$$

$\therefore$  I<sub>DC</sub> FWR = 2 I<sub>DC</sub> HWR.

## **RMS VOLTAGE:**

$$\mathcal{V}_{rms} = \sqrt{\frac{1}{T}} \int_{0}^{T} \mathcal{V}^{2} d(wt)$$

$$\mathcal{V}_{rms} = \sqrt{\frac{1}{2\Pi}} \int_{0}^{2\Pi} (\mathcal{V}_{m} sim(wt))^{2} d(wt)$$

$$\mathcal{V}_{rms} = \frac{\mathcal{V}_{m}}{\sqrt{2}}$$

## IV) RMS CURRENT

V) PEAK FACTOR

Peak factor =  $\frac{peakvalue}{rmsvalue}$

Peak Factor =

$$\frac{V_m}{(V_m/2)}$$

Peak Factor =2

vi) FORM FACTOR

Form factor= Rms value average value

Form factor=

$$\frac{(V_m / \sqrt{2})}{2V_m / \Pi}$$

Form Factor =1.11

vii) Ripple Factor:

$$\gamma = \sqrt{\left(\frac{I_{max}}{I_{dc}}\right)^2 - 1}$$

for EWR.

$$I_{max} = \frac{I_m}{\sqrt{22}} \quad & I_{toc} = \frac{2I_m}{\pi}$$

$$\therefore \gamma_{FWR} = \sqrt{\left(\frac{I_m}{\sqrt{2}}\right)^2 - 1}$$

$$= \sqrt{\left(\frac{2\sqrt{2}}{\sqrt{2}}\right)^2 - 1}$$

$$= \sqrt{\left(\frac{2\sqrt{2}}{\sqrt{2}}\right)^2 - 1}$$

$$= \sqrt{\left(\frac{2\sqrt{2}}{\sqrt{2}}\right)^2 - 1} = 0.483$$

viii) Efficiency (77):

$$\eta = \frac{o / ppower}{i / ppower} *100$$

$$\begin{split} \eta &= \frac{P_{dc}}{p_{ac}} \times 100\% \\ \text{For FWR, } p_{de} &= I_{de}^2 . R_L = \left(\frac{2}{\pi} . \mathbf{I}_m\right)^2 . R_L \\ \mathbf{P}_{ac} &= \mathbf{I}^2_{\text{rms}} \left(\mathbf{R}_f + \mathbf{R}_S + \mathbf{R}_L\right) \\ &\left(\frac{\mathbf{I}_m}{\sqrt{2}}\right)^2 \left(R_f + R_S + R_L\right) \\ &\left(\frac{1}{\sqrt{2}}\frac{\mathbf{I}^2 m^2}{2} . (R_f + R_s + R_L)\right) \\ &If\left(R_f + R_S\right) < R_L \\ &\eta &= \frac{4}{\pi^2} . \frac{2}{1} = \frac{8}{\pi^2} = 0.812 = 81.2\% \end{split}$$

#### ix) Transformer Utilization Factor (TUF):

The d.c. power to be delivered to the load in a rectifier circuit decides the rating of the transformer used in the circuit. So,

a) TUF (Secondary) =  $\frac{P_{dc} \text{ delivered to load}}{AC \text{ power rating of transformer secondary}}$ b) Since both the windings are used TUF FWR = 2 TUF HWR = 2 x 0.287 = 0.574 c) TUF primary = Rated efficiency =  $\frac{P_{dc}}{P_{ac}} \times 100 = 81.2\%$ d) Average =  $\frac{0.812 + 0.574}{2} = 0.693$

#### x) Peak Inverse Voltage (PIV):

It is defined as the maximum reverse voltage that a diode can withstand without destroying the junction. The peak inverse voltage across a diode is the peak of the negative half- cycle. For half- wave rectifier, PIV is 2Vm

xi) % Regulation

Voltage regulation =

=

$$\frac{I_{dc}(R_s + R_f)}{\frac{2V_m}{\pi} - I_{DC}(R_f + R_s)}$$

## Advantages

- 1) Ripple factor = 0.482 (against 1.21 for HWR)

- 2) Rectification efficiency is 0.812 (against 0.405 for HWR)

- 3) Better TUF (secondary) is 0.574 (0.287 for HWR)

- 4) No core saturation problem

Disadvantages:

1) Requires center tapped transformer.

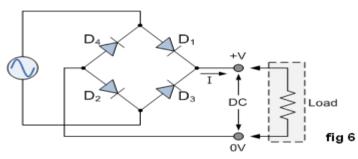

## **1.3.3 BRIDGE RECTIFIER.**

Another type of circuit that produces the same output waveform as the full wave rectifier circuit above, is that of the Full Wave Bridge Rectifier. This type of single phase rectifier uses four individual rectifying diodes connected in a closed loop "bridge" configuration to produce the desired output. The main advantage of this bridge circuit is that it does not require a special centre tapped transformer, thereby reducing its size and cost. The single secondary winding is connected to one side of the diode bridge network and the load to the other side as shown below.

Fig 1.6 Bridge rectifier

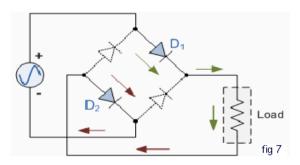

The four diodes labelled D1 to D4 are arranged in "series pairs" with only two diodes conducting current during each half cycle. During the positive half cycle of the supply, diodes D1 and D2 conduct in series while diodes D3 and D4 are reverse biased and the current flows through the load as shown below (fig 7).

### The Positive Half-cycle

Fig 1.7 Bridge rectifier-positive half cycle

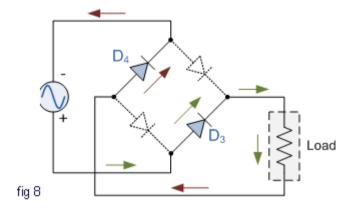

#### The Negative Half-cycle

During the negative half cycle of the supply, diodes D3 and D4 conduct in series (fig 8), but diodes D1 and D2 switch "OFF" as they are now reverse biased. The current flowing through the load is the same direction as before.

#### Fig 1.8 Bridge rectifier-positive half cycle

As the current flowing through the load is unidirectional, so the voltage developed across the load is also unidirectional the same as for the previous two diode full-wave rectifier, therefore the average DC voltage across the load is 0.637Vmax. However in reality, during each half cycle the current flows through two diodes instead of just one so the amplitude of the output voltage is two voltage drops ( $2 \ge 0.7 = 1.4V$ ) less than the input VMAX amplitude. The ripple frequency is now twice the supply frequency (e.g. 100Hz for a 50Hz supply) **2.3**

Therefore, the following expressions are same as that of full wave rectifier.

- a) Average current  $I_{dc} = \frac{2I_m}{\pi}$

- b) RMS current  $I_{max} = \frac{I_m}{\sqrt{2}}$

- c) DC output voltage (no.load)  $V_{DC} \frac{2V_m}{\pi}$

- d) Ripple factor  $\gamma = 0.482$

- e) Rectification efficiency =  $\eta = 0.812$

- f) DC output voltage full load.

=

$$V_{DCFL} = \frac{2V_m}{\pi} - I_{de}(R_s + 2R_f);$$

i.e., less by one diode loss.

TUF of both primary & secondary are 0.812 therefore TUF overall is 0.812 (better than FWR with 0.693)

| Con       | parison:                        |                                       |                                        |                                        |

|-----------|---------------------------------|---------------------------------------|----------------------------------------|----------------------------------------|

| SL<br>No. | Parameter                       | HWR                                   | FWR                                    | BR                                     |

| 1         | No. of diodes                   | 1                                     | 2                                      | 4                                      |

| 2         | PIV of diodes                   | Vm                                    | 2 V <sub>m</sub>                       | Vm                                     |

| 3         | Secondary voltage (rms)         | V                                     | V-0-V                                  | V                                      |

| 4         | DC output voltage at no load    | $\frac{V_m}{\pi} = 0.318 \text{ V}_m$ | $\frac{2V_m}{\pi} = 0.636 \text{ V}_m$ | $\frac{2V_m}{\pi} = 0.636 \text{ V}_m$ |

| 5         | Ripple factor y                 | 1.21                                  | 0.482                                  | 0.482                                  |

| 6         | Ripple frequency                | ſ                                     | 2f                                     | 2f                                     |

| 7         | Rectification efficiency $\eta$ | 0.406                                 | 0.812                                  | 0.812                                  |

| 8         | TUF                             | 0.287                                 | 0.693                                  | 0.812                                  |

#### **1.4 FILTERS**

The output of a rectifier contains dc component as well as ac component. Filters are used to minimize the undesirable ac i.e., ripple leaving only the dc component to appear at the output. Some important filters are:

- 1. Inductor filter

- 2. Capacitor filter

- 3. LC or L section filter

- 4. CLC or П-type filter

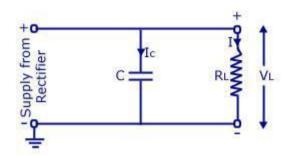

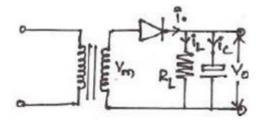

## **1.4.1 CAPACITOR FILTER**

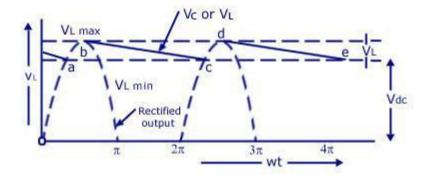

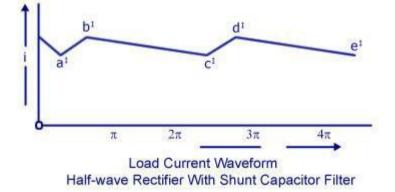

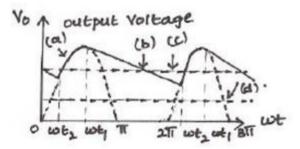

This is the most simple form of the **filter circuit** and in this arrangement a high value capacitor C is placed directly across the output terminals, as shown in figure. During the conduction period it gets charged and stores up energy to it during non-conduction period. Through this process, the time duration during which Ft is to be noted here that the capacitor C gets charged to the peak because there is no resistance (except the negligible forward resistance of diode) in the charging path. But the discharging time is quite large (roughly 100 times more than the charging time depending upon the value of RL) because it discharges through load resistance RL.

The function of the capacitor filter may be viewed in terms of impedances. The large value capacitor C offers a low impedance shunt path to the ac components or ripples but offers high impedance to the dc component. Thus ripples get bypassed through capacitor C and only dc component flows through the load resistance RL

Capacitor filter is very popular because of its low cost, small size, light weight and good characteristics.

Circuit Diagram

Input voltage Waveform to Rectifier

Rectified and filtered Output Voltage Waveform

Fig 1.9 Capacitor filter in Rectifiers

Cut In angle - wt2

Cut out angle =  $Wt_1$  $Wt_1 = \pi - \tan^{-1} WCR_L$

- (a) Capacitor charging through diode  $(Wt_2 Wt_1)$

- (b) Capacitor discharging through R<sub>L</sub> (Wt<sub>1</sub> to Wt<sub>2</sub>)

- (c) Average (DC) voltage with fitter

- (d) Average (DC) voltage without fitter.

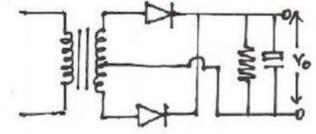

CAPACITOR FILTER WITH FWR

Fig 1.11 Capacitor Filter With FWR

Ripple freq  $_{FWR}$  = 2 ripple freq  $_{HWR}$ .

Concluding:

1.For a fixed-value filter capacitance larger the load resistance RL larger will be the discharge time constant CRL and therefore, lower the ripples and more the output voltage. On the other hand lower the load resistance (or more the load current), lower will be the output voltage.

2.Similarly smaller the filter capacitor, the less charge it can hold and more it will discharge. Thus the peak-to-peak value of the ripple will increase, and the average dc level will decrease. Larger the filter capacitor, the more charge it can hold and the less it will discharge. Hence the peak-to-peak value of the ripple will be less, and the average dc level will increase. But, the maximum value of the capacitance that can be employed is limited by another factor. The larger the capacitance value, the greater is the current required to charge the capacitor to a given voltage. The maximum current that can be handled by a diode is limited by the figure quoted by the manufacturer. Thus the maximum value of the capacitance, that can be used in the shunt filter capacitor is limited.

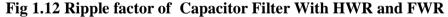

#### 1.4. 2 Series Inductor Filter.

Output Voltage Waveforms Fig 1.13. Full-Wave Rectifier With Series Inductor Filter

In this arrangement a high value inductor or choke L is connected in series with the rectifier element and the load, as illustrated in figure. The filtering action of an inductor filter depends upon its property of opposing any change in the current flowing through it. When the output current of the rectifier increases above a certain value, energy is stored in it in the form of magnetic field and this energy is given up when the output current falls below the average value. Thus by placing a choke coil in series with the rectifier output and load, any sudden change in current that might have occurred in the circuit without an inductor is smoothed out by the presence of the inductor L.

The function of the inductor filter may be viewed in terms of impedances. The choke offers high impedance to the ac components but offers almost zero resistance to the desired dc components. Thus ripples are removed to a large extent. Nature of the output voltage without filter and with choke filter is shown in figure.

For dc (zero frequency), the choke resistance Rc in series with the load resistance RL forms a voltage divider and dc voltage across the load is given as

where Vdc is dc voltage output from a full-wave rectifier. Usually choke coil resistance Rc, is much small than RL and, therefore, almost entire of the dc voltage is available across the load resistance RL.

Since the reactance of inductor increases with the increase in frequency, better filtering of the higher harmonic components takes place, so effect of third and higher harmonic voltages can be neglected.

As obvious from equation, if choke coil resistance Rc is negligible in comparison to load resistance RL, then the entire dc component of rectifier output is available across 2 RL and is equal to — VL max. The ac voltage partly drops across XL and partly over RL.

## 1.4 .3 L-SECTION FILTER:

A simple series inductor reduces both the peakand effective values of the output current and output voltage. On the other hand a simple **shunt capacitor filter** reduces the ripple voltage but increases the diode current. The diode may get damaged due to large current and at the same time it causes greater heating of supply transformer resulting in reduced efficiency.

In an inductor filter, ripple factor increases with the increase in load resistance RL while in a capacitor filter it varies inversely with load resistance RL. From economical point of view also, neither series inductor nor shunt capacitor type filters are suitable. Practical

**filter-circuits** are derived by combining the voltage stabilizing action of shunt capacitor with the current smoothing action of series choke coil. By using combination of inductor and capacitor ripple factor can be lowered, diode current can be restricted and simultaneously ripple factor can be made almost independent of load resistance (or load current). Two types of most commonly used combinations are choke-input or L-section filter-and capacitor-input or Pi-Filter.

### Choke-input filter is explained below:

Choke-input filter consists of a choke L connected in series with the rectifier and a capacitor C connected across the load. This is also sometimes called the L-section filter because in this arrangement inductor and capacitor are connected, as an inverted L. In figure only one filter

section is shown. But several identical sections are often employed to improve the smoothing action. (The choke L on the input side of the filter readily allows dc to pass but opposes the flow of ac components because its dc resistance is negligibly small but ac impedance is large. Any fluctuation that remains in the current even after passing through the choke are largely by-passed around the load by the shunt capacitor because Xc is much smaller than RL. Ripples can be reduced effectively by making XL greater than Xc at ripple frequency. However, a small ripple still remains in the filtered output and this is considered negligible if it than 1%. The rectified and filtered output voltage waveforms from a full-wave re with choke-input filter are shown in figure.

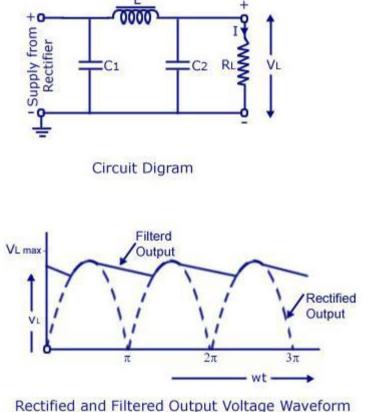

## **1.4.5 П-SECTION FILTER**:

Such a filter consists of a shunt capacitor C1 at the input followed by an L-section filter formed by series inductor L and shunt capacitor C2. This is also called the *n*-filter because the shape of the circuit diagram for this filter appears like Greek letter n (pi). Since the rectifier feeds directly into the capacitor so it is also called *capacitor input filter*. As the rectified output is fed directly into a capacitor C1. Such a filter can be used with a half-wave rectifier (series inductor and L-section filters cannot be used with half-wave rectifiers). Usually electrolytic capacitors are used even though their capacitances are large but they

occupy minimum space. Usually both capacitors C1 and C2 are enclosed in one metal container. The metal container serves as, the common ground for the two capacitors.

A capacitor-input or pi- filter is characterized by a high voltage output at low current drains. Such a filter is used, if, for a given transformer, higher voltage than that can be obtained from an L-section filter is required and if low ripple than that can be obtained from a shunt capacitor filter or L-section filter is desired. In this filter, the input capacitor C1 is selected to offer very low reactance to the ripple frequency. Hence major part of filtering is accomplished by the input capacitor C1. Most of the remaining ripple is removed by the L-section filter consisting of a choke L and capacitor C2.) The action of this filter can *best* be understood by considering the action of L-section filter, formed by L and C2, upon the triangular output voltage wave from the input capacitor C1 The charging and discharging action of input capacitor C1 less the dc voltage drop in inductor. The ripples contained in this output are reduced further by L-section filter. The output voltage of pi-filter falls off rapidly with the increase in load-current and, therefore, the voltage regulation with this filter is very poor.

## SALIENT FEATURES OF L-SECTION AND PI-FILTERS.

1. In pi-filter the dc output voltage is much larger than that can be had from an L-section filter with the same input voltage.

2.In pi-filter ripples are less in comparison to those in shunt capacitor or L-section filter. So smaller valued choke is required in a pi-filter in comparison to that required in L-section filter.

3.In pi-filter, the capacitor is to be charged to the peak value hence the rms current in supply transformer is larger as compared in case of L-section filter.

4.Voltage regulation in case of pi-filter is very poor, as already mentioned. So n-filters are suitable for fixed loads whereas L-section filters can work satisfactorily with varying loads provided a minimum current is maintained.

5.In case of a pi-filter PIV is larger than that in case of an L-section filter.

### **COMPARISON OF FILTERS**

1) A capacitor filter provides Vm volts at less load current. But regulation is poor.

2) An Inductor filter gives high ripple voltage for low load currents. It is used for high load currents

3) L – Section filter gives a ripple factor independent of load current. Voltage

21

Regulation can be improved by use of bleeder resistance

4) Multiple L – Section filter or  $\pi$  filters give much less ripple than the single L – Section Filter.

## 1.5 Voltage Regulator :

A **voltage regulator** is such a device that maintains constant output voltage, instead of any kind of fluctuations in the input voltage being applied or any variations in current, drawn by the load.

**Types of Regulators**

Regulators can be classified into different categories, depending upon their working and type of connection.

**Depending upon the type of regulation**, the regulators are mainly divided into two types namely, line and load regulators.

Ine Regulator – The regulator which regulates the output voltage to be constant, in spite of input line variations, it is called as Line regulator.

Icoad Regulator – The regulator which regulates the output voltage to be constant, in spite of the variations in load at the output, it is called as Load regulator.

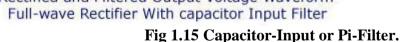

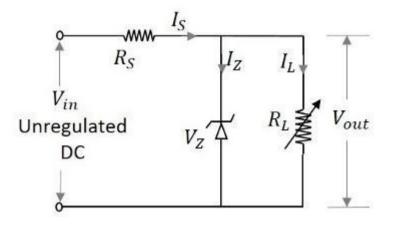

**Depending upon the type of connection**, there are two type of voltage regulators. They are 1.Series voltage regulator 2.Shunt voltage regulator. The arrangement of them in a circuit will be just as in the following figures.

Fig 1.16 Voltage regulator with arrangement

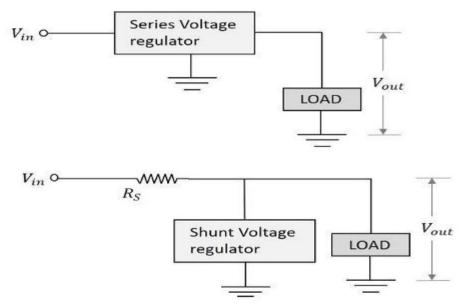

#### **1.5.1 Zener Voltage Regulator**

A Zener voltage regulator is one which uses Zener diode for regulating the output voltage. We have already discussed the details regarding Zener diode in BASIC ELECTRONICS tutorial. When the Zener diode is operated in the breakdown or **Zener region**, the voltage across it is substantially **constant** for a **large change of current** through it. This characteristic makes Zener diode a **good voltage regulator**.

The following figure shows an image of a simple Zener regulator.

Fig 1.17 Zener Voltage Regulator

The applied input voltage ViVi when increased beyond the Zener voltage VzVz, then the Zener diode operates in the breakdown region and maintains constant voltage across the load. The series limiting resistor RsRs limits the input current.

Working of Zener Voltage Regulator

The Zener diode maintains the voltage across it constant in spite of load variations and input voltage fluctuations. Hence we can consider 4 cases to understand the working of a Zener voltage regulator.

**Case 1** – If the load current ILIL increases, then the current through the Zener diode IZIZ decreases in order to maintain the current through the series resistor RSRS constant. The output voltage Vo depends upon the input voltage Vi and voltage across the series resistor RSRS. This is can be written as

Vo=Vin-IRsVo=Vin-IRs Where II is constant. Therefore, VoVo also remains constant.

Case 2 - If the load current ILIL decreases, then the current through the Zener diode IZIZ increases, as the current ISIS through RS series resistor remains constant. Though the current IZIZ through Zener diode increases it maintains a constant output voltage VZVZ, which maintains the load voltage constant.

**Case 3** – If the input voltage ViVi increases, then the current ISIS through the series resistor RS increases. This increases the voltage drop across the resistor, i.e. VSVS increases. Though the current through Zener diode IZIZ increases with this, the voltage across Zener diode VZVZ remains constant, keeping the output load voltage constant.

**Case 4** – If the input voltage decreases, the current through the series resistor decreases which makes the current through Zener diode IZIZ decreases. But the Zener diode maintains output voltage constant due to its property.

Limitations of Zener Voltage Regulator

There are a few limitations for a Zener voltage regulator. They are -

$\Box$  It is less efficient for heavy load currents.

□ The Zener impedance slightly affects the output voltage.

Hence a Zener voltage regulator is considered effective for low voltage applications. Now, let us go through the other types of voltage regulators, which are made using transistors.

#### **1.5.2 Transistor Series Voltage Regulator**

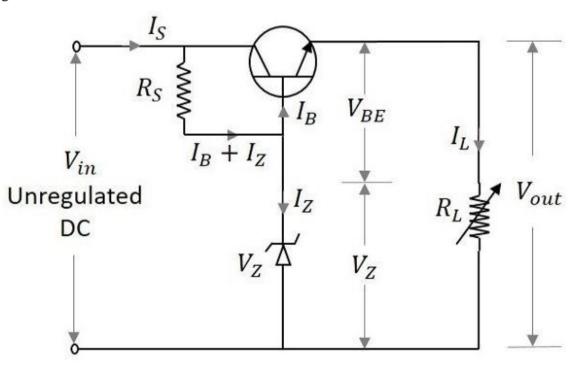

This regulator has a transistor in series to the Zener regulator and both in parallel to the load. The transistor works as a variable resistor regulating its collector emitter voltage in order to maintain the output voltage constant. The figure below shows the transistor series voltage regulator.

Fig 1.18 Transistor Series Voltage Regulator

With the input operating conditions, the current through the base of the transistor changes. This effects the voltage across the base emitter junction of the transistor VBEVBE. The output voltage is maintained by the Zener voltage VZVZ which is constant. As both of them are maintained equal, any change in the input supply is indicated by the change in emitter base voltage VBEVBE.

Hence the output voltage Vo can be understood as

$$V_0 = V_Z + V_{BE} V_0 = V_Z + V_{BE}$$

Working of Transistor Series Voltage Regulator

The working of a series voltage regulator shall be considered for input and load variations. If the input voltage is increased, the output voltage also increases. But this in turn makes the voltage across the collector base junction  $V_{BE}V_{BE}$  to decrease, as the Zener voltage remains constant. The conduction decreases as the resistance across emitter collector region increases. This further increases the voltage across collector emitter junction VCE thus reducing the output voltage V<sub>0</sub>. This will be similar when the input voltage decreases.

When the load changes occur, which means if the resistance of the load decreases, increasing the load current  $I_L$ , the output voltage  $V_O$  decreases, increasing the emitter base voltage  $V_{BE}$ .

With the increase in the emitter base voltage the conduction increases reducing the emitter collector resistance. This in turn increases the input current which compensates the decrease in the load resistance. This will be similar when the load current increases.

Limitations of Transistor Series Voltage Regulator

Transistor Series Voltage Regulators have the following limitations -

$\Box$  The voltages V<sub>BE</sub> and V<sub>Z</sub>V<sub>Z</sub> are affected by the rise in temperature.

- $\Box$  No good regulation for high currents is possible.

- $\square$  Power dissipation is high.

- $\square$  Power dissipation is high.

- $\Box$  Less efficient.

To minimize these limitations, transistor shunt regulator is used.

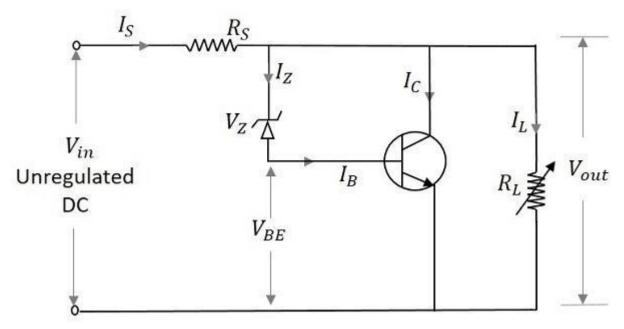

#### 1.5.3 Transistor Shunt Voltage Regulator

A transistor shunt regulator circuit is formed by connecting a resistor in series with the input and a transistor whose base and collector are connected by a Zener diode that regulates, both in parallel with the load. The figure below shows the circuit diagram of a transistor shunt regulator.

## Fig 1.19 Transistor Shunt Voltage Regulator 1.5.4 Working of Transistor Shunt Voltage Regulator

If the input voltage increases, the  $V_{BE}$  and  $V_O$  also gets increased. But this happens initially. Actually when  $V_{in}$  increases, the current also increases. This current when flows through RS, causes a voltage drop  $V_SVS$  across the series resistor, which also gets increased with  $V_{in}$ . But this makes  $V_O$  to decrease. Now this decrease in Vo compensates the initial increase maintaining it to be constant. Hence Vo is maintained constant. If the output voltage decreases instead, the reverse happens.

If the load resistance decreases, there should be decrease in the output voltage Vo. The current through the load increases. This makes the base current and collector current of the transistor to decrease. The voltage across the series resistor becomes low, as the current flows heavily. The input current will be constant.

The output voltage appears will be the difference between the applied voltage ViVi and the series voltage drop Vs. Hence the output voltage will be increased to compensate the initial decrease and hence maintained constant. The reverse happens if the load resistance increases.

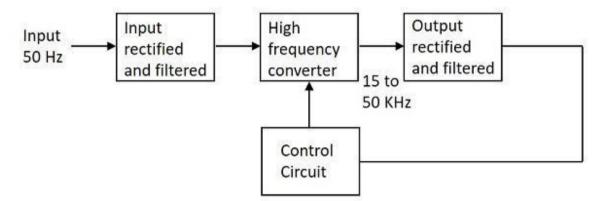

## **1.6 SWITCHED-MODE POWER SUPPLY**

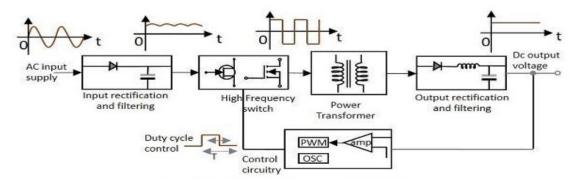

A switched-mode power supply (SMPS) is an electronic circuit that converts power using switching devices that are turned on and off at high frequencies, and storage components such as inductors or capacitors to supply power when the switching device is in its nonconduction state. Switching power supplies have high efficiency and are widely used in a variety of electronic equipment, including computers and other sensitive equipment requiring stable and efficient power supply.

A switched-mode power supply is also known as a switch-mode power supply or switchingmode power supply. Switched-mode power supplies are classified according to the type of input and output voltages. The four major categories are:

- AC to DC

- DC to DC

- DC to AC

- AC to AC

A basic isolated AC to DC switched-mode power supply consists of:

- Input rectifier and filter

- Inverter consisting of switching devices such as MOSFETs

- Transformer

- Output rectifier and filter

- Feedback and control circuit

Fig 1.20 Switched-Mode Power Supply

Input Stage

The AC input supply signal 50 Hz is given directly to the rectifier and filter circuit combination without using any transformer. This output will have many variations and the capacitance value of the capacitor should be higher to handle the input fluctuations. This unregulated dc is given to the central switching section of SMPS.

Switching Section

A fast switching device such as a Power transistor or a MOSFET is employed in this section, which switches ON and OFF according to the variations and this output is given to the primary of the transformer present in this section. The transformer used here are much smaller and lighter ones unlike the ones used for 60 Hz supply. These are much efficient and hence the power conversion ratio is higher.

Output Stage The output signal from the switching section is again rectified and filtered, to get the required DC voltage. This is a regulated output voltage which is then given to the control circuit, which is a feedback circuit. The final output is obtained after considering the feedback signal.

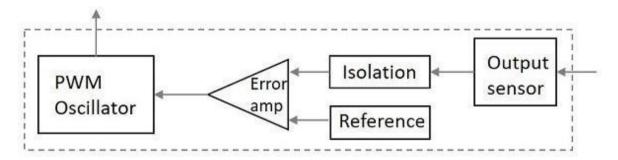

Control Unit This unit is the feedback circuit which has many sections. Let us have a clear understanding about this from The following figure.

## Fig 1.21 Control Unit

The above figure explains the inner parts of a control unit. The output sensor senses the signal and joins it to the control unit. The signal is isolated from the other section so that any sudden spikes should not affect the circuitry. A reference voltage is given as one input along with the signal to the error amplifier which is a comparator that compares the signal with the required signal level. By controlling the chopping frequency the final voltage level is maintained. This is controlled by comparing the inputs given to the error amplifier, whose output helps to decide whether to increase or decrease the chopping frequency. The PWM oscillator produces a standard PWM wave fixed frequency.

We can get a better idea on the complete functioning of SMPS by having a look at the following

28

The input DC supply from a rectifier or battery is fed to the inverter where it is turned on and off at high frequencies of between 20 KHz and 200 KHz by the switching MOSFET or power transistors. The high-frequency voltage pulses from the inverter are fed to the transformer primary winding, and the secondary AC output is rectified and smoothed to produce the required DC voltages. A feedback circuit monitors the output voltage and instructs the control circuit to adjust the duty cycle to maintain the output at the desired level.

The SMPS is mostly used where switching of voltages is not at all a problem and where efficiency of the system really matters. There are few points which are to be noted regarding SMPS. They are

- SMPS circuit is operated by switching and hence the voltages vary continuously.

- The switching device is operated in saturation or cut off mode.

- The output voltage is controlled by the switching time of the feedback circuitry.

- Switching time is adjusted by adjusting the duty cycle.

- The efficiency of SMPS is high because, instead of dissipating excess power as heat, it continuously switches its input to control the output.

#### Disadvantages

There are few disadvantages in SMPS, such as

- The noise is present due to high frequency switching.

- The circuit is complex.

- It produces electromagnetic interference.

## Advantages

The advantages of SMPS include,

- The efficiency is as high as 80 to 90%

- Less heat generation; less power wastage.

- Reduced harmonic feedback into the supply mains.

- The device is compact and small in size.

- The manufacturing cost is reduced.

- Provision for providing the required number of voltages.

Applications There are many applications of SMPS. They are used in the motherboard of computers, mobile phone chargers, HVDC measurements, battery chargers, central power distribution, motor vehicles, consumer electronics, laptops, security systems, space stations, etc.

## Types of SMPS

SMPS is the Switched Mode Power Supply circuit which is designed for obtaining the regulated DC output voltage from an unregulated DC or AC voltage. There are four main types of SMPS such as

- DC to DC Converter

- AC to DC Converter

- Fly back Converter

- Forward Converter

The AC to DC conversion part in the input section makes the difference between AC to DC converter and DC to DC converter. The Fly back converter is used for Low power applications. Also there are Buck Converter and Boost converter in the SMPS types which decrease or increase the output voltage depending upon the requirements. The other type of SMPS include Self-oscillating fly-back converter, Buck-boost converter, Cuk, Sepic, etc.

## **TEXT / REFERENCE BOOKS**

1. S Millman and Halkias, "Integrated Electronics", Tata McGraw Hill International, 2008.

2. R.L. Boylestad and L. Nashelsky, "Electronic Devices and Circuit Theory", PHI Learning Pvt. Ltd, India, 9th edition, 2008.

3. D.Roy Choudhury & Shail B Jain, "Linear Integrated Circuits", 3rd edition. 2007.

4. David. A. Bell, "Electronic Devices and Circuits", PHI Learning Private Ltd, India, 4th edition 2008.

5. R.A. Gayakwad, "Op-Amps and Linear integrated circuits", PHI, 2008.

# SCHOOL OF ELECTRICAL AND ELECTRONICS DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

UNIT - 2 Electronic Circuits-SECA1305

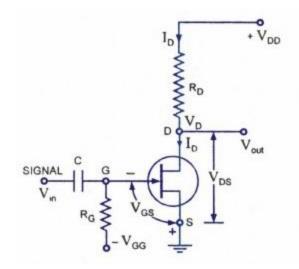

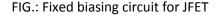

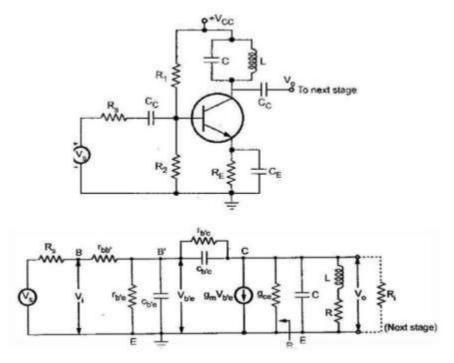

#### 2.1 NEED FOR TRANSISTOR BIASING

If the o/p signal must be a faithful reproduction of the i/p signal, the transistor must be operated in active region. That means an operating point has to be established in this region. To establish an operating point (proper values of collector current Ic and collector to emitter voltage VCE) appropriate supply voltages and resistances must be suitably chosen in the ckt. This process of selecting proper supply voltages and resistance for obtaining desired operating point or Q point is called as biasing and the ckt used for transistor biasing is called as biasing ckt.

There are four conditions to be met by a transistor so that it acts as a faithful ampr:

1) Emitter base junction must be forward biased (VBE=0.7Vfor Si, 0.2V for Ge) and collector base junction must be reverse biased for all levels of i/p signal.

2) Vce voltage should not fall below VCE (sat) (0.3V for Si, 0.1V for Ge) for any part of the i/p signal. For VCE less than VCE (sat) the collector base junction is not probably reverse biased.

3) The value of the signal Ic when no signal is applied should be at least equal to the max. collector current t due to signal alone.

4) Max. rating of the transistor Ic(max), VCE (max) and PD(max) should not be exceeded at any value of i/p signal.

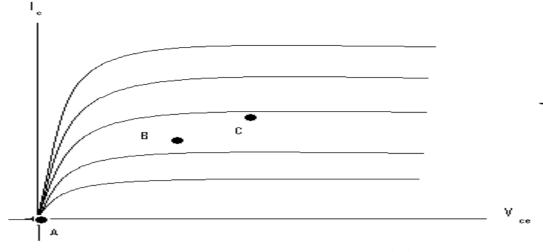

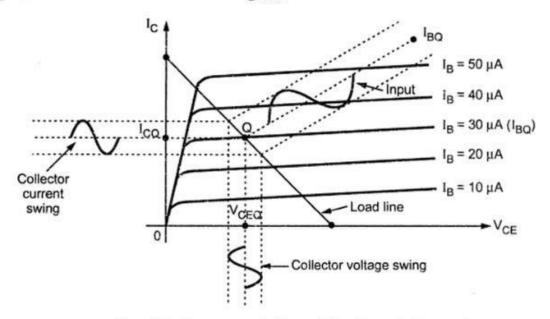

Consider the fig shown in fig1. If operating point is selected at A, A represents a condition when no bias is applied to the transistor i.e, Ic=0, VCE =0. It does not satisfy the above said conditions necessary for faithful amplification.

Point C is too close to PD(max) curve of the transistor. Therefore the o/p voltage swing in the positive direction is limited.

Point B is located in the middle of active region .It will allow both positive and negative half cycles in the o/p signal. It also provides linear gain and larger possible o/p voltages and currents. Hence operating point for a transistor amplifier is selected to be in the middle of active region.

Fig 2.1 Transistor output characteristics

#### **2.2 DC LOAD LINE**

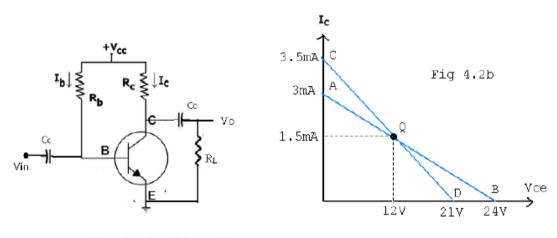

Referring to the biasing circuit of fig 4.2a, the values of VCC and RC are fixed and Ic and VCE are dependent on RB. Applying Kirchhoff's voltage law to the collector circuit in fig. 4.2a, we get

Vcc = IcRc + Vce

CE Amplifier circuit (b) Load line

#### Fig 2.2 DC load line

The straight line represented by AB in fig4.2b is called the dc load line. The coordinates of the end point A are obtained by substituting VCE =0 in the above equation. Therefore The coordinates of A are VCE =0 and the coordinates of B are obtained by substituting Ic=0 in the above equation. Then Vce = Vcc. Therefore the coordinates of B are VCE =Vcc and Ic=0. Thus the dc load line AB can be drawn if the values of Rc and Vcc are known.

As shown in the fig4.2b, the optimum POINT IS LOCATED AT THE MID POINT OF THE MIDWAY BETWEEN a AND b. In order to get faithful amplification, the Q point must be well within the active region of the transistor.

Even though the Q point is fixed properly, it is very important to ensure that the operating point remains stable where it is originally fixed. If the Q point shifts nearer to either A or B, the output voltage and current get clipped, thereby o/p signal is distorted.

In practice, the Q-point tends to shift its position due to any or all of the following three main factors.

1) Reverse saturation current, Ico, which doubles for every 10oC raise in temperature

2) Base emitter Voltage ,VBE, which decreases by 2.5 mV per oC

3) Transistor current gain, hFE or  $\beta$  which increases with temperature.

If base current IB is kept constant since IB is approximately equal to Vcc/RB. If the transistor is replaced by another one of the same type, one cannot ensure that the new transistor will have identical parameters as that of the first one. Parameters such as  $\beta$  vary over a range. This results in the variation of collector current Ic for a given IB. Hence , in the o/p characteristics, the spacing between the curves might increase or decrease which leads to the shifting of the Q-point to a location which might be completely unsatisfactory.

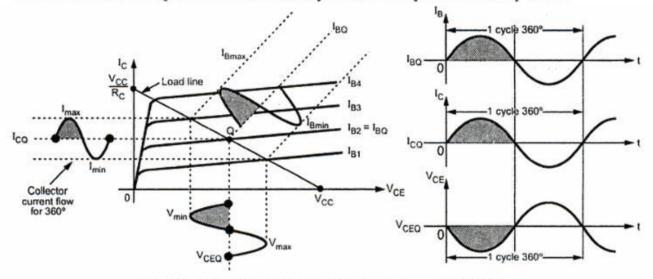

#### **2.3 AC LOAD LINE**

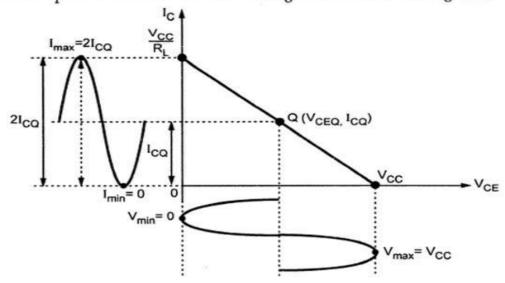

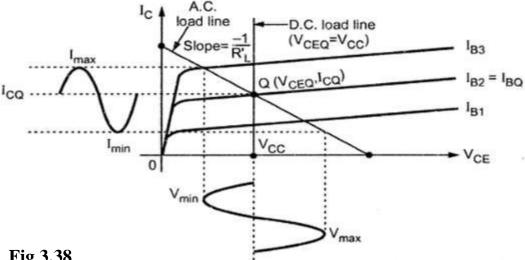

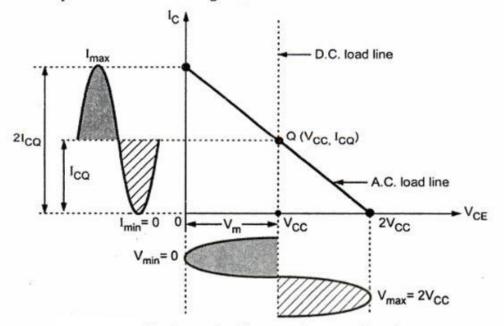

After drawing the dc load line, the operating point Q is properly located at the center of the dc load line. This operating point is chosen under zero input signal condition of the circuit. Hence the ac load line should also pas through the operating point Q. The effective ac load resistance Rac, is a combination of RC parallel to RL i.e. So the slope of the ac load line CQD. To draw the ac load line, two end points, I.e. VCE(max) and IC(max) when the signal is applied are required

$$V_{CE(\max)} = V_{CEQ} + I_{CQ}R_{ac}$$

, which locates point D on the Vce axis

$I_{c(\max)} = I_{CQ} + \frac{V_{CEQ}}{R_{ac}}$ , which locates the point C on the I<sub>c</sub> axis.

By joining points c and D, ac load line CD is constructed. As RC > Rac, The dc load line is less steep than ac load line.

#### 2.4 STABILITY FACTOR (S):

The rise of temperature results in increase in the value of transistor gain  $\beta$  and the leakage current Ico. So, IC also increases which results in a shift in operating point. Therefore, The biasing network should be provided with thermal stability. Maintenance of the operating

point is specified by S, which indicates the degree of change in operating point due to change in temperature.

The extent to which IC is stabilized with varying IC is measured by a stability factor S

$S = \frac{\partial I_c}{\partial I_{co}} \approx \frac{dI_c}{dI_{co}} \approx \frac{\Delta I_c}{\Delta I_{co}} \,_{*}\beta \text{ and } I_B \text{ constant}$

For CE configuration

$$I_c = \beta I_B + (1 + \beta) I_{cc}$$

Differentiate the above equation w.r.t I<sub>c</sub> , We get

$$1 = \beta \frac{dI_B}{dI_c} + (1+\beta) \frac{dI_{co}}{dI_c}$$

$$\therefore \quad \left(1 - \beta \frac{dI_B}{dI_c}\right) = \frac{(\beta+1)}{S}$$

$$\therefore \quad S = \frac{1+\beta}{1-\beta \frac{dI_B}{dI_c}}$$

S should be small to have better thermal stability.

#### Stability factor S' and S'':

S' is defined as the rate of change of  $~~I_{C}$  with  $V_{BE},$  keeping  $I_{C}$  and  $V_{BE}$  constant.

$$S' = \frac{\partial I_c}{\partial V_{BE}}$$

S'' is defined as the rate of change of  $I_c$  with  $\beta$ , keeping  $I_{co}$  and  $V_{BE}$  constant.

$$S'' = \frac{\partial I_c}{\partial \beta}$$

## **2.5 METHODS OF TRANSISTOR BIASING**

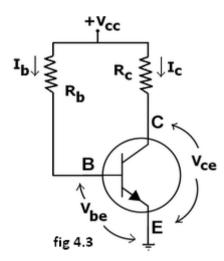

2.5.1 Fixed bias (base bias)

## Fig 2.3 Fixed Biasing Circuit

This form of biasing is also called *base bias*. In the fig 4.3 shown, the single power source (for example, a battery) is used for both collector and base of a transistor, although separate batteries can also be used. In the given circuit, Vcc = IBRB + Vbe. Therefore, IB = (Vcc - Vbe)/RB Since the equation is independent of current ICR, dIB//dICR = 0 and the stability

factor is given by the equation..... reduces to  $S=1+\beta$ . Since  $\beta$  is a large quantity, this is very poor biasing circuit. Therefore in practice the circuit is not used for biasing. For a given transistor, Vbe does not vary significantly during use. As Vcc is of fixed value, on selection of Rthe base current IB is fixed. Therefore this type is called *fixed bias* type of circuit. Also for given circuit, Vcc = ICRC + Vce Therefore, Vce = Vcc - ICRC

### Merits:

It is simple to shift the operating point anywhere in the active region by merely changing the base resistor (RB).

A very small number of components are required.

#### **Demerits:**

The collector current does not remain constant with variation in temperature or power supply voltage. Therefore the operating point is unstable.

Changes in Vbe will change IB and thus cause RE to change. This in turn will alter the gain of the stage.

When the transistor is replaced with another one, considerable change in the value of  $\beta$  can be expected. Due to this change the operating point will shift.

## 2.5.2 EMITTER-FEEDBACK BIAS:

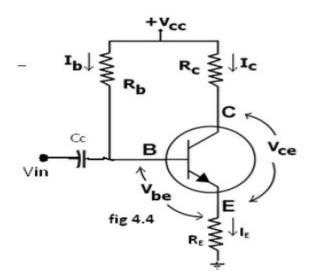

The emitter feedback bias circuit is shown in the fig 4.4. The fixed bias circuit is modified by attaching an external resistor to the emitter. This resistor introduces negative feedback that stabilizes the Q-point. From Kirchhoff's voltage law, the voltage across the base resistor is VRb = VCC - IeRe - Vbe. From Ohm's law, the base current is Ib = VRb / Rb.

The way feedback controls the bias point is as follows. If Vbe is held constant and temperature increases, emitter current increases. However, a larger le increases the emitter voltage Ve = leRe, which in turn reduces the voltage VRb across the base resistor. A lower base-resistor voltage drop reduces the base current, which results in less collector current because Ic =  $\beta$  IB. Collector current and emitter current are related by Ic =  $\alpha$  le with  $\alpha \approx 1$ , so increase in emitter current with temperature is opposed, and operating point is kept stable.

Similarly, if the transistor is replaced by another, there may be a change in IC (corresponding to change in  $\beta$ -value, for example). By similar process as above, the change is negated and operating point kept stable. For the given circuit, IB = (VCC - Vbe)/(RB + ( $\beta$ +1)RE).

#### **Merits:**

The circuit has the tendency to stabilize operating point against changes in temperature and  $\beta$ -value.

# **Demerits:**

In this circuit, to keep IC independent of  $\beta$  the following condition must be met:

$$I_{C} = \beta I_{B} = \frac{\beta (V_{CC} - V_{be})}{R_{B} + (\beta + 1)R_{E}} \approx \frac{(V_{CC} - V_{be})}{R_{E}}$$

which is approximately the case if ( $\beta + 1$ )R<sub>E</sub> >> R<sub>B</sub>.

large, or making RB very low. If RE is of large value, high VCC is necessary. This increases cost as well as precautions necessary while handling. If RB is low, a separate low voltage supply should be used in the base circuit. Using two supplies of different voltages is impractical. In addition to the above, RE causes ac feedback which reduces the voltage gain of the amplifier.

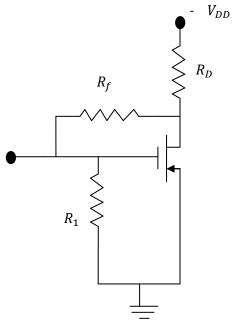

Fig 2.4 Self Biasing Circuit 2.5.3 COLLECTOR TO BASE BIAS OR COLLECTOR FEED-BACK BIAS:

Fig 2.5 Collector to Base Biasing Circuit

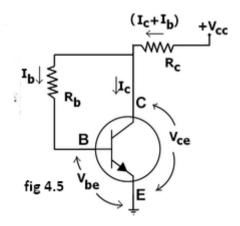

This configuration shown in fig 4.5 employs negative feedback to prevent thermal runaway and stabilize the operating point. In this form of biasing, the base resistor  $R_B$  is connected to the collector instead of connecting it to the DC source  $V_{cc}$ . So any thermal runaway will induce a voltage drop across the  $R_C$  resistor that will throttle the transistor's base current

From Kirchhoff's voltage law, the voltage  $V_{

m Rbacross}$  the base resistor  ${\it R_b}$  is

$V_{\rm R_b} = V_{\rm cc} - \underbrace{\overbrace{(I_{\rm c} + I_{\rm b})R_{\rm c}}^{\rm Voltage \ drop \ across \ R_{\rm c}}}_{\left(I_{\rm c} + I_{\rm b}\right)R_{\rm c}} - \underbrace{\overbrace{V_{\rm be}}^{\rm Voltage \ at \ base}}_{\left(I_{\rm be}\right)}$

By the Ebers–Moll model,  $I_c = \beta I_b$ , and so

$$V_{\rm R_b} = V_{\rm cc} - (\widehat{\beta I_{\rm b}} + I_{\rm b})R_{\rm c} - V_{\rm bc} = V_{\rm cc} - I_{\rm b}(\beta + 1)R_{\rm c} - V_{\rm bc}.$$

From Ohm's law, the base current  $I_{

m b} = V_{

m R_b}/R_{

m b}$  , and so

$$\overbrace{I_{\rm b}R_{\rm b}}^{V_{\rm R_{\rm b}}} = V_{\rm cc} - I_{\rm b}(\beta + 1)R_{\rm c} - V_{\rm be}.$$

Hence, the base current I<sub>b</sub> is

$$I_{\rm b} = \frac{V_{\rm cc} - V_{\rm be}}{R_{\rm b} + (\beta + 1)R_{\rm c}}$$

... ...

If

$$V$$

be is held constant and temperature increases, then the collector current  $I$ c increases.

However, a larger  $I$ c causes the voltage drop across resistor  $R$ c to increase, which in turn reduces the voltage

. .

across the base resistor Rb. A lower base-resistor voltage drop reduces the base current Ib, which results in less collector current Ic. Because an increase in collector current with temperature is opposed, the operating point is kept stable.

#### **Merits:**

Circuit stabilizes the operating point against variations in temperature and  $\beta$  (i.e. replacement of transistor)

#### **Demerits:**

In this circuit, to keep *I*c independent of  $\beta$ , the following condition must be met:

$$I_{\rm c} = \beta I_{\rm b} = \frac{\beta (V_{\rm cc} - V_{\rm be})}{R_{\rm b} + R_{\rm c} + \beta R_{\rm c}} \approx \frac{(V_{\rm cc} - V_{\rm be})}{R_{\rm c}}$$

which is the case when

$\beta R_{\rm c} \gg R_{\rm b}$ .

As  $\beta$ -value is fixed (and generally unknown) for a given transistor, this relation can be satisfied either by keeping *R*c fairly large or making *R*b very low.

If *R*c is large, a high *V*cc is necessary, which increases cost as well as precautions necessary while handling.

If *R*b is low, the reverse bias of the collector–base region is small, which limits the range of collector voltage swing that leaves the transistor in active mode.

The resistor Rb causes an AC feedback, reducing the voltage gain

of the amplifier. This undesirable effect is a trade-off for greater Q-point stability.

**Usage:** The feedback also decreases the input impedance of the amplifier as seen from the base, which can be advantageous. Due to the gain reduction from feedback, this biasing form is used only when the trade-off for stability is warranted.

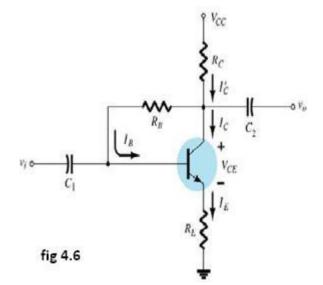

# 2.2.4 COLLECTOR – EMITTER FEEDBACK BIAS

Fig 2.6 Collector – Emitter Feedback Bias

The above fig2.2.4 shows the collector –emitter feedback bias circuit that can be obtained by applying both the collector feedback and emitter feedback. Here the collector feedback is provided by connecting a resistance RB from the collector to the base and emitter feedback is

provided by connecting an emitter Re from emitter to ground. Both feed backs are used to control collector current and base current IB in the opposite direction to increase the stability as compared to the previous biasing circuits.

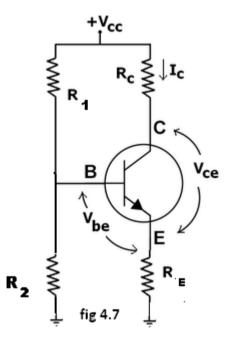

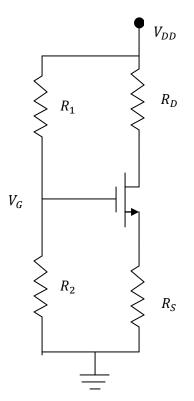

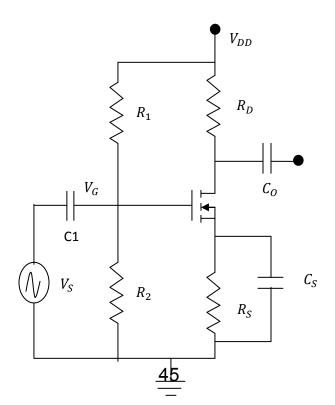

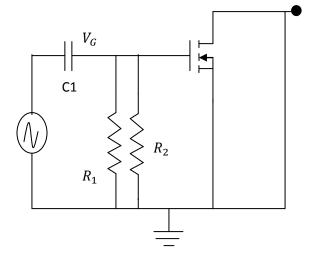

# 2.2.5 VOLTAGE DIVIDER BIAS OR SELF BIAS OR EMITTER BIAS

The voltage divider as shown in the fig 4.7 is formed using external resistors R1 and R2. The voltage across R2 forward biases the emitter junction. By proper selection of resistors R1 and R2, the operating point of the transistor can be made independent of  $\beta$ . In this circuit, the voltage divider holds the base voltage fixed independent of base current provided the divider current is large compared to the base current. However, even with a fixed base voltage, collector current varies with temperature (for example) so an emitter resistor is added to stabilize the Q-point, similar to the above circuits with emitter resistor.

Fig 2.7 Voltage Divider Biasing Circuit

In this circuit the base voltage is given by:

$$V_B =_{\text{voltage across } R_2} = V_{cc} \frac{R_2}{(R_1 + R_2)} - I_B \frac{R_1 R_2}{(R_1 + R_2)}$$

$$\approx V_{cc} \frac{R_2}{(R_1 + R_2)}_{\text{provided } I_B} << I_2 = V_B/R_2.$$

Also  $V_B = V_{be} + I_E R_E$

For the given circuit,

$$I_B = \frac{\frac{V_{CC}}{1+R_1/R_2} - V_{be}}{(\beta+1)R_E + R_1 \parallel R_2}$$

Let the current in resistor R1 is I1 and this is divided into two parts – current through base and resistor R2. Since the base current is very small so for all practical purpose it is assumed that I1 also flows through R2, so we have

$$I_{1} = \frac{V_{CC}}{R_{1} + R_{2}}$$

$$V_{2} = \frac{V_{CC}}{R_{1} + R_{2}} \cdot R_{2}$$

Applying KVL in the circuit, we have

$$V_{2} = V_{BE} + V_{E}$$

$$V_{2} = V_{BE} + I_{E}R_{E}$$

$$\begin{split} I_E &= \frac{V_2 - V_{BE}}{R_E} \\ I_C &= \frac{V_2 - V_{BE}}{R_R} \quad \because I_C \cong I_E \\ I_C &= \frac{V_{CC}}{R_1 + R_2} \cdot R_2 - V_{BE}}{R_E} \end{split}$$

It is apparent from above expression that the collector current is independent of ? thus the stability is excellent. In all practical cases the value of VBE is quite small in comparison to the V2, so it can be ignored in the above expression so the collector current is almost independent of the transistor parameters thus this arrangement provides excellent stability.

Again applying KVL in collector circuit, we have

$$\begin{split} & V_{CC} = I_C R_C + V_{CE} + I_E R_E \\ & \because I_C \cong I_E \\ & \land V_{CC} = I_C R_C + V_{CE} + I_C R_E \\ & V_{CE} = V_{CC} - I_C \left( R_C + R_E \right) \end{split}$$

The resistor RE provides stability to the circuit. If the current through the collector rises, the voltage across the resistor RE also rises. This will cause VCE to increase as the voltage V2 is independent of collector current. This decreases the base current, thus collector current increases to its former value.

Stability factor for such circuit arrangement is given by

$$S = \frac{(1+\beta)(R_{eq} + R_{E})}{R_{eq} + R_{E}(1+\beta)}$$

$$R_{eq} = R_{1}||R_{2}$$

$$S = \frac{(1+\beta)\left(1 + \frac{R_{eq}}{R_{E}}\right)}{\frac{R_{eq}}{R_{E}} + 1 + \beta}$$

If Req/RE is very small compared to 1, it can be ignored in the above expression thus we have  $S = \frac{1+\beta}{1+\beta} = 1$

Which is excellent since it is the smallest possible value for the stability. In actual practice the value of stability factor is around 8-10, since Req/RE cannot be ignored as compared to 1.

#### **Merits:**

Unlike above circuits, only one dc supply is necessary.

Operating point is almost independent of  $\beta$  variation.

Operating point stabilized against shift in temperature. Demerits:

In this circuit, to keep IC independent of  $\beta$  the following condition must be met:

which is approximately the case if where  $R1 \parallel R2$  denotes the equivalent resistance of R1 and R2 connected in parallel.

As  $\beta$ -value is fixed for a given transistor, this relation can be satisfied either by keeping RE fairly large, or making R1||R2 very low.

If RE is of large value, high VCC is necessary. This increases cost as well as precautions necessary while handling.

If  $R1 \parallel R2$  is low, either R1 is low, or R2 is low, or both are low. A low R1 raises VB closer to VC, reducing the available swing in collector voltage, and limiting how large RC can be made without driving the transistor out of active mode. A low R2 lowers Vbe, reducing the allowed collector current. Lowering both resistor values draws more current from the power supply and lowers the input resistance of the amplifier as seen from the base.

AC as well as DC feedback is caused by RE, which reduces the AC voltage gain of the amplifier. A method to avoid AC feedback while retaining DC feedback is discussed below.

Usage: The circuit's stability and merits as above make it widely used for linear circuits.

# 2.3 BIAS COMPENSATION USING DIODE AND TRANSISTOR

The various biasing circuits considered use some type of negative feedback to stabilize the operation point. Also, diodes, thermistors and sensistors can be used to compensate for **variations in current**.

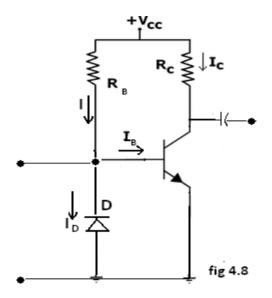

**2.3.1 DIODE COMPENSATION**: The following fig4.8 shows a transistor amplifier with a diode D connected across the baseemitter The following fig4.8 shows a transistor amplifier with a diode D connected across the base-emitter junction for compensation of change in collector saturation current ICO. The diode is of the same material as the transistor and it is reverse biased by e the emitter-base junction voltage VBE, allowing the diode reverse saturation current IO to flow through diode D. The base current IB=I-IO.

Fig 2.8 Diode Compensation circuit

As long as temperature is constant, diode D operates as a resistor. As the temperature increases, ICO of the transistor increases. Hence, to compensate for this, the base current IB should be decreased. The increase in temperature will also cause the leakage current IO through D to increase and thereby decrease the base current IB. This is the required action to keep Ic constant. This type of bias compensation does not need a change in IC to effect the change in IC, as both IO and ICO can track almost equally according to the change in temperature.

# 2.3.2 THERMISTOR COMPENSATION:

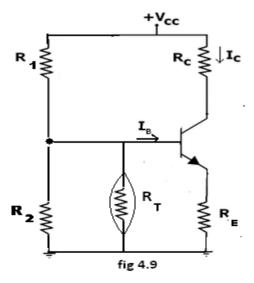

The following fig 2.9 a thermistor RT, having a negative temperature coefficient is connected in parallel with R2. The resistance of thermistor decreases exponentially with increase of temperature. An increase of temperature will decrease the base voltage VBE, reducing IB and IC. Fig

**Fig 2.9 Thermistor Compensation**

#### 2.3.3 SENSISTOR COMPENSATION:

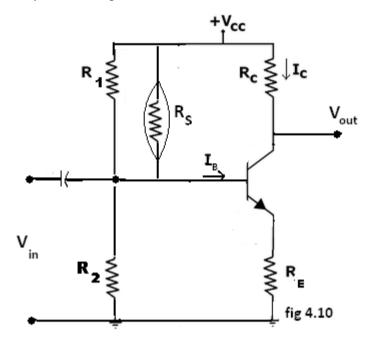

In the following fig4.10 shown a sensistor Rs having a positive temperature coefficient is connected across R<sub>1</sub> or R<sub>E</sub>. Rs increases with temperature. As the temperature increases, the equivalent resistance of the parallel combination of R1 and Rs also increases and hence V<sub>BE</sub> decreases, reducing I<sub>B</sub> and I<sub>c</sub>. This reduced I<sub>c</sub> compensates for increased I<sub>c</sub> caused by the increase in V<sub>BE</sub>, I<sub>c</sub> and  $\beta$  due to temperature.

Fig 2.10 Thermistor Compensation

# 2.4 THERMAL RUNAWAY AND THERMAL STABILITY

The collector current for the CE circuit is given by The three variables in the equation,  $\beta$ , , and increases with rise in temperature. In particular, the reverse saturation current or leakage current changes greatly with temperature. Specifically it doubles for every 10oC rise in temperature. The collector current causes the collector base junction temperature to rise which in turn, increase , as a result will increase still further, which will further rise the temperature at the collector base junction. This process will become cumulative leading at the collector base junction. This process will become cumulative leading to *"thermal runaway"*. Consequently, the ratings of the transistor are exceeded which may destroy the transistor itself.

The collector is made larger in size than the emitter in order to help the heat developed at the collector junction. However if the circuit is designed such that the base current is made to decrease automatically with rise in temperature, then the decrease in will compensate for increase in the

, keeping

almost constant.

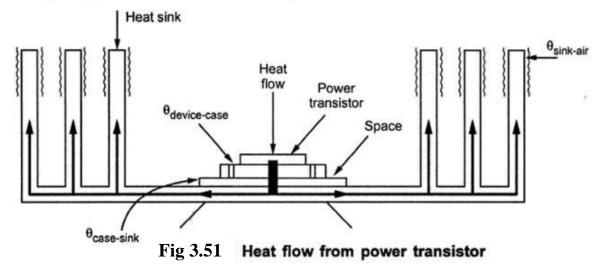

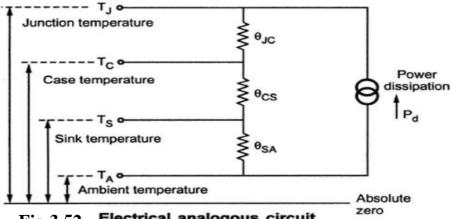

# 2.4.1 THERMAL RESISTANCE

Consider transistor used in a circuit where the ambient temperature of the air around the transistor is TAoC and the temperature of the collector-base junction of the transistor is TJoC. Due to heating within the transistor TJ is higher than TA. As the temperature difference TJ- TA is greater, the power dissipated in the transistor, PD will be greater, i.e, TJ- TA PD The equation can be written as TJ- TA PD. , where is the constant of proportionality and is called the Thermal resistance. Rearranging the above equation = TJ- TA /PD. Hence is measured in oC/W which may be as small as 0.2 oC/W for a high power transistor that has an efficient heat sink or up to 1000oC/W for small signal, low power transistor junction to the ambient temperature, it is referred to as  $\Theta$ J-A. However, for power transistors, thermal resistance is given form junction to case,  $\Theta$ J-C.

The amount resistance from junction to ambience is considered to consist of 2 parts.  $\Theta J-A = \Theta J-C - \Theta C-A$ .

Which indicates the heat dissipated in the junction must make its way to the surrounding air through two series paths from junction to case and from case to air. Hence the power dissipated.

If the effective surface area of the transistor case could be increased, the resistance to heat flows, or could be increased  $\Theta$ C-A, could be decreased. This can be achieved by the use of a heat sink.

The heat sink is a relatively large, finned, usually black metallic heat conducting device in close contact with transistor case or flange. Many versions of heat sink exist depending upon the shape and size of the transistor. Larger the heat sink smaller is the thermal resistance  $\Theta$ HS-A.

This thermal resistance is not added to  $\Theta$ C-A in series, but is instead in parallel with it and if  $\Theta$ HS-A is much less than  $\Theta$ C-A, then  $\Theta$ C-A will be reduced significantly, thereby improving the dissipation capability of the transistor. Thus

ΘJ-A

$=\Theta$  J-C +  $\Theta$  C-A $\parallel$   $\Theta$ HS-A.

# 2.4.2 CONDITION FOR THERMAL STABILITY

For preventing thermal runaway, the required condition I the rate at which the heat is released at the collector junction should not exceed the rate at which the heat can be dissipated under steady state condition. Hence the condition to be satisfied to avoid thermal runaway is given

If the circuit is properly designed, then the transistor cannot runaway below a specified ambient temperature or even under any conditions.

In the self biased circuit the transistor is biased in the active region. The power generated at the junction without any signal is

$$P_C = I_C V_{CB} \approx I_C V_{CE}$$

Let us assume that the quiescent collector and the emitter currents are equal. Then

$$P_{C} = I_{C}V_{CC} - I_{C}^{2}(R_{E} + R_{C})....$$

The condition to prevent thermal runaway can be written as

As  $\Theta$  and  $\frac{\partial I_C}{\partial \tau_i}$  are positive,  $\frac{\partial P_C}{\partial I_C}$  should be negative in order to satisfy the above condition.

Differentiating equation (1) w.r.t I<sub>c</sub> we get

Hence to avoid thermal runaway it is necessary that

SinceVCE=VCC-IC(RE+RC) then eq(4) implies that VCE<VCC/2. IF the inequality of eq(4) is not satisfied and VCE<VCC/2, then from eq(3),  $\frac{\partial P_C}{\partial I_C}$  is positive., and the corresponding eq(2) should be satisfied. Otherwise thermal runaway will occur.

## 2.5 BJT HYBRID MODEL

# Small signal low frequency transistor Models:

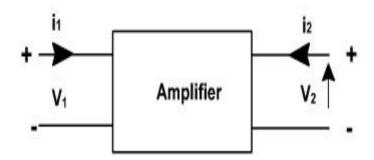

All the transistor amplifiers are two port networks having two voltages and two currents. The positive directions of voltages and currents are shown in

Fig 2.11 Two port network

A two - port network is represented by four external variables: voltage V1 and current I1 at the input port, and voltage V2 and current I2 at the output port, so that the two -port network can be treated as a black box modeled by the relationships between the four variables,V1,V2, I1,I2 . Out of four variables two can be selected as are independent variables and two are dependent variables. The dependent variables can be expressed interns of independent variables. This leads to various two port parameters out of which the following three are important:

- 1. Impedance parameters (z parameters)

- 2. Admittance parameters (y parameters)

- 3. Hybrid parameters (h parameters)

## z-parameters

A two -port network can be described by z-parameters as

$$V_1 = Z_{11}l_1 + Z_{12}l_2$$

$$V_2 = Z_{21}l_1 + Z_{22}l_2$$

In matrix form, the above equation can be rewritten as

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} z_{11} & z_{12} \\ z_{21} & z_{22} \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}$$

Where

$$z_{11} = \left. \frac{V_1}{I_1} \right|_{I_2 = 0}$$

Input impedance with output port open circuited

$$z_{12} = \left. \frac{V_1}{I_2} \right|_{I_1=0}$$

Reverse transfer impedance with input port open circuited

$$z_{21} = \left. \frac{V_2}{I_1} \right|_{I_2=0}$$

Forward transfer impedance with output port open circuited

$$z_{22} = \left. \frac{V_2}{I_2} \right|_{I_1=0}$$

Output impedance with input port open circuited

# **Y** -parameters

A two -port network can be described by Y-parameters as

$$I_1 = Y_{11}V_1 + Y_{12}V_2$$

$$I_2 = Y_{21}V_1 + Y_{22}V_2$$

$$\begin{bmatrix} I_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} y_{11} & y_{12} \\ y_{21} & y_{22} \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}$$

$$y_{11} = \left. \frac{I_1}{V_1} \right|_{V_2 = 0}$$

Input admittance with output port short circuited

$$y_{12} = \left. \frac{I_1}{V_2} \right|_{V_1 = 0}$$

Reverse transfer admittance with input port short circuited

$$y_{21} = \left. \frac{I_2}{V_1} \right|_{V_2 = 0}$$

Forward transfer admittance with output port short circuited

$$y_{22} = \left. \frac{I_2}{V_2} \right|_{V_1=0}$$

Output admittance with input port short circuited

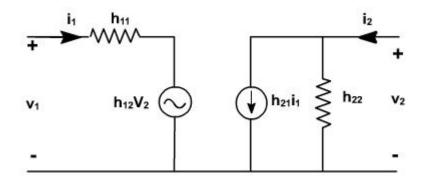

#### Hybrid parameters (h-parameters)

If the input current I1 and output voltage V2 are taken as independent variables, the dependent variables V1 and I2 can be written as

$$\begin{bmatrix} V_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} h_{11} & h_{12} \\ h_{21} & h_{22} \end{bmatrix} \begin{bmatrix} I_1 \\ V_2 \end{bmatrix}$$

Where h11, h12, h21, h22 are called as hybrid parameters.

$$h_{11} = \left. \frac{V_1}{I_1} \right|_{V_2 = 0}$$

Input impedence with o/p port short circuited

$$h_{12} = \left. \frac{V_1}{V_2} \right|_{I_1=0}$$

Reverse voltage transfer ratio with i/p port open circuited

$$h_{21} = \left. \frac{I_2}{I_1} \right|_{V_2=0}$$

Forward voltage transfer ratio with o/p port short circuited

$$h_{22} = \left. \frac{I_2}{V_2} \right|_{I_1=0}$$

output impedence with i/p port open circuited

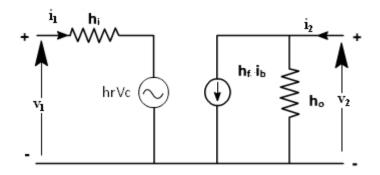

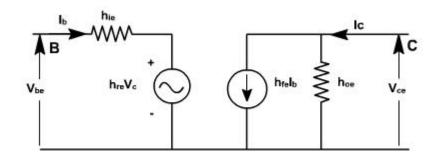

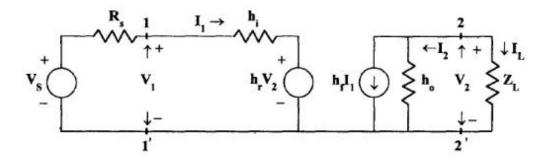

THE HYBRID MODEL FOR TWO PORT NETWORK:

Based on the definition of hybrid parameters the mathematical model for two pert networks known as h-parameter model can be developed. The hybrid equations can be written as:  $V_1 = h_i I_1 + h_r V_2$

$I_2 = h_f I_1 + h_o V_2$

# f =21 = forward transfer r = 12 = reverse transfer)

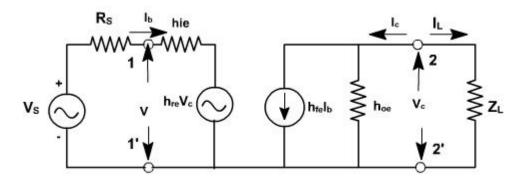

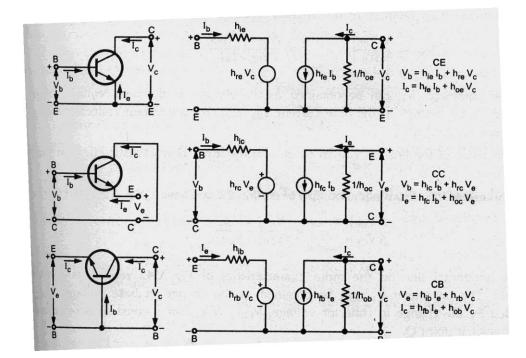

We may now use the four h parameters to construct a mathematical model of the device of Fig.(1). The hybrid circuit for any device indicated in Fig.(2). We can verify that the model of Fig.(2) satisfies above equations by writing Kirchhoff'svoltage and current laws for input and output ports.

If these parameters are specified for a particular configuration, then suffixes e,b or c are also included, e.g.  $h_{fe}$ ,  $h_{ib}$  are h parameters of common emitter and common collector amplifiers

Using two equations the generalized model of the amplifier can be drawn as shown in fig. 2.

Fig. 2

# TRANSISTOR HYBRID MODEL:

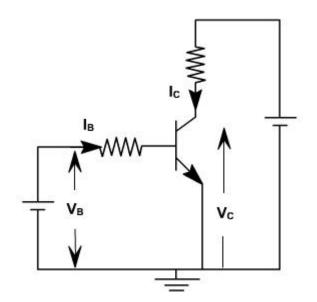

The hybrid model for a transistor amplifier can be derived as follow:

Let us consider CE configuration as show in <u>fig. 3</u>. The variables,  $i_B$ ,  $i_C$ ,  $v_C$ , and  $v_B$  represent total instantaneous currents and voltages  $i_B$  and  $v_C$  can be taken as independent variables and  $v_B$ ,  $I_C$  as dependent variables.

$$V_{B} = f1 (i_{B}, v_{C})$$

$$I_{c} = f2 (i_{B}, v_{c}).$$

Using Taylor 's series expression, and neglecting higher order terms we obtain.

$$\Delta v_{B} = \frac{\partial f_{1}}{\partial i_{B}} \bigg|_{V_{C}} \Delta i_{B} + \frac{\partial f_{1}}{\partial v_{C}} \bigg|_{i_{B}} \Delta v_{C}$$

$$\Delta i_{C} = \frac{\partial f_{2}}{\partial i_{B}} \bigg|_{V_{C}} \Delta i_{B} + \frac{\partial f_{2}}{\partial v_{C}} \bigg|_{i_{B}} \Delta v_{C}$$

The partial derivatives are taken keeping the collector voltage or base current constant. The  $\Delta v_B$ ,  $\Delta v_C$ ,  $\Delta i_B$ ,  $\Delta i_C$  represent the small signal (incremental) base and collector current and voltage and can be represented as  $v_B$ ,  $i_C$ ,  $i_B$ ,  $v_C$

where

$$\begin{aligned} h_{ie} &= \frac{\partial f_1}{\partial i_B} \Big|_{v_c} &= \left. \frac{\partial v_B}{\partial i_B} \right|_{v_c}; \qquad h_{re} &= \left. \frac{\partial f_1}{\partial v_C} \right|_{i_B} &= \left. \frac{\partial v_B}{\partial v_C} \right|_{i_B} \\ h_{fe} &= \left. \frac{\partial f_2}{\partial i_B} \right|_{v_c} &= \left. \frac{\partial i_C}{\partial i_B} \right|_{v_c}; \qquad h_{oe} &= \left. \frac{\partial f_2}{\partial v_C} \right|_{i_B} &= \left. \frac{\partial v_B}{\partial v_C} \right|_{i_B} \end{aligned}$$

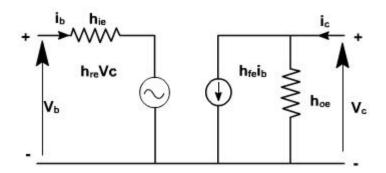

The model for CE configuration is shown in fig. 4.

Fig. 4

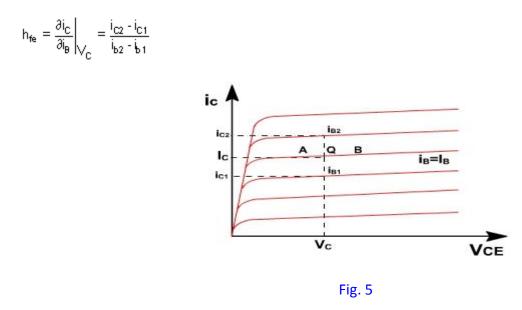

To determine the four h-parameters of transistor amplifier, input and output characteristic are used. Input characteristic depicts the relationship between input voltage and input current with output voltage as parameter. The output characteristic depicts the relationship between output voltage and output current with input current as parameter. <u>Fig. 5</u>, shows the output characteristics of CE amplifier.

The current increments are taken around the quiescent point Q which corresponds to  $i_B = I_B$  and to the collector voltage  $V_{CE} = V_C$

$$h_{oe} = \frac{\partial i_C}{\partial V_C} \Big|_{i_B}$$

The value of  $h_{oe}$  at the quiescent operating point is given by the slope of the output characteristic at the operating point (i.e. slope of tangent AB).

$$h_{ie} = \frac{\partial V_B}{\partial i_B} \approx \frac{\Delta V_B}{\Delta i_B} \Big|_{V_C}$$

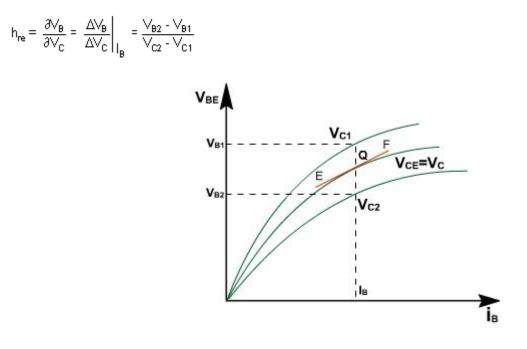

$h_{ie}$  is the slope of the appropriate input on <u>fig. 6</u>, at the operating point (slope of tangent EF at Q).

Fig. 6

A vertical line on the input characteristic represents constant base current. The parameter hre can be obtained from the ratio ( $V_{B2}$ -  $V_{B1}$ ) and ( $V_{C2}$ -  $V_{C1}$ ) for at Q.

Typical CE h-parametersof transistor 2N1573 are given below:

$h_{ie} = 1000 \text{ ohm.}$   $h_{re} = 2.5 * 10 - 4$   $h_{fe} = 50$  $h_{oe} = 25 @A / V$

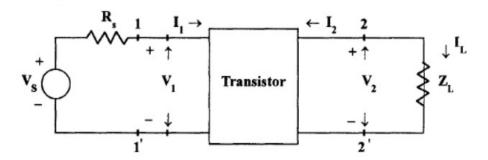

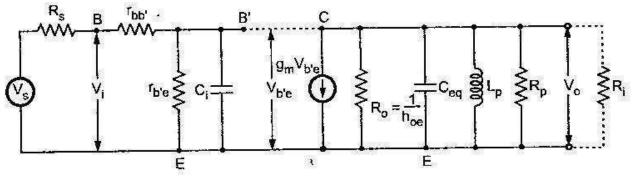

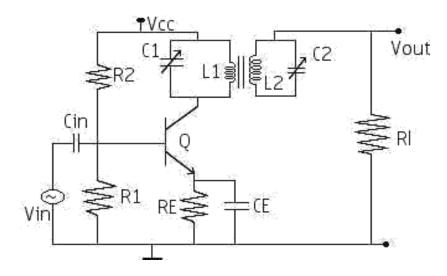

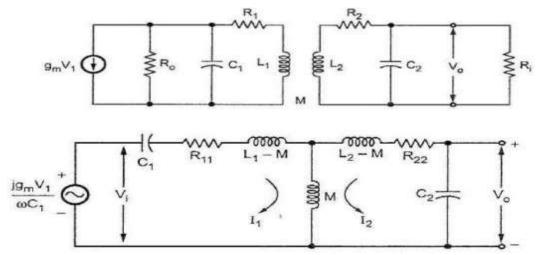

## ANALYSIS OF A TRANSISTOR AMPLIFIER USING H-PARAMETERS:

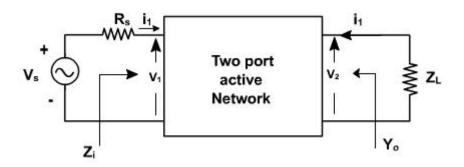

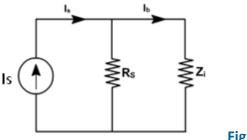

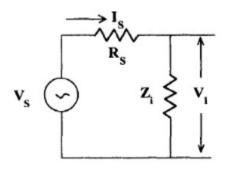

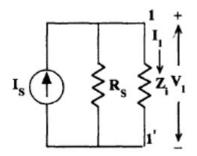

To form a transistor amplifier it is only necessary to connect an external load and signal source as indicated in <u>fig. 1</u> and to bias the transistor properly.

Fig. 1

Consider the two-port network of CE amplifier.  $R_s$  is the source resistance and  $Z_L$  is the load impedence h-parameters are assumed to be constant over the operating range. The ac equivalent circuit is shown in <u>fig. 2</u>. (Phasor notations are used assuming sinusoidal voltage input). The quantities of interest are the current gain, input impedence, voltage gain, and output impedence.

## Current gain:

For the transistor amplifier stage, A<sub>i</sub> is defined as the ratio of output to input currents.

$$A_I = \frac{I_L}{I_1} = \frac{-I_2}{I_1}$$

# Input impedence:

The impedence looking into the amplifier input terminals (1,1') is the input impedance  $Z_i$

$$Z_{i} = \frac{V_{b}}{I_{b}}$$

$$V_{b} = h_{ie} I_{b} + h_{re} V_{c}$$

$$\frac{V_{b}}{I_{b}} = h_{ie} + h_{re} \frac{V_{c}}{I_{b}}$$

$$= h_{ie} - \frac{h_{re} I_{c} Z_{L}}{I_{b}}$$

$$\therefore Z_{i} = h_{ie} + h_{re} A_{I} Z_{L}$$

$$= h_{ie} - \frac{h_{re} h_{fe} Z_{L}}{1 + h_{oe} Z_{L}}$$

$$\therefore Z_{i} = h_{ie} - \frac{h_{re} h_{fe}}{Y_{L} + h_{oe}} \qquad (\text{since } Y_{L} = \frac{1}{Z_{L}})$$

# Voltage gain:

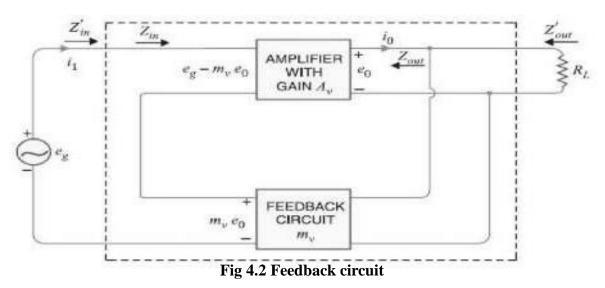

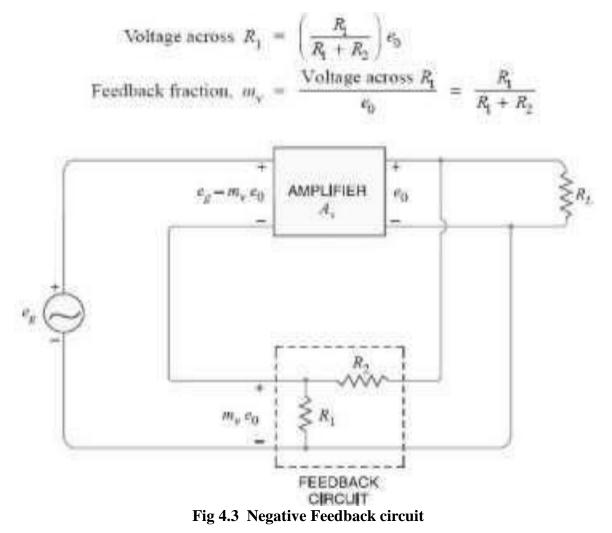

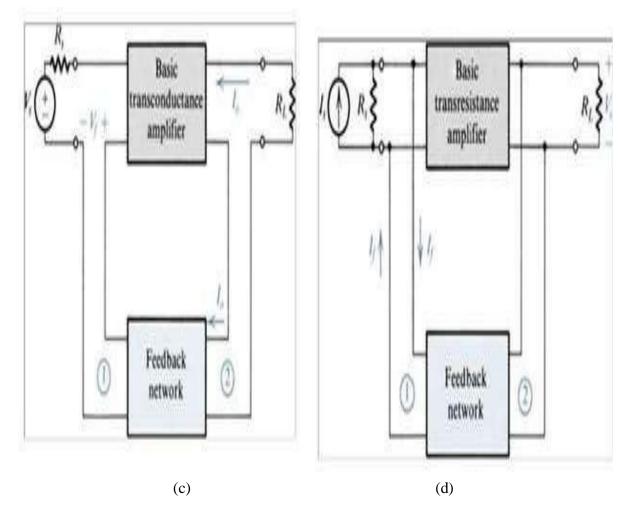

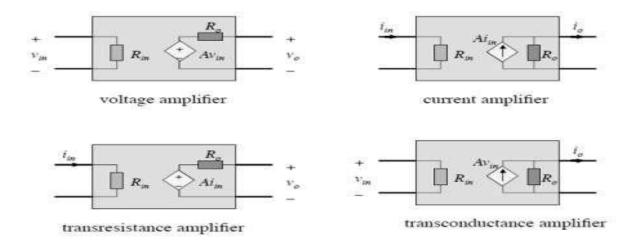

The ratio of output voltage to input voltage gives the gain of the transistors.