(DEEMED TO BE UNIVERSITY)

Accredited "A" Grade by NAAC | 12B Status by UGC | Approved by AICTE

www.sathyabama.ac.in

# SCHOOL OF ELECTRICAL AND ELECTRONICS

# DEPARTMENT OF ELECTRONICS AND COMMMUNICATION ENGINEERING

# UNIT - I PROGRAMMING IN HDL – SEC1406

#### I. CONCEPTS IN VHDL

#### INTRODUCTION TO VHDL

VHDL is an acronym for VHSIC Hardware Description Language (VHSIC is an acronym for Very High Speed Integrated Circuits). It is a hardware description language that can be used to model a digital system at many levels of abstraction ranging from the algorithmic level to the gate level. The complexity of the digital system being modeled could vary from that of a simple gate to a complete digital electronic system, or anything in between. The digital system can also be described hierarchically. Timing can also be explicitly modeled in the same description.

The VHDL language can be regarded as an integrated amalgamation of the following languages:

- sequential language

- Concurrent language

- net-list language

- timing specifications

- Waveform generation language.

Therefore, the language has constructs that enable you to express the concurrent or sequential behavior of a digital system with or without timing. It also allows you to model the system as an interconnection of components. Test waveforms can also be generated using the same constructs. All the above constructs may be combined to provide a comprehensive description of the system in a single model.

The language not only defines the syntax but also defines very clear simulation semantics for each language construct. Therefore, models written in this language can be verified using a VHDL simulator. It is a strongly typed language and is often verbose to write. It inherits many of its features, especially the sequential language part, from the Ada programming language. Because VHDL provides an extensive range of modeling capabilities, it is often difficult to understand. Fortunately, it is possible to quickly assimilate a core subset of the language that is both easy and simple to understand without learning the more complex features. This subset is usually sufficient to model most applications. The complete language, however, has sufficient power to capture the descriptions of the most complex chips to a complete electronic system.

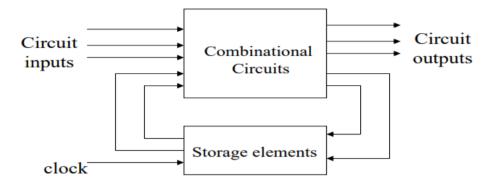

#### Digital system design process:-

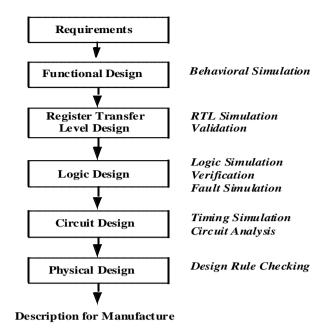

Figure 1.1 : Digital system design process

Digital Systems have conquered the whole world. Every appliances or equipment's we see today are digital. This is because of the very small element called Transistor invented by John Bardeen, Walter Brattain & William Shockley in 1947 at Bell Labs. This tiny and Powerful transistor changed the future of Electronics. Therefore it is our responsibility to study the analysis and design of this digital system as an electronic student. In this chapter we will study the Basic Digital IC Design Flow and then we will study what are the tools available for digital design and synthesis. Later we are going to study a special hardware description language (VHDL) which is used to describe the digital systems.

#### **Digital Design Flow Process:-**

Based on the specification given, the design team forms a general idea about the solution to the problem. System level decisions are made regarding the design and a general consensus is reached regarding the major functional blocks that go into the making of the chip. At the end of this stage, a general block diagram solution of the design is agreed upon. CAD tools are generally not needed at this stage.

#### **Behavioral Design:**

Hardware Description Languages (HDLs) are used to model the design idea (block diagram). Circuit details and electrical components are not specified. Instead, the behavior of each block at the highest level of abstraction is modeled. Simulations are then run to see if the blocks do indeed function as expected and the whole system performs as a whole. Behavioral descriptions are important as they corroborate the integrity of the design idea. Here we don't have any architectural or hardware details.

#### **Data Path Design:**

The next Phase in the design process is the design of the system data path. In this phase, the designer specifies the registers and logic units necessary for implementation of the system. These components may be interconnected using either bidirectional or unidirectional buses. Based on the intended behavior of the system, the procedure of controlling the movement of data between registers and logic units through buses are developed. Data components in the data part of circuit communicate via system busses and the control procedure controls flow of data between these components. This phase results in architectural design of the system with specification of control flow.

# **Logic Design:**

Logic Design is the next phase in the design process and involves the use of primitive gates and flip-flops for the implementation of data registers, busses, logic units, and their controlling hardware. The result of this design stage is a net list of gates and flip-flops. Components used and their interconnections are specified in this net list.

#### **Physical Design:**

This stage transforms the net list into transistor list or layout. This involves the replacement of gates and flip-flops with their transistor equivalents or library cells.

#### **Manufacturing:**

The final step is manufacturing, which uses the transistor list or layout specification to burn fuses of FPGA or to generate masks for Integrated circuit (IC).

#### **Basic Terminology**

VHDL is a hardware description language that can be used to model a digital system. The digital system can be as simple as a logic gate or as complex as a complete electronic system. A

hardware abstraction of this digital system is called an entity in this text. An entity X, when used in another entity Y, becomes a component for the entity Y. Therefore, a component is also an entity, depending on the level at which you are trying to model.

To describe an entity, VHDL provides five different types of primary constructs, called design units. They are

- 1. Entity declaration

- 2. Architecture body

- 3. Configuration declaration

- 4. Package declaration

- 5. Package body

#### **Entity Declaration**

The entity' declaration specifies the name of the entity being modeled and lists the set of interface ports. Ports are signals through which the entity communicates with the other models in its external environment.

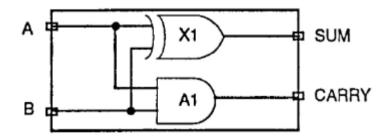

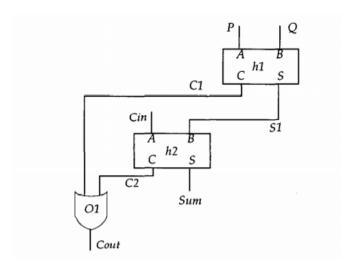

Figure 1.2: Half adder

Here is an example of an entity declaration for the half-adder circuit

entity HALF\_ADDER is

port (A, B: in BIT; SUM, CARRY: out BIT);

end HALF\_ADDER;

The entity, called HALF\_ADDER, has two input ports, A and B (the mode in specifies input port), and two output ports, SUM and CARRY (the mode out specifies output port). BIT is a predefined type of the language; it is an enumeration type containing the character literals '0' and '1'. The port types for this entity have been specified to be of type BIT, which means that the ports can take the values, '0' or '1'.

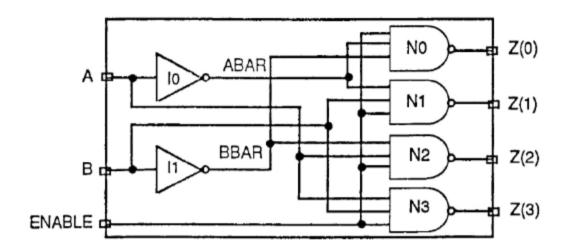

The following is another example of an entity declaration for a 2-to-4 decoder circuit entity DECODER2x4 is

port(A, B, ENABLE: in SIT: Z: out BIT\_VECTOR(0 to 3)); end DECODER2x4;

Figure 1.3: 2\*4 decoder

This entity, called DECODER2x4, has three input ports and four output ports. BIT\_VECTOR is a predefined unconstrained array type of BIT. An unconstrained array type is a type in which the size of the array is not specified. The range "0 to 3" for port Z specifies the array size.

From the last two examples of entity declarations, we see that the entity declaration does not specify anything about the internals of the entity. It only specifies the name of the entity and the interface ports.

#### **Architecture Body**

The internal details of an entity are specified by an architecture body using any of the following modeling styles:

- 1. As a set of interconnected components (structural modeling)

- 2. As a set of concurrent assignment statements (dataflow modeling)

- 3. As a set of sequential assignment statements (behavioral modeling)

- 4. Any combination of the above three (Mixed modeling)

#### **Configuration Declaration**

A configuration declaration is used to select one of the possibly many architecture bodies that an entity may have, and to bind components, used to represent structure in that architecture body, to entities represented by an entity-architecture pair or by a configuration, that reside in a design library. Consider the following configuration declaration for the HALF\_ADDER entity.

```

library CMOS_LIB, MY_LIB;

configuration HA_BINDING of HALF_ADDER is for HA-STRUCTURE

for X1:XOR2

use entity CMOS_LIB.XOR_GATE(DATAFLOW);

end for;

```

for A1:AND2

use configuration MY\_LIB.AND\_CONFIG;

end for;

end for; end HA\_BINDING;

# **Package Declaration**

A package declaration is used to store a set of common declarations like components, types, procedures, and functions. These declarations can then be imported into other design units using a context clause. Here is an example of a package declaration.

```

package EXAMPLE_PACK is

```

```

type\ SUMMER\ is\ (MAY, JUN, JUL, AUG, SEP);\ component\ D\_FLIP\_FLOP

```

port (D, CK: in BIT; Q, QBAR: out BIT); end component;

constant PIN2PIN\_DELAY: TIME := 125 ns; function INT2BIT\_VEC (INT\_VALUE: INTEGER)

return BIT\_VECTOR;

end EXAMPLE\_PACK;

# **Package Body**

A package body is primarily used to store the definitions of functions and procedures that were declared in the corresponding package declaration, and also the complete constant declarations for any deferred constants that appear in the package declaration. Therefore, a package body is always associated with a package declaration; furthermore, a package

declaration can have at most one package body associated with it. Contrast this with an architecture body and an entity declaration where multiple architecture bodies may be associated with a single entity declaration. A package body may contain other declarations as well.

Here is the package body for the package EXAMPLE\_PACK declared in the previous section.

package body EXAMPLE\_PACK is

function INT2BIT\_VEC (INT\_VALUE: INTEGER) return

BIT\_VECTOR is

begin

end INT2BIT\_VEC;

end EXAMPLE PACK;

# Language elements of VHDL

**Basic Language Elements of VHDL are**

- Identifiers

- Comments

- Data Objects

- Data Types

- Operators

#### **Identifiers**

- Identifiers are used to name items in a VHDL model.

Basic identifier: composed of a sequence of one or more characters, A basic identifier may contain only capital 'A' - 'Z', 'a' - 'z', '0' - '9', underscore character '\_'

- first character must be a letter, last character must NOT be an underscore

- Two underscores cannot occur concurrently

- case insensitive: COUNT, count, Count, counT are all the same

- Keywords can not be used as basic identifiers

Extended identifier: sequence of characters written between two backslashes

Any printable characters can be used including %, \$, \*, etc.

- lower case and upper case are distinct

- examples: /2FOR\$/ , /countNow!/ , /&#\$(@#&!!!/

#### **Comments**

- Its non executable or readable parameter for understanding purpose.

- The comments to be proceeded by two consecutive hyphens(--)

```

Example

```

```

entity half_adder is

port (a, b: in std_logic; sum, carry: out std_logic);

end half adder; -- end of entity with entity name

architecture HA-DF of half_adder is

begin

sum <= a xor b; -- a xor with b, result assigned to sum

carry <= a and b; -- a and with b, result assigned to carry

end HA DF;

-- end of architecture with architecture name

Data Objects

- hold a value of a specified type

constant: holds a single value of a specified type and cannot be changed throughout the

simulation

constant declaration:

constant RESULT: BIT:=1;

constant FALL TIME: TIME:=10ns

variable: holds a single value of a specified type but can be changed throughout the

simulation

variable ABAR:BIT;

variable STATUS:BIT_VECTOR(3 downto 0);

```

signal: holds a list of values including current value and a list of possible future values typically used to model wires and flip-flops signal DATA BUS:BIT VECTOR(0 to 31)

file: same as with any computer file, contains data

**Data Types**

- Is a name which is associated with a set of values and a set of operations.

**Major Data Types:**

**Scalar Type**

**Composite Type**

**Access Type**

File Type

There can also be user-defined types and subtypes A *subtype* is a type with a (possibly) added constraint

syntax: subtype subtype\_name is base\_type range range\_constraint;

example: subtype DIGITS is integer range 0 to 9;

**Scalar types**

Enumeration – defines a type that has a set of user-defined values

type std logic is ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H','-');

'u' unspecified, 'x' unknown, '0' strong zero, '1' strong one

'z' high impedance, 'w' weak unknown, 'l' weak zero, 'h' weak one, '-' don't care

Integer – values fall within the specified integer range

type REG SIZE is range 0 to 31

subtype WORD is REG SIZE range 0 to 15

Floating Point -real decimal types

Physical – represent measurement of some physical quantity like time, voltage, or current

# **Composite Types** - a collection of values Array Types - collection of values all belonging to a single type BIT\_VECTOR and STRING are pre-defined one-dimensional array types type DATA\_BYTE is array (0 to 7) of BIT; type MEMORY is array (0 to 127) of DATA\_BYTE; Record Types – collection of values that may belong to different types type MODULE is record **SUM:** BIT\_VECTOR(0 to 7); **COUT: BIT;** end record; **Access Type** Values belonging to an access type are pointers to a allocated object of some other type. **Example:** type PTR is access MODULE; File Type Objects of file type represent files in the host environment. Syntax: type file\_type\_name is file of type\_name; **Data Operators** VHDL will support different types of operations. The following are the types of operators available in VHDL 1. Assignment operator 2. Logical Operator 3. Relational Operator

4. Shift operator

- 5. Arithmetic operator

- **5.1 Addition Operator**

- **5.2 Multiplication Operator**

- **5.3** Miscellaneous operator

#### **Assignment Operator**

This operator is used to assign values to signals, variables, and constants. They are

- 1. <= Used to assign a value to signal

- 2. := Used to assign a variable, constant or generic, used for also establishing initial values.

- 3. => Used to assign values to individual vector or with others.

# **Logical Operators**

Used to perform to logical operations. The data must be of type Bit, Std\_logic or std\_ulogic. The logical operators are:

- **1. NOT**

- **2. AND**

- 3. OR

- 4. NAND

- 5. NOR, XOR & XNOR

### **Relational Operators**

Used for making comparisons. The data can be of any types listed above. The relational (Comparison) operators listed below:

- 1. = Equal to

- 2. /= not equal to

- 3. < Greater than

- 4. > Lesser than

- 5. <= Greater than

- 6. >= Lesser than

# **Shift Operators**

Used for shifting data.

1. Sll: Shift left logic

2. Sla: shift left arithmetic

3. Srl: Shift right logic

4. Sra: Shift right arithmetic

5. Rol:Rotateleft

6. Ror: Rotate right

Arithmetic Operators Used to perform arithmetic operations. The data can be of integer, signed, Unsigned or a real.

The different types of arithmetic operations are:

Addition operator (+)

**Subtract Operator (-)**

**Multiplication operator** (\*)

**Division Operator** (/)

Modulus (MOD)

Remainder (REM)

Miscellaneous Operator Uses as special cases in VHDL

- 1. Absolute (ABS)

- 2. Exponentiation (\*\*)

# **Concurrent and Sequential assignments**

- 1. As a set of concurrent assignment statements (to represent dataflow),

- 2. As a set of sequential assignment statements (to represent be-hav.ior),

**Dataflow Style of Modeling(Concurrent assignment)**

In this modeling style, the flow of data through the entity is expressed primarily using concurrent signal assignment statements. The structure of the entity is not explicitly specified

in this modeling style, but it can be implicitly deduced. Consider the following alternate architecture body for the HALF..ADDER entity that uses this style.

architecture HA CONCURRENT of HALF ADDER is

begin

$sum \le A xor B$ ;

carry <= A and B;

end HALF ADDER;

The dataflow model for the HALF\_ADDER is described using two concurrent signal assignment statements (sequential signal assignment statements are described in the next section). In a signal assignment statement, the symbol <= implies an assignment of a value to a signal. The value of the expression on the right-hand-side of the statement is computed and is assigned to the signal on the left-hand-side, called the *target signal*. A concurrent signal assignment statement is executed only when any signal used in the expression on the right-hand-side has an event on it, that is, the value for the signal changes.

Delay information is included in the signal assignment statements using after clauses. If either signal A or B, which are input port signals of HALF\_ADDER entity, has an event, say at time T, the right-hand-side expressions of both signal assignment statements are evaluated. Signal SUM is scheduled to get the new value after 8 ns while signal CARRY is scheduled to get the new value after 4 ns. When simulation time advances to (T+4) ns, CARRY will get its new value and when simulation time advances to (T+8) ns, SUM will get its new value. Thus, both signal assignment statements execute concurrently.

Concurrent signal assignment statements are concurrent statements, and therefore, the ordering of these statements in an architecture body is not important. Note again that this architecture body, with name HA\_CONCURRENT, is also associated with the same HALF\_ADDER entity declaration.

Here is a dataflow model for the DECODER2x4 entity.

architscturedec dataflow of DECODER2x4

is signal ABAR, BBAR: BIT;

begin

Z(3) <=not (A and B and ENABLE); -- Statement 1

Z(0) <=not (ABAR and BBAR and ENABLE); --- Statement 2

BBAR <= not B; -- Statement 3

Z(2) <= not (A and BBAR and ENABLE); -- Statement 4

ABAR <= not A; -- Statement 5

Z(1) <= not (ABAR and B and ENABLE); -- Statement 6 end DEC\_DATAFLOW;

The architecture body consists of one signal declaration and six concurrent signal assignment statements. The signal declaration declares signals ABAR and BBAR to be used locally within the architecture body. In each of the signal assignment statements, no after clause was used to specify delay. In all such cases, a default delay of 0ns is assumed. This delay of 0ns is also known as delta delay, and it represents an infinitesimally small delay. This small delay corresponds to a zero delay with respect to simulation time and does not correspond to any real simulation time.

To understand the behavior of this architecture body, consider an event happening on one of the input signals, say input port B at time T. This would cause the concurrent signal assignment statements 1,3, and 6, to be triggered. Their right -hand-side expressions would be evaluated and the corresponding values would be scheduled to be assigned to the target signals at time (T+A). When simulation time advances to (T+A), new values to signals Z(3), BBAR, and Z(1), are assigned. Since the value of BBAR changes, this will in turn trigger signal assignment statements, 2 and 4. Eventually, at time (T+2A), signals Z(0) and Z(2) will be assigned their new values. The semantics of this concurrent behavior indicate that the simulation, as defined by the language, is event-triggered and that simulation time advances to the next time unit when an event is scheduled to occur. Simulation time could also advance a multiple of delta time units. For example, events may have been scheduled to occur at times 1,3,4,4+A,5,6,6+A,6+2A,6+3A,10,10+A,15,15+A time units.

The after clause may be used to generate a clock signal as shown in the following concurrent signal assignment statement

CLK <= not CLK after 10 ns;

Behavioral Style of modeling (Sequential assignment)

In contrast to the styles of modeling described earlier, the behavioral style of modeling specifies the behavior of an entity as a set of statements that are executed sequentially in the specified order. This set of sequential statements, that are specified inside a process statement, do not explicitly specify the structure of the entity but merely specifies its functionality. A process statement is a concurrent statement that can appear within an architecture body. For example, consider the following behavioral model for the DECODER2x4 entity.

architecture DEC\_SEQUENTIAL of DECODER2x4 is

begin

process (A,B)

```

variable ABAR,BBAR : std_logic;

begin

ABAR := not A;

BBAR := not B;

Z(0) <= (ABAR and BBAR);

Z(1) <= (ABAR and B);

Z(2) <= (A and BBAR);

Z(3) <= (A and B):

end process;</pre>

```

#### **Structural Model**

An entity is modeled as a set of components connected by signals, that is, as a net-list. The behavior of the entity is not explicitly apparent from its model. The component instantiation statement is the primary mechanism used for describing such a model of an entity. COMPONENT & PORT MAP statements are used to implement structural modeling. The component instantiation statements are concurrent statements, and their order of appearance in the architecture body is therefore not important. A component can be instantiated any number of times. Each instantiation must have a unique component label.

#### **Component Declaration**

A component in a structural description must first be declared using a component declaration. A component declaration declares the name and the interface of a component (similar to the entity). The interface specifies the mode and the type of ports.

The syntax of a simple form of component declaration is:

```

COMPONENT Component-Name [IS]

PORT(List-of-Interface-Ports);

END COMPONENT [Component-Name];

```

The component-name may or may not refer to the name of an entity already existing in a library. If it does not, it must be explicitly bound to an entity. The binding information can be specified using a configuration. The List-of-Interface-Ports specifies the name, mode, and type for each port of the component in a manner similar to that specified in an entity declaration. The names of the ports may also be different from the names of the ports in the entity to which it may be bound (different port names can be mapped in a configuration)

#### **Component Instantiation**

A component instantiation statement defines a association of formal and actual parameters. It associates the signals in the entity with the ports of that component.

A format of a component instantiation statement:

Component-Label: Component-Name PORT MAP (association-list);

The Component-Label can be any legal identifier and can be considered as the name of the instance. The Component-Name must be the name of a component declared earlier using a component declaration. The association-list, associates signals in the entity, called actuals, with the ports of a component, called formals.

There are two ways to perform the association of formals with actuals:

- 1. Positional association

- 2. Named association

In positional association, each actual in the component instantiation is mapped by position with each port in the component declaration. That is, the first port in the component declaration corresponds to the first actual in the component instantiation, the second with the second, and so on.

```

COMPONENT dff

PORT (d, clk: IN bit; q, qb: OUT bit);

END COMPONENT;

dl: dff PORT HAP (data, ck, sl, s2);

```

If a port in a component instantiation is not connected to any signal, the keyword OPEN can be used to signify that the port is not connected.

For example

```

d1: dff PORT MAP (data, ck, s1, open);

```

In named association, an association-list is of the form:

```

formal1 => actual1, formal2=> actual2, ... formaln=> actualn

```

For example

```

d1: dff PORT MAP (d => data, clk => ck, q => s1, qb => s2);

```

In named association, the ordering of the associations is not important since the mapping between the actual and formal is explicitly specified.

#### **Dataflow Model**

The Data-Flow modeling is a collections of concurrent statements. All the statements must be write only in the architecture body. There is no meaning to the order of the statements.

```

There are 3 Data-Flow statement:

- Concurrent Signal Assignment

- Conditional Signal Assignment

- Selected Signal Assignment

Concurrent Signal Assignment

The syntax is:

target-signal _1<= expression_1;</pre>

target-signal 2<= expression 2;

-Example:

entity decoder is

port (a, b : in std_logic;

d: out std_logic_vector(0 to 3));

end decoder;

architecture DEC_DF of decoder is

signal s1,s2: std_logic;

begin

s1 \le not a;

s2 \le not b;

d(0) \le s1 \text{ and } s2;

d(1) \le s1 and b;

d(2) \le a \text{ and } s2;

d(3) \le a and b;

```

## **Conditional Signal Assignment Statement**

end DEC DF;

- Also called a When-Else Statement.

- Concurrent statement, thus all signals.

- Similar to a sequential IF-THEN-ELSE statement.

- Select one of several values to drive an output signal.

- Selection based on first condition that is TRUE.

# **Syntax:**

target\_signal <= value1 when condition1 else value2 when condition2 else

value9;

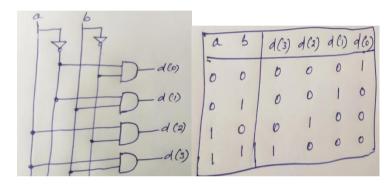

# Example: 2\*4 decoder

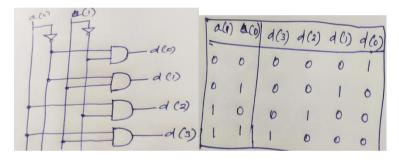

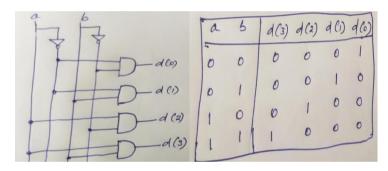

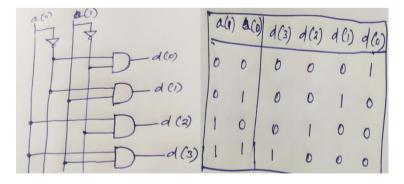

Figure 1.4: 2\*4 decoder logic diagram and truth table

# entity decoder is

```

port (a, b : in std_logic;

d: out std_logic_vector(0 to 3));

end decoder;

architecture DEC_CS of decoder is

```

begin

# Selected Signal Assignment Statement

- Also called a With-Select-When statement.

- Concurrent statement, thus all signals.

- Similar to a sequential CASE statement.

- Select one of several values to drive an output signal.

- Selection based on all possible values of a selector expression.

#### syntax:

with expression select

target\_signal <= value1 when condition1,

value2 when condition2,</pre>

value9 when condition9;

Example: 2\*4 decoder

Figure 1.5: 2\*4 decoder logic diagram and truth table

#### entity decoder is

end DEC\_SS;

# **Behavioral Model**

13.Return Statement

The process statement contains sequential statements that describe the functionality of an entity in sequential terms The sensitivity list is a set of signals which will cause the process to execute in sequential order when an event occurs.

```

Syntax

architecture architecture name of entity name is

begin

process(sensitivity_list)

[variable_declarations;]

begin

sequential assignment statements;

end process;

end architecture name;

Some of the sequential statements in Behavioral model are

1. Variable Assignment Statement

2. Signal Assignment Statement

3. Wait Statement ( wait on, wait until, wait for )

4.If Statement (conditional)

5.Case Statement (Selection)

6.Loop Statement (for loop, while loop, no loop)

7. Null Statement (No operation)

8.Exit Statement (Exit from the loop)

9.Next statement (Exit from one loop, and execute next loop)

10.Assertion Statement (Modelling constrain)

11.Report Statement (Display Message)

12.Procedure call Statement (Linkage)

```

# If statement

# - selects statements for execution based upon a condition

# **Syntax**

```

if condition_1 then

sequential_statement_1;

elsif condition_2 then

sequential_statement_2;

:

else sequential_statement_n;

end if;

```

# Example: 2\*4 decoder

Figure 1.6: 2\*4 decoder logic diagram and truth table

```

entity decoder is

port (a, b : in std_logic; d: out std_logic_vector(0 to 3));

end decoder;

architecture DEC_IF of decoder is

begin

process (a,b)

begin

if (a = '0' and b = '0') then

d <= "0001";

elsif (a = '0' and b = '1') then</pre>

```

```

d <= "0010";

elsif (a = '1' and b = '0') then

d <= "0100";

else d <= "1000";

end if;

end process;

end DEC_IF;</pre>

```

#### **Case statement**

selects one branch of execution from a list of many based upon selected expressionSyntax:

case expression is

```

when choice_1 => statement_1;

when choice_2 => statement_2;

:

when choice_n => statement_n;

end case;

```

Example: 2\*4 decoder

Figure 1.7: 2\*4 decoder logic diagram and truth table

entity decoder is

port (a : in std\_logic\_vector(0 to 1); d: out std\_logic\_vector(0 to 3));

end decoder;

```

begin

process (a)

begin

case a is

when "00" => d <= "0001";

when "01" => d <= "0010";

when "10" => d <= "0100";

```

architecture DEC CASE of decoder is

end case;

end process;

end DEC CASE;

#### TEXT / REFERENCE BOOKS

when "11" => d <= "1000";

- 1. J.Bhaskar, "A VHDL Primer", Prentice Hall of India Limited. 3rd edition 2004

- 2. Stphen Brown, "Fundamental of Digital logic with Verilog Design",3rd edition, Tata McGraw Hill, 2008

- 3. J.Bhaskar, "A Verilog HDL Primer", Prentice Hall of India Limited. 3rd edition 2004

- 4. Samir Palnitkar" Verilog HDL: A Guide to Digital Design and Synthesis", Star Galaxy Publishing; 3rd edition,2005

- 5. Michael D Ciletti Advanced Digital Design with VERILOG HDL, 2nd Edition, PHI, 2009.

- 6. Z Navabi Verilog Digital System Design, 2nd Edition, McGraw Hill, 2005.

- 7. Stuart Sutherland, "RTL Modeling With System Verilog for Simulation and Synthesis: Using System Verilog for ASIC and FPGA Design",1st Edition, Sutherland HDL,Inc., 2017.

- 8. Simon Monk, "Programming FPGAs: Getting Started with Verilog", 1st Edition, Tata McGraw Hill,2016.

- 9. User Guide "7 Series FPGAs Configurable Logic Block" (WWW.XILINX.COM)

(DEEMED TO BE UNIVERSITY)

Accredited "A" Grade by NAAC | 12B Status by UGC | Approved by AICTE

www.sathyabama.ac.in

# SCHOOL OF ELECTRICAL AND ELECTRONICS

# DEPARTMENT OF ELECTRONICS AND COMMMUNICATION ENGINEERING

# UNIT - II PROGRAMMING IN HDL – SEC1406

#### II. INTRODUCTION TO VERILOG HDL

Verilog HDL is a hardware description language that can be used to model a digital system at many levels of abstraction ranging from the algorithmic level to the gate level to the switch level. The complexity of the digital system being modeled could vary from that of a simple gate to a complete electronic digital system, or anything in between. The digital system can be described hierarchically and timing can be explicitly modeled within the same description.

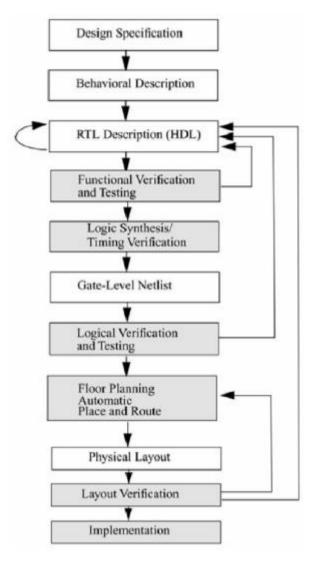

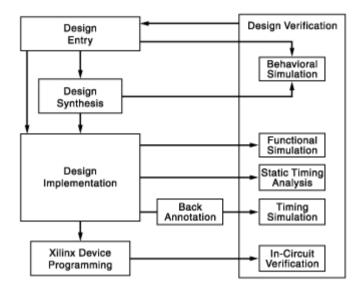

## **Typical Design Flow**

A typical design flow for designing VLSI IC circuits is shown in Figure 2.1. Un shaded blocks show the level of design representation; shaded blocks show processes in the design flow.

The design flow shown in Figure 2.1 is typically used by designers who use HDLs. In any design, specifications are written first. Specifications describe abstractly the functionality, interface, and overall architecture of the digital circuit to be designed. At this point, the architects do not need to think about how they will implement this circuit. A behavioral description is then created to analyze the design in terms of functionality, performance, compliance to standards, and other high-level issues.

#### Behavioral descriptions are often written with HDLs

The behavioral description is manually converted to an RTL description in an HDL. The designer has to describe the data flow that will implement the desired digital circuit. From this point onward, the design process is done with the assistance of EDA tools.

Logic synthesis tools convert the RTL description to a gate-level netlist. A gatelevel netlist is a description of the circuit in terms of gates and connections between them. Logic synthesis tools ensure that the gate-level netlist meets timing, area, and power specifications. The gate-level netlist is input to an Automatic Place and Route tool, which creates a layout. The layout is verified and then fabricated on a chip.

Figure 2.1: Typical Design Flow

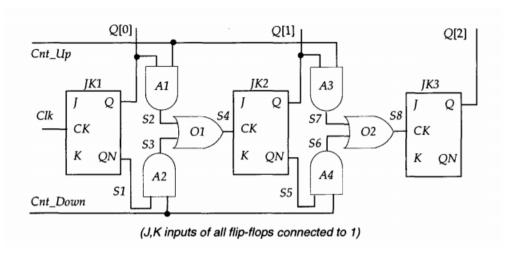

#### **Design Methodologies**

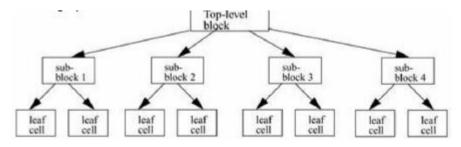

There are two basic types of digital design methodologies: a top-down design methodology and a bottom-up design methodology. In a top-down design methodology, we define the top-level block and identify the sub-blocks necessary to build the top-level block. We further subdivide the sub-blocks until we come to leaf cells, which are the cells that cannot further be divided. Figure 2.2 shows the top-down design process.

Figure 2.2: Top-down Design Methodology

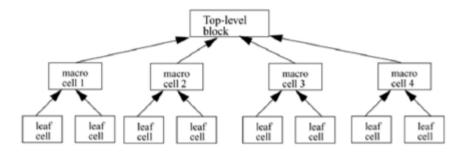

In a bottom-up design methodology, we first identify the building blocks that are available to us. We build bigger cells, using these building blocks. These cells are then used for higher-level blocks until we build the top-level block in the design. Figure 2.3 shows the bottom-up design process

Figure 2.3: Bottom-up Design Methodology

#### Levels for design description

Verilog supports designing at many different levels of abstraction. Three of them are very important:

- Behavioral level

- Register-Transfer Level

- Gate Level

#### **Behavioral Level**

This level describes a system by concurrent algorithms (Behavioral). Each algorithm itself is sequential, that means it consists of a set of instructions that are executed one after the other. Functions, Tasks and Always blocks are the main elements. There is no regard to the structural realization of the design.

#### **Register-Transfer Level**

Designs using the Register-Transfer Level specify the characteristics of a circuit by operations and the transfer of data between the registers. An explicit clock is used. RTL design contains exact timing bounds: operations are scheduled to occur at certain times. Modern RTL code definition is "Any code that is synthesizable is called RTL code".

# **Gate Level**

Within the logic level the characteristics of a system are described by logical links and their timing properties. All signals are discrete signals. They can only have definite logical values ('0', '1', 'X', 'Z'). The usable operations are predefined logic primitives (AND, OR, NOT etc gates). Using gate level modeling might not be a good idea for any level of logic design. Gate level code is generated by tools like synthesis tools and this netlist is used for gate level simulation and for backend.

# **Language Elements**

# **Identifiers**

Identifiers are names given to objects so that they can be referenced in the design. Identifiers are made up of alphanumeric characters, the underscore ( \_ ), or the dollar sign ( \$ ). Identifiers are case sensitive. Identifiers start with an alphabetic character or an underscore. They cannot start with a digit or a \$ sign

reg value; // reg is a keyword; value is an

identifier input clk; // input is a keyword, clk is an identifier

#### **Comments**

Comments can be inserted in the code for readability and documentation. There are two ways to write comments. A one-line comment starts with "//". Verilog skips from that point to the end of line. A multiple-line comment starts with "/\*" and ends with "\*/". Multiple-line comments cannot be nested. However, one-line comments can be embedded in multiple-line comments.

```

a = b && c; // This is a one-line comment

/* This is a multiple line comment */

/* This is /* an illegal */ comment */

/* This is //a legal comment */

```

#### **Format**

Verilog HDl is case sensitive. Identifiers differing only in their case are distinct. Verilog HDL, is free format, constructs may be written across multiple lines, or on one line. White space (newline, tab, and space characters) have no special significance.

# **System Tasks and Functions**

Verilog provides standard system tasks for certain routine operations. All system tasks appear in the form \$<keyword>. Operations such as displaying on the screen, monitoring values of nets, stopping, and finishing are done by system tasks.

#### **Compiler Directives**

Compiler directives are provided in Verilog. All compiler directives are defined by using the '<keyword> construct. We deal with the two most useful compiler directives.

'define

The 'define directive is used to define text macros in Verilog.

The Verilog compiler substitutes the text of the macro wherever it encounters a '<macro\_name>. This is similar to the #define construct in C. The defined constants or text macros are used in the Verilog code by preceding them with a ' (back tick).

//define a text macro that defines default word

size //Used as 'WORD\_SIZE in the code

'define WORD SIZE 32

'include

The 'include directive allows you to include entire contents of a Verilog source file in another Verilog file during compilation. This works similarly to the #include in the C programming language. This directive is typically used to include header files, which typically contain global or commonly used definitions.

**Example 'include Directive**

// Include the file header.v, which contains declarations in the

// main verilog file design.v.

'include header.v

•••

<Verilog code in file design.v>

•••

Two other directives, 'ifdef and 'timescale, are used frequently.

#### Value set

Verilog supports four values and eight strengths to model the functionality of real hardware.

# **Strength levels**

| Value Level | Condition in Hardware Circuits |  |  |  |

|-------------|--------------------------------|--|--|--|

| 0           | Logic zero, false condition    |  |  |  |

| 1           | Logic one, true condition      |  |  |  |

| x           | Unknown logic value            |  |  |  |

| z           | High impedance, floating state |  |  |  |

# **Data types**

Verilog HDL has two groups of data types

### (i) Net type

A net type represents a physical connection between structural elements. Its value is determined from the value of its drivers such as a continuous assignment or a gate output. If no driver is connected to a net, the net defaults to a value of z.

# (ii) Variable type

A variable type represents an abstract data storage element. It is assigned values only within an always statement or an initial statement, and its value is saved from one assignment to the next. A variable type has a default value of x.

**Net types**

| Here are the | different | kinda  | ۸f | note | that | holong | to | tha  | not | data | trm | _ |

|--------------|-----------|--------|----|------|------|--------|----|------|-----|------|-----|---|

| mere are und | umerem    | Killus | UΙ | Hers | шаі  | neiong | w  | uic. | псі | uata | typ | C |

wire

tri

wor

trior

wand

triand

trireg

tri1

tri0

supply0

#### supply1

#### Variable types

There are five different kinds of variable types

reg

integer

time

real

realti

me

#### **Register**

Registers represent data storage elements. Registers retain value until another value is placed onto them. Register data types are commonly declared by the keyword reg. The default value for a reg data type is x.

**Example of Register**

reg reset; // declare a variable reset that can hold its value

begin

reset = 1'b1; //initialize reset to 1 to reset the digital circuit.

#100 reset = 1'b0; // after 100 time units reset is de asserted.

end

#### Integer

An integer is a general purpose register data type used for manipulating quantities. Integers are declared by the keyword integer. Although it is possible to use reg as a general-purpose variable, it is more convenient to declare an integer variable for purposes such as counting. The default width for an integer is the host-machine word size, which is implementation-specific but is at least 32 bits. Registers declared as data type reg store values as unsigned quantities, whereas integers store values as signed quantities.

integer counter; // general purpose variable used as a counter.

initial counter = -1; // A negative one is stored in the counter

#### Real

Real number constants and real register data types are declared with the keyword real. They can be specified in decimal notation (e.g., 3.14) or in scientific notation (e.g., 3e6, which is  $3 \times 106$ ). Real numbers cannot have a range declaration, and their default value is 0. When a real value is assigned to an integer, the real number is rounded off to the nearest integer.

```

real delta; // Define a real variable called delta

initial

begin

delta = 4e10; // delta is assigned in scientific notation delta = 2.13;

// delta is assigned a value 2.13

end

integer i; // Define an integer i initial

i = delta; // i gets the value 2 (rounded value of 2.13)

```

#### Time

Verilog simulation is done with respect to simulation time. A special time register data type is used in Verilog to store simulation time. A time variable is declared with the keyword time. The width for time register data types is implementation specific but is at least 64 bits. The system function \$\\$time is invoked to get the current simulation time.

```

time save_sim_time; // Define a time variable save_sim_time

initial save_sim_time = $time; // Save the current simulation time

```

#### **Arrays**

Arrays are allowed in Verilog for reg, integer, time, real, realtime and vector register data types. Multi-dimensional arrays can also be declared with any number of dimensions. Arrays of nets can also be used to connect ports of generated instances. Each element of the array can be used in the same fashion as a scalar or vector net. Arrays are accessed by <array\_name>[<subscript>]. For multi-dimensional arrays, indexes need to be provided for each dimension.

```

integer count[0:7]; // An array of 8 count variables

reg bool[31:0]; // Array of 32 one-bit boolean register variables time

chk_point[1:100]; // Array of 100 time checkpoint variables

reg [4:0] port_id[0:7]; // Array of 8 port_ids; each port_id is 5 bits wide

```

#### **Parameters**

Verilog allows constants to be defined in a module by the keyword parameter. Parameters cannot be used as variables. Parameter values for each module instance can be overridden individually at compile time. This allows the module instances to be customized. This aspect is discussed later. Parameter types and sizes can also be defined.

```

parameter port_id = 5; // Defines a constant port_id

parameter cache_line_width = 256; // Constant defines width of cache line

parameter signed [15:0] WIDTH; // Fixed sign and range for parameter WIDTH

```

#### **Expressions**

An expression is formed using operands and operators. An expression can be used wherever a value is expected.

#### **Operands**

Operands can be constants, integers, real numbers, nets, registers, times, bitselect (one bit of vector net or a vector register), part-select (selected bits of the vector net or register vector), and memories or function calls.

```

integer count, final_count;

final_count = count + 1;//count is an integer operand

real a, b, c;

c = a - b; //a and b are real operands

reg [15:0] reg1,

reg2; reg [3:0]

reg_out;

reg_out = reg1[3:0] ^ reg2[3:0];//reg1[3:0] and reg2[3:0] are //part-select register operands

reg ret_value;

ret_value = calculate_parity(A, B);//calculate_parity is a //function type operand

```

## **Operator Types**

Verilog provides many different operator types. Operators can be arithmetic, logical, relational, equality, bitwise, reduction, shift, concatenation, or conditional. Some of these

operators are similar to the operators used in the C programming language. Each operator type is denoted by a symbol. The table 2.1 shows the complete listing of operator symbols classified by category.

**Table 2.1 Operators**

| Operator Type | Operator Symbol | Operation Performed   | Number of Operands |  |  |

|---------------|-----------------|-----------------------|--------------------|--|--|

| Arithmetic    | *               | multiply              | two                |  |  |

|               | 1               | divide                | two                |  |  |

|               | +               | add                   | two                |  |  |

|               | -               | subtract              | two                |  |  |

|               | %               | modulus               | two                |  |  |

|               | **              | power (exponent)      | two                |  |  |

| Logical       | !               | logical               | one                |  |  |

|               | &&              | negation              | two                |  |  |

|               | II              | logical and           | two                |  |  |

| Relational    | >               | greater               | two                |  |  |

|               | <               | than less             | two                |  |  |

|               | >=              | than                  | two                |  |  |

|               | <=              | greater than or equal | two                |  |  |

| Equality      | ==     | equality               | two        |

|---------------|--------|------------------------|------------|

|               | ļ=     | inequality case        | two        |

|               | ===    | equality               | two        |

|               | ļ==    | case inequality        | two        |

|               | ~      | bitwise                | one        |

|               | &      | negation               | two        |

| Bitwise       |        | bitwise and            | two        |

|               | A      | bitwise or             | two        |

|               | &      | reduction and          | one        |

|               | ~&     | reduction nand         | one        |

| Reduction     |        | reduction or           | one        |

|               | <br> ~ | reduction nor          | one        |

|               | >>     | Right shift            | Two        |

| Shift         | <<     | Left shift             | Two        |

|               | >>>    | Arithmetic right shift | Two        |

|               | <<<    | Arithmetic left shift  | Two        |

|               |        |                        |            |

| Concatenation | {}     | Concatenation          | Any number |

| Replication   | {{}}   | Replication            | Any number |

| Conditional   | ?:     | Conditional            | Three      |

# **Module**

The basic unit of description in Verilog is the module. A module describes the functionality or structure of a design and also describes the ports through which it communicates externally with other modules. The structure of a design is described using switch-level primitives, gate-level primitives and user-defined primitives; data flow behavior of a design is described using continuous assignments; sequential behavior is described using procedural constructs. A module can also be instantiated inside another module.

module module\_name (port\_list );

**Declarations:**

reg, wire,

parameter, input, output, inout, function, task, ....

**Statements:**

**Initial statement**

**Always statement**

**Module instantiation**

**Gate instantiation**

**UDP** instantiation

Continuous assignment

**Generate statement**

end module

#### TEXT / REFERENCE BOOKS

- 1. J.Bhaskar, "A VHDL Primer", Prentice Hall of India Limited. 3rd edition 2004

- 2. Stphen Brown, "Fundamental of Digital logic with Verilog Design",3rd edition, Tata McGraw Hill, 2008

- 3. J.Bhaskar, "A Verilog HDL Primer", Prentice Hall of India Limited. 3rd edition 2004

- 4. Samir Palnitkar" Verilog HDL: A Guide to Digital Design and Synthesis", Star Galaxy Publishing; 3rd edition,2005

- 5. Michael D Ciletti Advanced Digital Design with VERILOG HDL, 2nd Edition, PHI, 2009.

- 6. Z Navabi Verilog Digital System Design, 2nd Edition, McGraw Hill, 2005.

- 7. Stuart Sutherland, "RTL Modeling With System Verilog for Simulation and Synthesis: Using System Verilog for ASIC and FPGA Design",1st Edition, Sutherland HDL,Inc., 2017.

- 8. Simon Monk, "Programming FPGAs: Getting Started with Verilog", 1st Edition, Tata McGraw Hill,2016.

- 9. User Guide "7 Series FPGAs Configurable Logic Block" (WWW.XILINX.COM)

(DEEMED TO BE UNIVERSITY)

Accredited "A" Grade by NAAC | 12B Status by UGC | Approved by AICTE

www.sathyabama.ac.in

# SCHOOL OF ELECTRICAL AND ELECTRONICS

# DEPARTMENT OF ELECTRONICS AND COMMMUNICATION ENGINEERING

# UNIT - III PROGRAMMING IN HDL – SEC1406

# III. STYLES OF MODELING

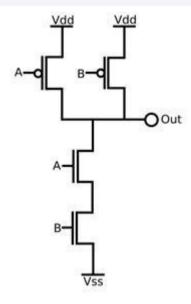

# **Gate Level Modeling:**

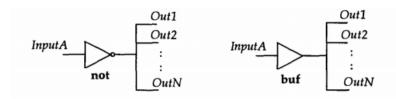

The Built-in Primitive Gates:

The following built-in primitive gates are available in Verilog HDL.

- i. Multiple-input gates: and, nand, or,nor,xor,xnor

- ii. Multiple-output gates: buf, not

- iii. Tristate gates: buflfO, bufifl, notifO, notifl

- iv. Pull gates: pullup, pulldown 70 Multiple-input

- v. MOS switches: cmos, nmos, pmos, rcmos, rnmos, rpmos

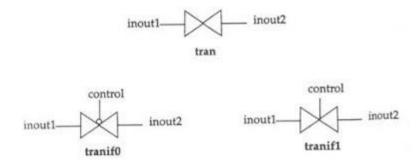

- vi. Bidirectional switches: tran, tranifO, tranifl, rtran, rtranifO,rtranifl

A gate can be used in a design using a gate instantiation. Here is a simple format of a gate instantiation.

```

gate_type[ instance_name ] ( terml , term2 , . . . , termN);

```

Note that the instance\_name is optional; gate type is one the gates listed earlier. The terms specify the nets and registers connected to the terminals of the gate. Multiple instances of the same gate type can be specified in one construct. The syntax for this is the following.

```

gate type

```

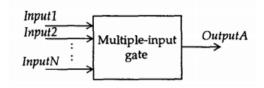

# **Multiple-input Gates:**

The multiple-input built-in gates are: and nand nor or xorxnor. These logic gates have only one output and one or more inputs. Here is the syntax of a multiple-input gate instantiation.

```

multiple_input_gate_type I instance_name ] ( OutputA , Input 1 , Input2,..., InputN );

```

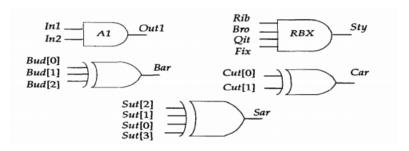

The first terminal is the output and all others are the inputs. Here are some examples. The logic diagrams are shown in figure 3.1.

**Figure 3.1: Multiple Input Gates**

```

and A1 (Outl, Inl, In2);

and RBX (Sty, Rib, Bro, Qit, Fix);

xor (Bar, Bud[0],Bud[1],Bud[2]),

(Car, Cut[0], Cut[1]),

(Sar, Sut[2], Sut[1], Sut[0], Sut[3]);

```

Figure 3.2: Multiple Input Gate examples

The first gate instantiation is a 2-input and gate with instance name Al, output Outl and with two inputs, Inl and Inl. The second gate instantiation is a 4-input and gate with instance name RBX, output Sty and four inputs, Rib, Bro, Qit and Fix. The third gate instantiation is an example of anxor gate with no instance name. Its output is Bar and it has three inputs, Bud[0],Bud[1] and Bud[2]. Also, this instantiation has two additional instances of the same type.

The truth tables for these gates are shown next. Notice that a value z at an input is handled like an x; additionally, the output of a multiple-input gate can never be a z.

| nand | 0   | 1 | x | z | and  | 0   | 1 | x |  |

|------|-----|---|---|---|------|-----|---|---|--|

| 0    | 1   | 1 | 1 | 1 | 0    | 0   | 0 | 0 |  |

| 1    | 1   | 0 | x | x | 1    | 0   | 1 | x |  |

| x    | 1   | x | x | x | x    | 0   | x | x |  |

| z    | 1   | x | х | x | z    | 0   | x | х |  |

|      |     |   |   |   |      |     |   |   |  |

| or   | 0   | 1 | x | z | nor  | 0   | 1 | x |  |

| 0    | 0   | 1 | x | x | 0    | 1   | 0 | х |  |

| 1    | 1   | 1 | 1 | 1 | . 1  | 0   | 0 | 0 |  |

| x    | x   | 1 | x | x | x    | x   | 0 | x |  |

| z    | x   | 1 | х | x | z    | x   | 0 | х |  |

| xor  | 1 0 | 1 | x | z | xnor | 1 0 | 1 | x |  |

| 0    | 0   | 1 | x | x | 0    | 1   | 0 | x |  |

| 1    | 1   | 0 | x | x | 1    | 0   | 1 | x |  |

| X    | x   | x |   |   | x    | x   | x | x |  |

|      | X   |   | x | x | ^    | 1 ^ | ^ | ^ |  |

Figure 3.3: Truth table Multiple input gates

# **Multiple-output Gates:**

The multiple-output gates are: buf & not

These gates have only one input and one or more outputs. The basic syntax for this gate instantiation is:

multiple\_output\_gate\_type

[instance\_name] (Outl, Out2,..., OutN, InputA);

The last terminal is the input; all remaining terminals are the outputs.

Figure 3.4: Multiple Output Gates

Here are some examples.

bufBl [Fan[0], Fan[1], Fan[2],Fan[3],Clk);

notNl {PhA, PhB, Ready);

In the first gate instance, Clk is the input to the buf gate; this gate instance has four outputs, Fan[0] through Fan[3]. In the second gate instance, Ready is the only input to the not gate. This instance has two outputs, PhA and PhB. The truth table for these gates are shown next.

| buf      | 0 | 1 | x | z | not      | 0 | 1 | x | z |

|----------|---|---|---|---|----------|---|---|---|---|

| (output) | 0 | 1 | х | х | (output) | 1 | 0 | х | x |

Figure 3.5: Truth table of Multiple output Gates

# **Tristate Gates:**

The tristate gates are: bufifO, bufifl, notifO, notifl

These gates model three-state drivers. These gates have one output, one data input and one control input. Here is the basic syntax of a tristate gate instantiation.

tristate\_gate[ instance\_name] (OutputA, InputB, ControlC);

The first terminal OutputA is the output, the second terminal InputB is the data input, and the control input is ControlC. Depending on the control input, the output can be driven to the high-impedance state, that is, to value z. For a bufifO gate, the output is z if control is 1,else data is transferred to output. For a bufifl gate, output is a z if control is 0. For a notifO gate, output is at z if control is at 1 else output is the invert of the input data value. For notifl gate, output is at z if control is at 0.

Figure 3.6: Tristate Gates

Here are some examples.

bufifl BF1 [Dbus, MemData, Strobe);

notifO NT2 {Addr, Abus, Probe); The bufifl gate BF1 drives the output Dbus to high-impedance state when Strobe is 0, elseMemData is transferred to Dbus. In the second instantiation, when Probe is 1, Addr is in high-impedance state, else Addr gets the inverted value of Abus. The truth tables for these gates are shown next. Some entries in the table indicate alternate entries. For example, 0/z indicates that the output can either be a 0 or a z depending on the strengths of the data and control values.

| bufif0 |   |   | Co | ntrol |      | bufif1 Con |   |   |   | ntrol |      |

|--------|---|---|----|-------|------|------------|---|---|---|-------|------|

|        |   | 0 | 1  | х     | z    |            |   | 0 | 1 | х     | z    |

|        | 0 | 0 | z  | 0/z   | 0/ z |            | 0 | z | 0 | 0/ z  | 0/ 2 |

| Data   | 1 | 1 | z  | 1/z   | 1/ z | Data       | 1 | z | 1 | 1/ z  | 1/2  |

|        | x | x | z  | x     | x    |            | x | z | x | x     | x    |

|        | z | x | z  | x     | x    |            | z | z | x | x     | x    |

| notif0 |   | 2005 | Co | ntrol |      | noti | notif1 Control |   |   |      |      |

|--------|---|------|----|-------|------|------|----------------|---|---|------|------|

|        |   | 0    | 1  | х     | z    |      |                | 0 | 1 | х    | z    |

|        | 0 | 1    | z  | 1/ z  | 1/ z |      | 0              | z | 1 | 1/ z | 1/2  |

| Data   | 1 | 0    | z  | 0/ z  | 0/ z | Data | 1              | z | 0 | 0/ z | 0/ z |

|        | x | x    | z  | x     | x    |      | х              | z | x | x    | x    |

|        | z | x    | z  | x     | x    |      | z              | z | x | x    | x    |

Figure 3.7: Truth table for Tristate Gates

#### **Pull Gates:**

The pull gates are: pullup & pulldown

These gates have only one output with no inputs. A pull up gate places a 1 on its output. A pull down gate places a 0 on its output. A gate instantiation is of the form:

pull gate I instance name ] ( Outputs );

The terminal list of this gate instantiation contains only one output. Here is an example.

pullup PUP (Pwr);

This pullup gate has instance name PUP with output Pwr tied to 1.

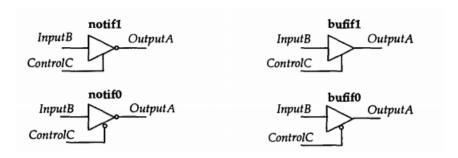

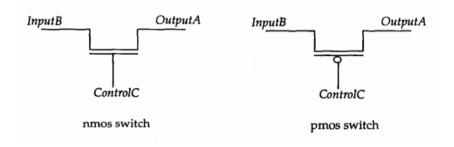

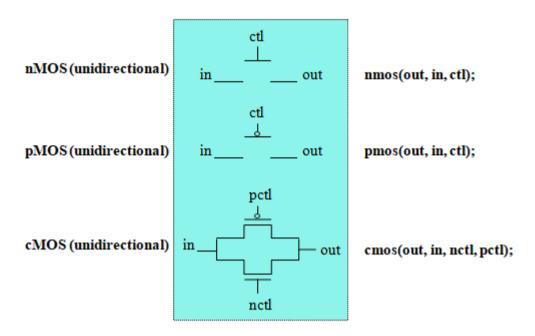

#### **MOS Switch:**

The MOS switches are: cmos, pmos, nmos, rcmos, rpmos, rnmos.

These gates model unidirectional switches, that is, data flows from input to output and the data flow can be turned off by appropriately setting the control input(s).

The pmos(p-type MOS transistor), nmos (n-type MOS transistor), rnmos ('r' stands for resistive) and rpmos switches have one output, one input and one control input. The basicsyntax for an instantiation is:

gate type[instance name](Outputs, InputB, ControlC);

The first terminal is the output, the second terminal is the input and the last terminal is the control. If controlis 0 for nmos and rnmos switches and 1 for pmos and rpmos switches, the switch is turned off, that is, output has value z; if control is 1, data at input passes to output; see Figure 5-5. The resistive switches (rnmos and rpmos) have a higher impedance(resistance) between the input and output terminals as compared to the non-resistive switches (nmos and pmos). Thus when data passes from input to output, a reduction in strength occurs for resistive switches.

Figure 3.8: nMOS and pMOS switches

Here are some examples.

pmos P1 {BigBus, SmallBus, GateControl);

rnmos RN1 [ControlBit, ReadyBit, Hold);

The first instance instantiates a pmos switch with instance name P1. The input to the switch is SmallBus and the output is BigBus and the control signal is Gate Control. The truth tables for these switches are shown next. Some entries in the table indicate alternate entries. For example, 1/z indicates that the output can be either 1 or z depending on the input and control.

| pmos<br>rpmos |   |   | Co | ntrol |      | nmos |     | Control |   |      |      |

|---------------|---|---|----|-------|------|------|-----|---------|---|------|------|

|               |   | 0 | 1  | х     | z    | rnn  | 105 | 0       | 1 | х    | z    |

|               | 0 | 0 | z  | 0/z   | 0/ z |      | 0   | z       | 0 | 0/ z | 0/   |

| Data          | 1 | 1 | z  | 1/z   | 1/ z | Data | 1   | z       | 1 | 1/ z | 1/ : |

|               | x | x | z  | x     | x    |      | x   | z       | x | x    | x    |

|               | z | z | z  | z     | z    |      | z   | z       | z | z    | z    |

Figure 3.9: Truth table of MOS switches

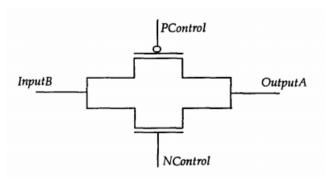

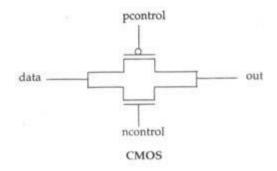

The CMOS (Complimentary MOS) and rcmos (resistive version of cmos) switches have one data output, one data input and two control inputs. The syntax for instantiating these two switches is of the form:

(r)cmos [instance name] (OutputA, InputB, NControl, PControl);

The first terminal is the output, the second is the input, the third is the n channel control input and the fourth terminal is the p-channel control input. A cmos (rcmos) switch behaves exactly like a combination of a pmos (rpmos) and an nmos (rnmos) switch with common outputs and common inputs.

Figure 3.10: (r)cmos switch

#### **Bidirectional Switch:**

The bidirectional switches are: tran, rtran, tranifO, rtranifO, tranifl, rtranifl

These switches are bidirectional, that is, data flows both ways and there is no delay when data propagates through the switches. The last four switches can be turned off by setting a control signal appropriately. The tran and rtran switches cannot be turned off. The syntax for instantiating a tran or a rtran (resistive version of tran) switch is:

(r)tran [ instance\_name ] ( SignalA , SignalB);

The terminal list has only two terminals and data flows unconditionally both ways, that is, from SignalA to SignalB and vice versa. The syntax for instantiating the other bidirectional switches is:

gate type[instance name](SignalA, SignalB, ControlC);

The first two terminals are the bidirectional terminals, that is, data flows from SignalA to SignalB and vice versa. The third terminal is the control signal. If ControlC is 1for tranifO and rtranifO, and 0 for tranifl and rtranifl, the bidirectional data flow is disabled. For the resistive switches(rtran, rtranifO and rtranifl), the strength of the signal reduces when it passes through the switch.

# **Examples:**

# 4 X 1 Multiplexer:

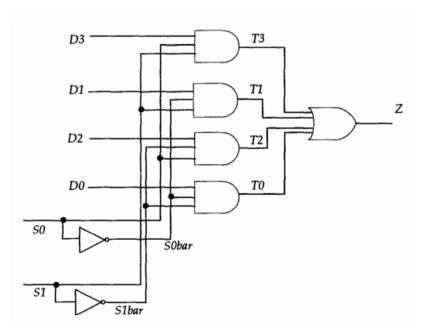

Figure 3.11: 4 X 1 Multiplexer

moduleMUX4x1 (Z, DO, Dl, D2, D3, SO, Si); output Z;

```

input DO, Dl, D2, D3, SO, SI;

and (TO, DO, SObar, Slbar),

(Tl, Dl, SObar, S1),

(T2, D2, SO, Slbar),

(T3, D3, SO, S1);

not (SObar, SO),

(Slbar, S1);

or (Z, TO, Tl, T2, T3);

endmodule

```

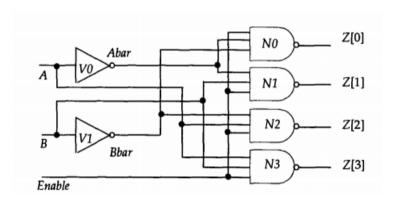

# 2 to 4 Decoder:

Figure 3.12: 2 to 4 Decoder

```

module DEC2x4 {A, B, Enable, Z);

input A, B, Enable;

output [0:3] Z;

wireAbar, Bbar;

not

V0 (Abar, A),

V1 (Bbar, B);

nand

NO (Z[0], Enable, Abar, Bbar),

N1 (Z[1], Enable, A, Bbar),

```

# N3 (Z[3] , Enable, A, B);

# endmodule

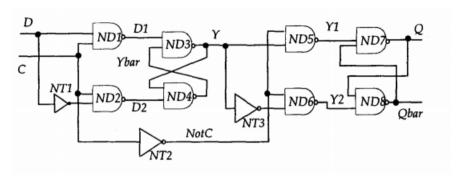

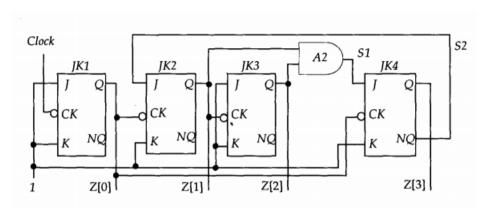

# **Master Slave Flip-flop:**

Figure 3.13: Master Slave Flip-flop

```

module MSDFF (D, C, Q, Qbar);

input D, C; output Q, Qbar;

not

NT1 (NotD, D),

NT2 (NotC, C),

NT3 (NotY, Y);

nand

ND1 (Dl, D, C),

ND2 (D2, C, NotD),

ND3 (Y, Dl, Ybar),

ND4 (Ybar, Y, D2),

ND5 (Yl, Y, NotC),

ND6 (Y2, NotY, NotC),

ND7 (Q, Qbar, Yl), ND8 (Qbar, Y2, Q);

endmodule

```

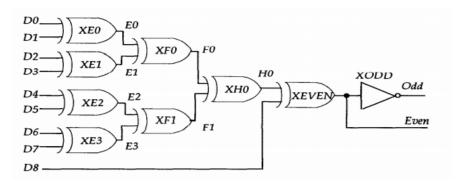

# **Parity Generator:**

Figure 3.14: Parity Generator

# **USER-DEFINED PRIMITIVES (UDP):**

The primitives available in Verilog are the entire gate or switch types. Verilog has the provision for the user to define primitives —called "user defined primitive (UDP)" and use them. The designers occasionally like to use their own custom-built primitives when developing a design. Verilog provides the ability to define User- Defined Primitives (UDP). These primitives are self contained and do not instantiate other modules or primitives. UDPs are instantiated exactly like gate level primitives. UDPs are basically of two types — combinational and sequential. A combinational UDP is used to define a combinational scalar

function and a sequential UDP for a sequential function.

# **Combinational UDPs:**

A combinational UDP accepts a set of scalar inputs and gives a scalar output. An input declaration is not supported by a UDP. The UDP definition is on par with that of a module; that is, it is defined independently like a module and can be used in any other module.

```

primitiveudp_and(out, a, b);

output out;

input a, b;

table

// a b: Out;

0 0: 0;

0 1: 0;

1 0: 0

1 1: 1;

endtable

endprimitive

```

# **Sequential UDPs:**

110:?:1;

Any sequential circuit has a set of possible states. When it is in one of the specified states, the next state to be taken is described as a function of the input logic variables and the present state. A sequential UDP can accommodate all these.

//latchq =data=1

# **Dataflow Modeling:**

For small circuits, the gate-level modeling approach works very well because the numbers of gates is limited and the designer can instantiate and connect every gate individually. Also, gate-level modeling is very intuitive to a designer with a basic knowledge of digital logic design. However, in complex designs the number of gates is very large. Thus, designers can design more effectively if they concentrate on implementing the function at a level of abstraction higher than gate level. Dataflow modeling provides a powerful way to implement a design. Verilog allows a circuit to be designed in terms of the data flow between registers and how a design processes data rather than instantiation of individual gates. Later in this chapter, the benefits of dataflow modeling will become more apparent.

With gate densities on chips increasing rapidly, dataflow modeling has assumed great importance. No longer can companies devote engineering resources to handcrafting entire designs with gates. Currently, automated tools are used to create a gate-level circuit from a dataflow design description. This process is called logic synthesis. Dataflow modeling has become a popular design approach as logic synthesis tools have become sophisticated. This approach allows the designer to concentrate on optimizing the circuit in terms of data flow. For maximum flexibility in the design process, designers typically use a Verilog description style that combines the concepts of gate-level, data flow, and behavioral design. In the digital design community, the term RTL (Register Transfer Level) design is commonly used for a combination of dataflow modeling and behavioral modeling.

#### **Continuous Assignments:**

A continuous assignment is the most basic statement in dataflow modeling, used to drive a value onto a net. This assignment replaces gates in the description of the circuit and describes the circuit at a higher level of abstraction. The assignment statement starts with the keyword assign. The syntax of an assign statement is as follows.

```

continuous_assign ::= assign [ drive_strength ] [ delay3 ] list_of_net_assignments ;

list_of_net_assignments ::= net_assignment { , net_assignment }

net_assignment ::= net_lvalue = expression

```

Notice that drive strength is optional and can be specified in terms of strength levels. The

default value for drive strength is strong1 and strong0. The delay value is also optional and can be used to specify delay on the assign statement. This is like specifying delays for gates. Delay specification is discussed in this chapter. Continuous assignments have the following characteristics:

- 1. The left hand side of an assignment must always be a scalar or vector net or a concatenation of scalar and vector nets. It cannot be a scalar or vector register.

- 2. Continuous assignments are always active. The assignment expression is evaluated as soon as one of the right-hand-side operands changes and the value is assigned to the left-hand-side net.

- 3. The operands on the right-hand side can be registers or nets or function calls. Registers or nets can be scalars or vectors.

- 4. Delay values can be specified for assignments in terms of time units. Delay values are used to control the time when a net is assigned the evaluated value. This feature is similar to specifying delays for gates. It is very useful in modeling timing behavior in real circuits.

#### **Examples of Continuous Assignment:**

Continuous assign - Out is a net. i1 and i2 are nets.

assign out = i1 & i2;

Continuous assign for vector nets - addr is a 16-bit vector net addr1 and addr2 are 16-bit vector registers.

assignaddr[15:0] = addr1 bits[15:0] ^ addr2 bits[15:0];

Concatenation - Left-hand side is a concatenation of a scalar net and a vector net.

assign  $\{c\_out, sum[3:0]\} = a[3:0] + b[3:0] + c\_in;$

# **Implicit Continuous Assignment:**

Instead of declaring a net and then writing a continuous assignment on the net, Verilog provides a shortcut by which a continuous assignment can be placed on a net when it is declared. There can be only one implicit declaration assignment per net because a net is declared only once.

In the example below, an implicit continuous assignment is contrasted with a regular continuous assignment.

//Regular continuous assignment

wire out;

assign out = in1 & in2;

//Same effect is achieved by an implicit continuous assignment wire out = in1 & in2;

# **Implicit Net Declaration**

If a signal name is used to the left of the continuous assignment, an implicit net declaration will be inferred for that signal name. If the net is connected to a module port, the width of the inferred net is equal to the width of the module port.

wire i1, i2;

assign out = i1 & i2; //Note that out was not declared as a wire

//but an implicit wire declaration for out //is done by the simulator

# **Delays**

Delay values control the time between the change in a right-hand-side operand and when the new value is assigned to the left-hand side. Three ways of specifying delays in continuous assignment statements are regular assignment delay, implicit continuous assignment delay, and net declaration delay.

#### **Regular Assignment Delay**

The first method is to assign a delay value in a continuous assignment statement. The delay value is specified after the keyword assign. Any change in values of in1 or in2 will result in a delay of 10 time units before recomputation of the expression in1 & in2, and the result will be assigned to out. If in1 or in2 changes value again before 10 time units when the result propagates to out, the values of in1 and in2 at the time of recomputation are considered. This property is called inertial delay. An input pulse that is shorter than the delay of the assignment statement does not propagate to the output.

assign #10 out = in1 & in2; // Delay in a continuous assign

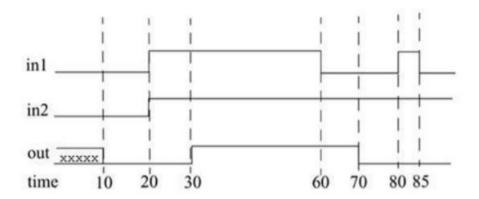

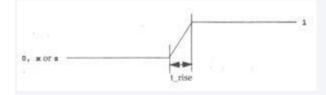

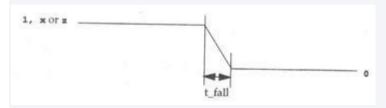

Figure 3.15: Delays

The above waveform is generated by simulating the above assign statement. It shows the delay on signal out. Note the following change:

When signals in 1 and in 2 go high at time 20, out goes to a high 10 time units later (time = 30).

When in 1 goes low at 60, out changes to low at 70.

However, in1 changes to high at 80, but it goes down to low before 10 time units have elapsed.

Hence, at the time of recomputation, 10 units after time 80, in1 is 0. Thus, out gets the value 0. A pulse of width less than the specified assignment delay is not propagated to the output.

# **Implicit Continuous Assignment Delay**

An equivalent method is to use an implicit continuous assignment to specify both a delay and an assignment on the net.

//implicit continuous assignment delay

wire #10 out = in1 & in2;

//same as wire out;

assign #10 out = in1 & in2;

The declaration above has the same effect as defining a wire out and declaring a continuous assignment on out.

# **Net Declaration Delay:**

A delay can be specified on a net when it is declared without putting a continuous assignment on the net. If a delay is specified on a net out, then any value change applied to the net out is delayed accordingly. Net declaration delays can also be used in gate-level modeling.

//Net Delays

```

wire # 10 out;

assign out = in1 \& in2;

//The above statement has the same effect as the following.

wire out;

assign #10 out = in1 & in2;

Examples

Master Slave Flip-flop:

module MSDFF_DF (D, C, Q, Qbar);

input D, C; output Q, Qbar;

wireNotC, NotD, NotY, Y, Dl, D2, Ybar, Yl, Y2;

assignNotD = \sim D;

assign Note = \sim C;

assignNotY = \sim Y;

assign D1= - (D \& C);

assign D2 = \sim (C \& NotD);

assign Y = \sim (Dl St Ybar);

assignYbar = \sim (Y \& D2);

assignYl = \sim (v \& Note);

assign Y2 = -(NotY\&NotC);

assign Q = \sim (Qbar&Yl);

assignQbar = \sim (Y2 & Q);

endmodule

8 bit Magnitude Comparator:

moduleMagnitudeComparator (A, B, AgtB, AeqB, AltB);

parameter BUS= 8;

parameter EQ_DELAY = 5, LT_DELAY = 8, GT_DELAY = 8;

input [1: BUS]A, B;

outputAgtB, AeqB, AltB;

assign %EQ_DELAY AeqB = A == B;

```

```

assign $GT_DELAY AgtB = A > B;

assign $LT_DELAY AltB = A < B;

endmodule</pre>

```

# **Behavioral Modeling:**

Behavioral modeling is the highest level of abstraction in the Verilog HDL. The other modeling techniques are relatively detailed. They require some knowledge of how hardware or hardware signals work. The abstraction in this modeling is as simple as writing the logic in C language. This is a very powerful abstraction technique. All that a designer need is the algorithm of the design, which is the basic information for any design.

Most of the behavioral modeling is done using two important constructs: initial and always. All the other behavioral statements appear only inside these two structured procedure constructs.

#### **Procedural Constructs:**

#### **Initial Construct:**

The statements which come under the initial construct constitute the initial block. The initial block is executed only once in the simulation, at time 0. If there is more than one initial block, then all the initial blocks are executed concurrently. The initial construct is used as follows:

initial

begin

reset=1'b0;

clk=1'b1;

end

or

initial

clk = 1'b1;

In the first initial block there is more than one statement hence they are written between begin and end. If there is only one statement then there is no needs to put begin and end.

# **Always Construct:**

The statements which come under the always construct constitute the always block. The always block starts at time 0, and keeps on executing all the simulation time. It works like a infinite loop. It is generally used to model a functionality that is continuously repeated.

```

always

#5 clk=~clk;

initial

clk = 1'b0;

```

The above code generates a clock signal clk, with a time period of 10 units. The initial blocks initiates the clk value to 0 at time 0. Then after every 5 units of time it toggled, hence we get a time period of 10 units. This is the way in general used to generate a clock signal for use in test benches.

```

always@(posedgeclk, negedge reset) begin a = b + c; \\ d = 1'b1; \\ end

```

In the above example, the always block will be executed whenever there is a positive edge in the clk signal, or there is negative edge in the reset signal. This type of always is generally used in implement a FSM, which has a reset signal.

```

always @(b, c, d)

begin

a = (b + c)*d;

e = b | c;

end

```

In the above example, whenever there is a change in b, c, or d the always block will be executed. Here the list b, c, and d is called the sensitivity list.

In the Verilog 2000, we can replace always @(b,c,d) with always @(\*), it is equivalent to include all input signals, used in the always block. This is very useful when always blocks are used for implementing the combination logic.

# **Operations & Assignments**

The design description at the behavioral level is done through a sequence of assignments. These are called 'procedural assignments' – in contrast to the continuous assignments at the data flow level. Though it appears similar to the assignments at the data flow level discussed in the last chapter, the two are different. The procedure assignment is characterized by the following:

- The assignment is done through the "=" symbol (or the "<=" symbol) as was the case with the continuous assignment earlier.

- An operation is carried out and the result assigned through the "=" operator to an operand specified on the left side of the "=" sign for example,  $N = \sim N$ ;

- Here the content of reg N is complemented and assigned to the reg N itself. The assignment is essentially an updating activity.

- The operation on the right can involve operands and operators. The operands can be of different types logical variables, numbers real or integer and so on.

# **Procedural Assignments**

Procedural assignments are used for updating reg, integer, time, real, realtime, and memory data types. The variables will retain their values until updated by another procedural assignment. There is a significant difference between procedural assignments and continuous assignments. Continuous assignments drive nets and are evaluated and updated whenever an input operand changes value. Whereas procedural assignments update the value of variables under the control of the procedural flow constructs that surround them.

# The LHS of a procedural assignment could be:

- •reg, integer, real, realtime, or time data type.

- Bit-select of a reg, integer, or time data type, rest of the bits are untouched.