## SCHOOL OF BIO AND CHEMICAL ENGINNEERING DEPARTMENT OF BIOMEDICAL ENGINEERING

Unit - I

# **Fundamentals of Microprocessor and Microcontroller – SEC1323**

Evolution of Microprocessor – Architecture – Instruction format – Addressing modes – Basic timing diagram –Opcode fetch –Memory Read- Memory write- I/O Read-I/O Write-Interrupts in 8085-Software interrupts- Hardware interrupts- Priorities of Interrupts- 8085 based system design.

## **1.1Evolution of Microprocessor:**

It can be classified as following types **1.1.1First generation of processor: 4-bit Microprocessor**

The first microprocessor was introduced in 1971 by Intel Corp. It was named Intel 4004 as it was a 4 bit processor. It was a processor on a single chip. It could perform simple arithmetic and logic operations such as addition, subtraction, Boolean AND & Boolean OR. It had a control unit capable of performing control functions like fetching an instruction from memory, decoding it, and generating control pulses to execute it. It was able to operate on 4 bits of data at a time. This first microprocessor was quite a success in industry. Soon other microprocessors were also introduced. Intel introduced the enhanced version of 4004, the 4040. Some other 4 bit processors are International's PPS4 and Toshiba's T3472.

## 1.1.2Second generation of processor: 8-bit Microprocessor

The first 8 bit microprocessor which could perform arithmetic and logic operations on 8 bit words was introduced in 1973 again by Intel. This was Intel 8008 and was later followed by an improved version, Intel 8088. Some other 8 bit processors are Zilog-80 and Motorola M6800.

## **1.1.3 Third generation of processor: 16-bit Microprocessor**

The 8-bit processors were followed by 16 bit processors. They are Intel 8086 and 80286.

## 1.1.4Fourth generation of processor: 32-bit Microprocessor

The 32 bit microprocessors were introduced by several companies but the most popular one is Intel 80386.

#### 1.1.5Fifth generation of processor: Pentium Series

Instead of 80586, Intel came out with a new processor namely Pentium processor. Its performance is closer to RISC performance. Pentium was followed by Pentium Pro CPU. Pentium Pro allows allow multiple CPUs in a single system in order to achieve multiprocessing. The MMX extension was added to Pentium Pro and the result was Pentium II. The low cost version of Pentium II is Celeron. The Pentium III provided high performance floating point operations for certain types of computations by using the SIMD extensions to the instruction set. These new instructions make the Pentium III faster than high-end RISC CPUs.

Interestingly Pentium IV could not execute code faster than the Pentium III when running at the same clock frequency. So Pentium IV had to speed up by executing at a much higher clock frequency.

#### 1.2. Internal Architecture of 8085 Microprocessor:

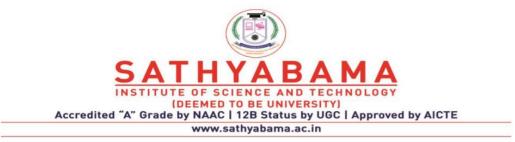

The functional block diagram or architecture of 8085 Microprocessor is very important as it gives the complete details about a Microprocessor. Fig1.1 shows the Block diagram of a Microprocessor.

Diagram

It consists of the following:

Control Unit

Generates signals within  $\mu P$  to carry out the instruction, which has been decoded. In reality causes certain connections between blocks of the  $\mu P$  to be opened or closed, so that data goes where it is required, and so that ALU operations occur.

Arithmetic Logic Unit

The ALU performs the actual numerical and logic operation such as 'add', 'subtract', 'AND', 'OR', etc. Uses data from memory and from Accumulator to perform arithmetic. Always stores result of operation in Accumulator.

Registers

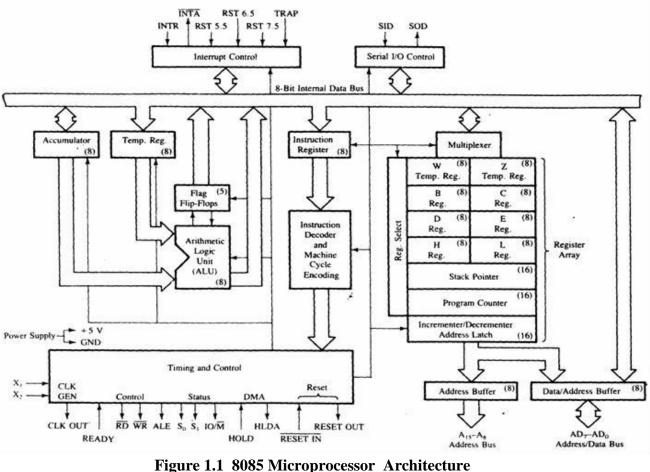

The 8085/8080A-programming model includes six registers, one accumulator, and one flag register. In addition, it has two 16-bit registers: the stack pointer and the program counter. They are described briefly in Figure 1.2.

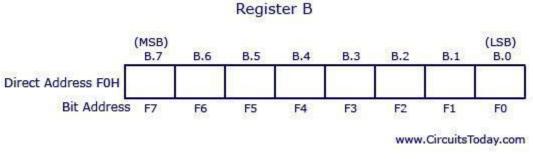

The 8085/8080A has six general- purpose registers to store 8-bit data; these are identified as B, C, D, E, H, and L as shown in the figure. They can be combined as register pairs - BC, DE, and HL - to perform some 16-bit operations. The programmer can use these registers to store or copy data into the registers by using data copy instructions.

Figure 1.2 8085 Microprocessor Registers set

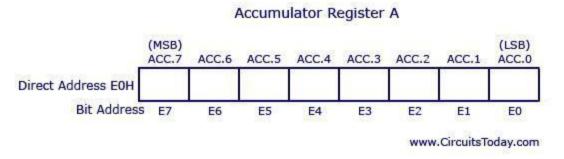

Accumulator (A):

It is an 8-bit register that is part of the arithmetic/logic unit (ALU). Used to store 8-bit data and to perform arithmetic and logical operations. The result of an operation is stored in the accumulator.

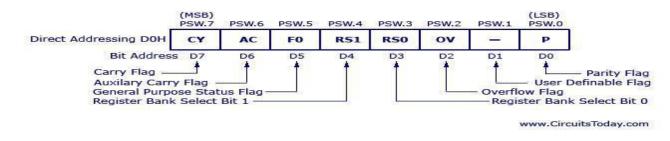

## Flags:

The ALU includes five flip-flops that are set or reset according to the result of an operation. The microprocessor uses the flags for testing the data conditions.

They are Zero (Z), Carry (CY), Sign (S), Parity (P), and Auxiliary Carry (AC) flags. The most commonly used flags are Sign, Zero, and Carry.

The bit position for the flags in flag register is,

| D7 | D <sub>6</sub> | D۶ | $D_4$ | $D_3$ | $D_2$ | D1 | D <sub>0</sub> |

|----|----------------|----|-------|-------|-------|----|----------------|

| S  | Z              |    | AC    |       | Р     |    | CY             |

Sign Flag (S):

- After execution of any arithmetic and logical operation, if D7 of the result is 1, the sign flag is set. Otherwise it is reset. D7 is reserved for indicating the sign; the remaining is the magnitude of number.

- If D7 is 1, the number will be viewed as negative number. If D7 is 0, the number will be viewed as positive number.

Zero Flag (z):

• If the result of arithmetic and logical operation is zero, then zero flag is set otherwise it is reset.

Auxiliary Carry Flag (AC):

• If D3 generates any carry when doing any arithmetic and logical operation, this flag is set. Otherwise it is reset.

Parity Flag (P):

• If the result of arithmetic and logical operation contains even number of 1's then this flag will be set and if it is odd number of 1's it will be reset.

Carry Flag (CY):

• If any arithmetic and logical operation result any carry then carry flag is set otherwise it is reset.

Program Counter (PC):

- This 16-bit register sequencing the execution of instructions. It is a memory pointer. Memory locations have 16-bit addresses, and that is why this is a 16-bit register.

- The function of the program counter is to point to the memory address of the next instruction to be executed.

- When an opcode is being fetched, the program counter is incremented by one to point to the next memory location.

Stack Pointer (SP):

The stack pointer is also a 16-bit register used as a memory pointer. It points to a memory location in R/W memory, called the stack.

The beginning of the stack is defined by loading a 16-bit address in the stack pointer.

Temporary Register:

• It is used to hold the data during the arithmetic and logical operations. Instruction Register:

• When an instruction is fetched from the memory, it is loaded in the instruction register.

Instruction Decoder:

• It gets the instruction from the instruction register and decodes the instruction. It identifies the instruction to be performed.

Serial I/O Control:

• It has two control signals named SID and SOD for serial data transmission.

Timing and Control unit:

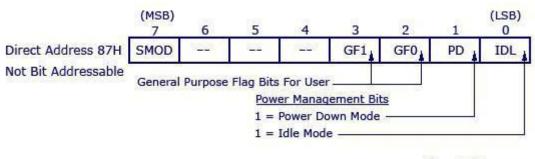

It has three control signals ALE, RD (Active low) and WR (Active low) and three status signals IO/M(Active low), S0 and S1. The control word shown in table .1

ALE is used for provide control signal to synchronize the components of microprocessor and timing for instruction to perform the operation.

RD (Active low) and WR (Active low) are used to indicate whether the operation is reading the data from memory or writing the data into memory respectively.IO/M(Active low) is used to indicate whether the operation is belongs to the memory or peripherals.

| IO/M(Active<br>Low) | <b>S1</b> | S2 | Data Bus Status(Output) |

|---------------------|-----------|----|-------------------------|

| 0                   | 0         | 0  | Halt                    |

| 0                   | 0         | 1  | Memory WRITE            |

| 0                   | 1         | 0  | Memory READ             |

| 1                   | 0         | 1  | IO WRITE                |

| 1                   | 1         | 0  | IO READ                 |

| 0                   | 1         | 1  | Opcode fetch            |

| 1                   | 1         | 1  | Interrupt ackno wiedge  |

Table 1: Read/Write data

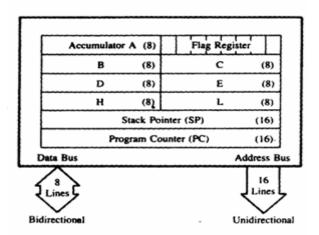

#### 1.2.1 8085 System Bus

Typical system uses a number of busses, collection of wires, which transmit binary numbers, one bit per wire. A typical microprocessor communicates with memory and other devices (input and output) using three busses: Address Bus, Data Bus and Control Bus.

## 1.2.1.1 Address Bus:

- $\Box$  The address bus is a group of 16 lines generally identified as A0 to A15.

- □ The address bus is unidirectional: bits flow in one direction-from the MPU to peripheral devices.

- □ The MPU uses the address bus to perform the first function: identifying a peripheral or a memory location.

Figure 1.3 Bus interfaced with Microprocessor

Data Bus:

The data bus is a group of eight lines used for data flow.

These lines are bi-directional - data flow in both directions between the MPU and memory and peripheral devices.

The MPU uses the data bus to perform the second function: transferring binary information. The eight data lines enable the MPU to manipulate 8-bit data ranging from 00 to FF (28 = 256 numbers).

The largest number that can appear on the data bus is 11111111.

## **1.2.2 Control Bus:**

The control bus carries synchronization signals and providing timing signals.

The MPU generates specific control signals for every operation it performs. These signals are used to identify a device type with which the MPU wants to communicate.

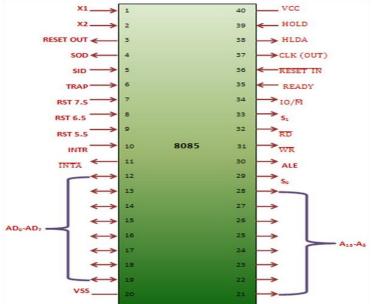

1.3 8085 Pin details. The diagram shown in Figure 1.4

Figure 1.4 Pin Diagram of 8085 Microprocessor

Properties

Single + 5V Supply

4 Vectored Interrupts (One is Non Maskable) Serial In/Serial Out

Port

Decimal, Binary, and Double Precision Arithmetic Direct

Addressing Capability to 64K bytes of memory

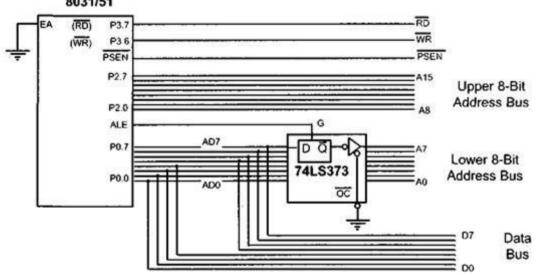

The Intel 8085A is a new generation, complete 8 bit parallel central processing unit (CPU). The 8085A uses a multiplexed data bus. The address is split between the 8bit address bus and the 8bit data bus.

Pin Description

The following describes the function of each pin:

A6 - A1s (Output 3 State)- Address Bus: The most significant 8 bits of the memory address or the 8 bits of the I/0 address,3 stated during Hold and Halt modes.

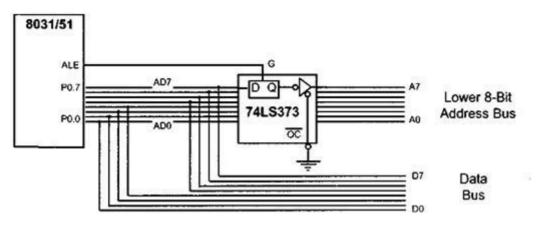

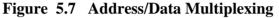

AD0 - AD7 (*Input/Output 3state*) Multiplexed Address/Data Bus; Lower 8 bits of the memory address (or I/0 address) appear on the bus during the first clock cycle of a machine state. It then becomes the data bus during the second and third clock cycles. 3 stated during Hold and Halt modes.

*ALE (Output)- Address Latch Enable:* It occurs during the first clock cycle of a machine state and enables the address to get latched into the on chip latch of peripherals. The falling edge of ALE is set to guarantee setup and hold times for the address information. ALE can also be used to strobe the status information. ALE is never 3stated.

SO, S1 (Output)-Data Bus Status. Encoded status of the bus cycle shown in table .2

| Table | .2 control | l word |

|-------|------------|--------|

|-------|------------|--------|

| <b>S</b> 1 | <b>S</b> 0 |       |

|------------|------------|-------|

| 0          | 0          | HALT  |

| 0          | 1          | WRITE |

| 1          | 0          | READ  |

| 1          | 1          | FETCH |

S1 can be used as an advanced R/W status.

*RD* (*Output 3state*)- *READ*; indicates the selected memory or 1/0 device is to be read and that the Data Bus is available for the data transfer.

*WR* (*Output 3state*)- *WRITE;* indicates the data on the Data Bus is to be written into the selected memory or 1/0 location. Data is set up at the trailing edge of WR. 3stated during Hold and Halt modes.

*READY (Input)*- If Ready is high during a read or write cycle, it indicates that the memory or peripheral is ready to send or receive data. If Ready is low, the CPU will wait for Ready to go high before completing the read or write cycle.

*HOLD (Input)- HOLD*; indicates that another Master is requesting the use of the Address and Data Buses. The CPU, upon receiving the Hold request. will relinquish the use of buses as soon as the completion of the current machine cycle. Internal processing can continue. The processor can regain the buses only after the Hold is removed. When the Hold is acknowledged, the Address, Data, RD, WR, and IO/M lines are 3stated.

*HLDA (Output)- HOLD ACKNOWLEDGE*; indicates that the CPU has received the Hold request and that it will relinquish the buses in the next clock cycle. HLDA goes low after the Hold request is removed. The CPU takes the buses one half clock cycle after HLDA goes low.

*INTR (Input)-* INTERRUPT REQUEST; is used as a general purpose interrupt. It is sampled only during the next to the last clock cycle of the instruction. If it is active, the Program Counter (PC) will be inhibited from incrementing and an INTA will be issued. During this cycle a RESTART or CALL instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and disabled by software. It is disabled by Reset and immediately after an interrupt is accepted.

*INTA (Output)-* INTERRUPT ACKNOWLEDGE; is used instead of (and has the same timing as) RD during the Instruction cycle after an INTR is accepted. It can be used to activate the 8259 Interrupt chip or some other interrupt port.

RST 5.5

RST 6.5 - (Inputs) RST

7.5

*RESTART INTERRUPTS*; These three inputs have the same timing as I NTR except they cause an internal RESTART to be automatically inserted.

RST 7.5 Highest Priority RST 6.5

RST 5.5 Lowest Priority

The priority of these interrupts is ordered as shown above. These interrupts have a higher priority than the INTR.

*TRAP (Input)-Trap* interrupt is a nonmaskable restart interrupt. It is recognized at the same time as INTR. It is unaffected by any mask or Interrupt Enable. It has the highest priority of any interrupt.

*RESET IN (Input)*- Reset sets the Program Counter to zero and resets the Interrupt Enable and HLDA flipflops. None of the other flags or registers (except the instruction register) are affected The CPU is held in the reset condition as long as Reset is applied. *RESET OUT (Output)*-

Indicates CPIJ is being reset. Can be used as a system RESET. The signal is synchronized to the processor clock.

X1, X2 (*Input*)-Crystal or R/C network connections to set the internal clock generator X1 can also be an external clock input instead of a crystal. The input frequency is divided by 2 to give the internal operating frequency.

*CLK (Output)*-Clock Output for use as a system clock when a crystal or R/C network is used as an input to the CPU. The period of CLK is twice the X1, X2 input period.

*IO/M (Output)*-IO/M indicates whether the Read/Write is to memory or I/O Tristated during Hold and Halt modes.

*SID (Input)*- Serial input data line The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.

SOD (output)- Serial output data line. The output SOD is set or reset as specified by the SIM instruction.

*Vcc* +5 volt supply.

Vss Ground Reference.

## **1.4 8085 Functional Description**

The 8085A is a complete 8 bit parallel central processor. It requires a single +5 volt supply. Its basic clock speed is 3 MHz thus improving on the present 8080's performance with higher system speed. Also it is designed to fit into a minimum system of three IC's: The CPU, a RAM/ IO, and a ROM or PROM/IO chip.

The 8085A uses a multiplexed Data Bus. The address is split between the higher 8bit Address Bus and the lower 8bit Address/Data Bus. During the first cycle the address is sent out. The lower 8bits are latched into the peripherals by the Address Latch Enable (ALE). During the rest of the machine cycle the Data Bus is used for memory or I/O data. The 8085A provides RD, WR, and IO/Memory signals for bus control. An Interrupt Acknowledge signal (INTA) is also provided. Hold, Ready, and all Interrupts are synchronized. The 8085A also provides serial input data (SID) and serial output data (SOD) lines for simple serial interface.

In addition to these features, the 8085A has three maskable, restart interrupts and one non-maskable trap interrupt. The 8085A provides RD, WR and IO/M signals for Bus control.

Status information is directly available from the 8085A. ALE serves as a status strobe. The status is partially encoded, and provides the user with advanced timing of the type of bus transfer being done. IO/M cycle status signal is provided directly also. Decoded So, S1 Carries the following status information:

#### HALT, WRITE, READ, FETCH

S1 can be interpreted as R/W in all bus transfers. In the 8085A the 8 LSB of address are multiplexed with the data instead of status. The ALE line is used as a strobe to enter the lower half of the address into the memory or peripheral address latch. This also frees extra pins for expanded interrupt capability.

## **1.5 Interrupt and Serial I/O**

The8085A has5 interrupt inputs: INTR, RST5.5, RST6.5, RST 7.5, and TRAP. INTR is identical in function to the 8080 INT. Each of the three RESTART inputs, 5.5, 6.5. 7.5, has a programmable mask. TRAP is also a RESTART interrupt except it is non-maskable.

The three RESTART interrupts cause the internal execution of RST (saving the program counter in the stack and branching to the RESTART address) if the interrupts are enabled and if the interrupt mask is not set. The non-maskable TRAP causes the internal execution of a RST independent of the state of the interrupt enable or masks.

The interrupts are arranged in a fixed priority that determines which interrupt is to be recognized if more than one is pending as follows: TRAP highest priority, RST 7.5, RST 6.5, RST 5.5, INTR lowest priority This priority scheme does not take into account the priority of a routine that was started by a higher priority interrupt. RST 5.5 can interrupt a RST 7.5 routine if the interrupts were re-enabled before the end of the RST 7.5 routine. The TRAP interrupt is useful for catastrophic errors such as power failure or bus error. The TRAP input is recognized just as any other interrupt but has the highest priority. It is not affected by any flag or mask. The TRAP input is both edge and level sensitive.

## **1.6 .Instruction Format**

An instruction is a command to the microprocessor to perform a given task on a specified data. Each instruction has two parts: one is task to be performed, called the operation code (opcode), and the second is the data to be operated on, called the operand. The operand (or data) can be specified in various ways. It may include 8-bit (or 16-bit ) data, an internal register, a memory location, or 8-bit (or 16-bit) address. In some instructions, the operand is implicit.

## **1.7 Instruction format**

The 8085 instruction set is classified into the following three groups according to word size:

- 1. One-word or 1-byte instructions

- 2. Two-word or 2-byte instructions

- **3**. Three-word or 3-byte instructions

In the 8085, "byte" and "word" are synonymous because it is an 8-bit microprocessor. However, instructions are commonly referred to in terms of bytes rather than words. One-Byte Instructions

A 1-byte instruction includes the opcode and operand in the same byte. Operand(s) are internal register and are coded into the instruction.

For example:

| Task                                                               | Op   | Operand | Binary    | Hex  |

|--------------------------------------------------------------------|------|---------|-----------|------|

|                                                                    | code |         | Code      | Code |

| Copy the contents of the accumulator in the register C.            | MOV  | C,A     | 0100 1111 | 4FH  |

| Add the contents of register B to the contents of the accumulator. | ADD  | В       | 1000 0000 | 80H  |

| Invert (compliment) each bit in the accumulator.                   | СМА  |         | 0010 1111 | 2FH  |

These instructions are 1-byte instructions performing three different tasks. In the first instruction, both operand registers are specified. In the second instruction, the operand B is specified and the accumulator is assumed. Similarly, in the third instruction, the accumulator is assumed to be the implicit operand. These instructions are stored in 8-bit binary format in memory; each requires one memory location.

MOV rd, rs

rd <-- rs copies contents of rs into rd.

Coded as 01 ddd sss where ddd is a code for one of the 7 general registers which is the destination of the data, sss is the code of the source register.

Example: MOV A,B

Coded as 01111000 = 78H = 170 octal (octal was used extensively in instruction design of such processors).

ADD r

A <-- A + r

Two-Byte Instructions

In a two-byte instruction, the first byte specifies the operation code and the second byte specifies the operand. Source operand is a data byte immediately following the opcode. For example:

| Task                                              | Opcode | Operand | Binary<br>Code | Hex Code |                           |

|---------------------------------------------------|--------|---------|----------------|----------|---------------------------|

| Load an 8-bit data<br>byte in the<br>accumulator. | MVI    | A, Data | 0011 1110      |          | First Byte<br>Second Byte |

Assume that the data byte is 32H. The assembly language instruction is written as

| Mnemonics  | Hex code |

|------------|----------|

| MVI A, 32H | 3E 32H   |

The instruction would require two memory locations to store in memory. MVI r,data r <--

data

Example: MVI A,30H coded as 3EH 30H as two contiguous bytes. This is an example of immediate addressing.

ADI data

A <-- A + data

OUT port where port is an 8-bit device address. (Port) <-- A. Since the byte is not the data but points directly to where it is located this is called direct addressing.

Three-Byte Instructions: In a three-byte instruction, the first byte specifies the opcode, and the following two bytes pecify the 16-bit address.

and the third byte is the high-order address opcode + data byte + data byte For example:

| Task            | Opcode | Operand | Binary code  | Hex Code |             |

|-----------------|--------|---------|--------------|----------|-------------|

| Transfer the    | JMP    | 2085H   |              | C3       | First byte  |

| program         |        |         | 1100<br>0011 |          |             |

| sequenc<br>e to |        |         | 1000<br>0101 | 85       | Second Byte |

| the memory      |        |         | 0010         |          |             |

| location        |        |         | 0000         | 20       | Third Byte  |

| 2085H.          |        |         |              |          |             |

This instruction would require three memory locations to store in memory. Three

byte instructions - opcode + data byte + data byte

LXI rp, data16

rp is one of the pairs of registers BC, DE, HL used as 16-bit registers. The two data bytes are 16-bit data in L H order of significance.

rp <-- data16

Example:

LXI H,0520H coded as 21H 20H 50H in three bytes. This is also immediate addressing.

LDA addr

A <-- (addr) Addr is a 16-bit address in L H order. Example: LDA 2134H coded as 3AH 34H 21H. This is also an example of direct addressing.

Instruction Set Classification

An instruction is a binary pattern designed inside a microprocessor to perform a specific function. The entire group of instructions, called the instruction set, determines what functions the microprocessor can perform. These instructions can be classified into the following five functional categories: data transfer (copy) operations, arithmetic operations, logical operations, branching operations, and machine-control operations.

Data Transfer (Copy) Operations

This group of instructions copy data from a location called a source to another location called a destination, without modifying the contents of the source. In technical manuals, the term *data transfer* is used for this copying function. However, the term *transfer* is misleading; it creates the impression that the contents of the source are destroyed when, in fact, the contents are retained without any modification. The various types of data transfer (copy) are listed below together with examples of each type:

| Types | Examples                                                |

|-------|---------------------------------------------------------|

| •     | 1. Copy the contents of the register B into register D. |

| 2. Specific data byte to a register or a memory location. | 2. Load register B with the data byte 32H.     |

|-----------------------------------------------------------|------------------------------------------------|

| 3. Between a memory location and a register.              | 3. From a memory location 2000H to register B. |

| 4. Between an I/O device and the accumulator.             | 4.From an input keyboard to the accumulator.   |

## 1.8.8085 Addressing Modes

The instructions MOV B, A or MVI A, 82H are to copy data from a source into a destination. In these instructions the source can be a register, an input port, or an 8-bit number (00H to FFH). Similarly, a destination can be a register or an output port. The sources and destination are operands. The various formats for specifying operands are called the ADDRESSING MODES. For 8085, they are:

- 1. Immediate addressing.

- 2. Register addressing.

- 3. Direct addressing.

- 4. Indirect addressing.

## **1.8.1. Immediate addressing**

Data is present in the instruction. Load the immediate data to the destination provided. Example: MVI R,data

#### 1.8.2 Register addressing

Data is provided through the registers.

## Example: MOV Rd, Rs

## 1.8.3 Direct addressing

Used to accept data from outside devices to store in the accumulator or send the data stored in the accumulator to the outside device. Accept the data from the port 00H and store them into the accumulator or Send the data from the accumulator to the port 01H. Example: IN 00H or OUT 01H

#### **1.8.4 Indirect Addressing**

This means that the Effective Address is calculated by the processor. And the contents of the address (and the one following) is used to form a second address. The second address is where the data is stored. Note that this requires several memory accesses; two accesses to retrieve the 16 -bit address and a further access (or accesses) to retrieve the data which is to be loaded into the register.

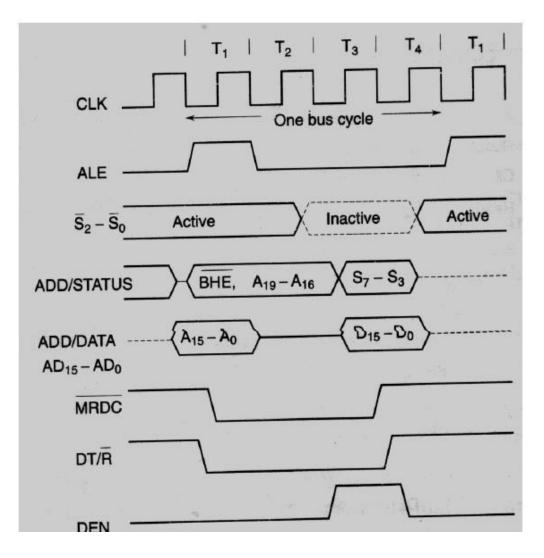

#### **1.9.Timing Diagrams of 8085**

It is one of the best ways to understand to process of micro-processor/controller. With the help of timing diagram we can understand the working of any system, step by step working of each instruction and its execution, etc. It is the graphical representation of process in steps with respect to time. The timing diagram represents the clock cycle and duration, delay, content of address bus and data bus, type of operation ie. Read/write/status signals.

Rules to identify number of machine cycles in an instruction:

- 1. If an addressing mode is direct, immediate or implicit then No. of machine cycles = No. of bytes.

- 2. If the addressing mode is indirect then No. of machine cycles = No. of bytes + 1. Add + 1 to the No. of machine cycles if it is memory read/write operation.

- 3. If the operand is 8-bit or 16-bit address then, No. of machine cycles = No. of bytes +1.

- 4. These rules are applicable to 80% of the instructions of 8085.]

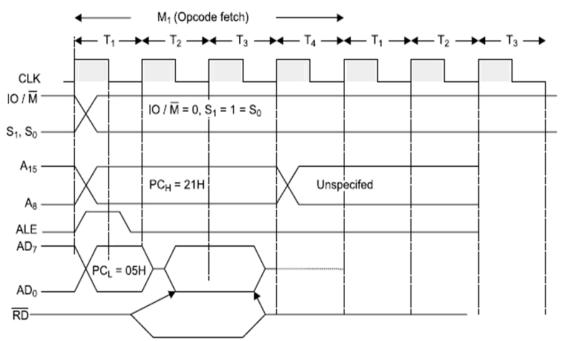

#### 1.9.1 Opcode fetch:

The microprocessor requires instructions to perform any particular action. In order to perform these actions microprocessor utilizes opcode which is a part of an instruction which provides detail to microprocessor.shown in Figure 1.5

Opcode fetch timing Operation:

- During T1 state, microprocessor uses IO/M(bar), S0, S1 signals are used to instruct microprocessor to fetch opcode.

- > Thus when IO/M(bar)=0, S0=S1=1, it indicates opcode fetch operation.

- During this operation 8085 transmits 16-bit address and also uses ALE signal for address latching.

- At T2 state microprocessor uses read signal and make data ready from that memory location to read opcode from memory and at the same time program counter increments by 1 and points next instruction to be fetched.

- In this state microprocessor also checks READY input signal, if this pin is at low logic level ie. '0' then microprocessor adds wait state immediately between T2 and T3.

- At T3, microprocessor reads opcode and store it into instruction register to decode it further.

- During T4 microprocessor performs internal operation like decoding opcode and providing necessary actions.

- The opcode is decoded to know whether T5 or T6 states are required, if they are not required then the processor performs next operation.

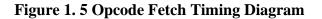

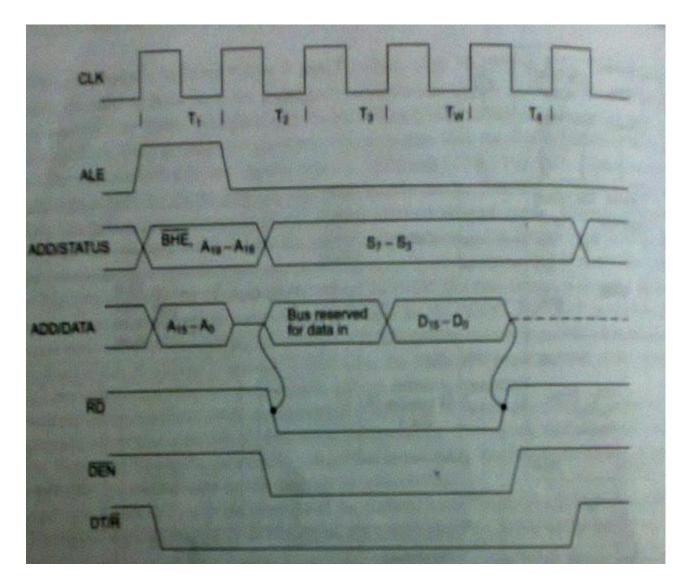

#### 1.9.2 Memory Read Timing Diagram

Figure.1.6 Memory read timing diagram

## Operation:

- ➤ It is used to fetch one byte from the memory.

- ➢ It requires 3 T-States.

- > It can be used to fetch operand or data from the memory.

- During T1, A8-A15 contains higher byte of address. At the same time ALE is high. Therefore Lower byte of address A0-A7 is selected from AD0-AD7.

- Since it is memory ready operation, IO/M(bar) goes low.

- During T2 ALE goes low, RD(bar) goes low. Address is removed from AD0-AD7 and data D0-D7 appears on AD0-AD7.

- > During T3, Data remains on AD0-AD7 till RD(bar) is at low signal.

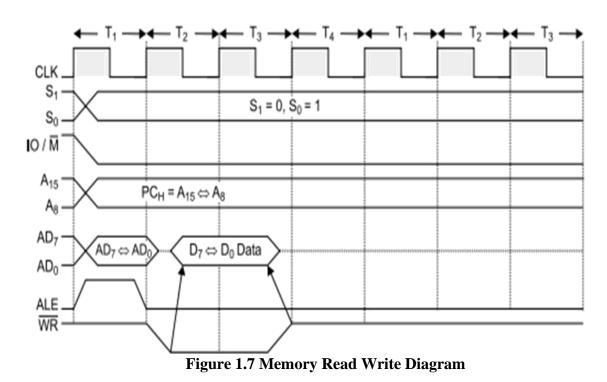

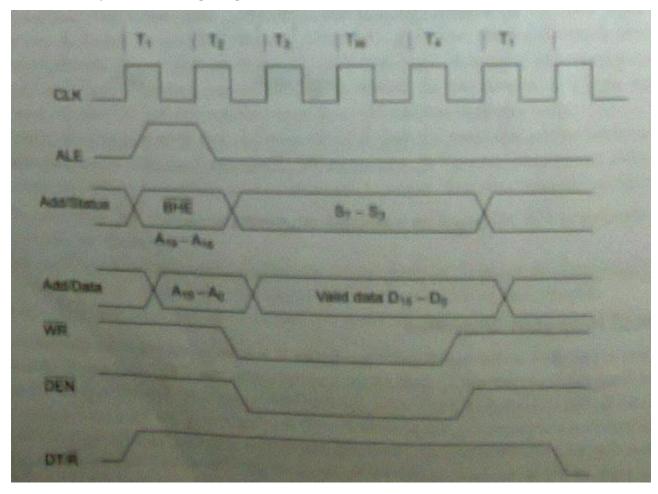

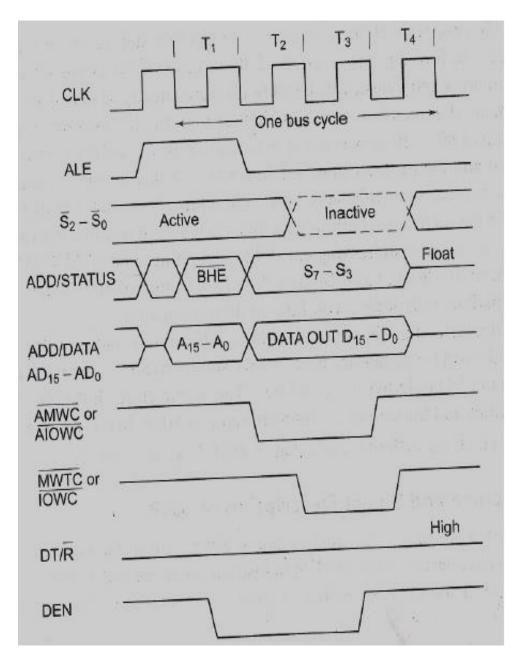

## 1.9.3 Memory write timing diagram

Operation:

- ➢ It is used to send one byte into memory.

- ▶ It requires 3 T-States.

- > During T1, ALE is high and contains lower address A0-A7 from AD0-AD7.

- A8-A15 contains higher byte of address. As it is memory operation, IO/M goes low.

- During T2, ALE goes low, WR goes low and Address is removed from AD0-AD7 and then data appears on AD0-AD7.

- > Data remains on AD0-AD7 till WR is low.

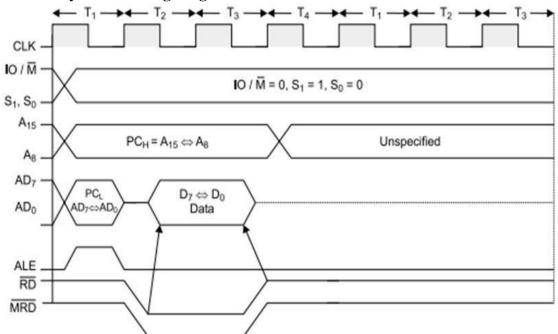

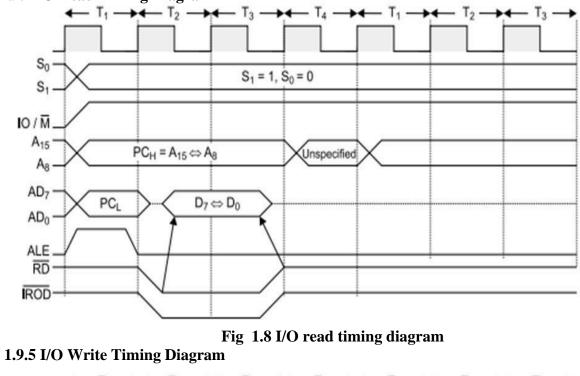

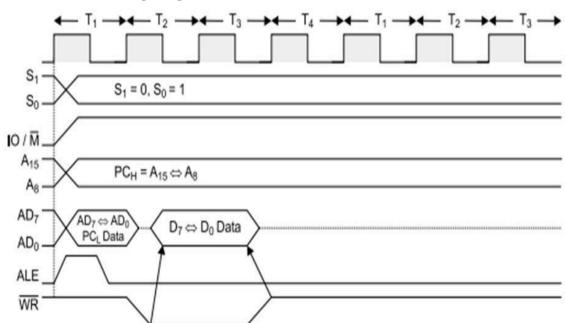

#### **1.9.4 IO Read Timing Diagram**

Figure 1.9 I/O write timing diagram

- It is used to writ one byte into IO device.

- ➢ It requires 3 T-States.

- During T1, the lower byte of address is duplicated into higher order address bus A8-A15.

- ALE is high and A0-A7 address is selected from AD0-AD7. o As it is an IO operation <u>IO/M</u> goes low.

- During T2, ALE goes low, WR goes low and data appears on AD0-AD7 to write data into IO device.

- During T3, Data remains on AD0-AD7 till W<u>R is</u> low.

## 1.10 Instruction Set of 8085

An Instruction is a command given to the computer to perform a specified operation on given data. The instruction set of a microprocessor is the collection of the instructions that the microprocessor is designed to execute. The instructions described here are of Intel 8085. These instructions are of Intel Corporation. They cannot be used by other microprocessor manufactures. The programmer can write a program in assembly language using these instructions. These instructions have been classified into the following groups:

- 1. Data Transfer Group

- 2. Arithmetic Group

- 3. Logical Group

- 4. Branch Control Group

- 5. I/O and Machine Control Group

**1.10.1 Data Transfer Instruction:** Instructions, which are used to transfer data from one register to another register, from memory to register or register to memory, come under this group. Examples are: MOV, MVI, LXI, LDA, STA etc. When an instruction of data transfer group is executed, data is transferred from the source to the destination without altering the contents of the source. For example, when MOV A, B is executed the content of the register B is copied into the register A, and the content of register B remains unaltered. Similarly, when LDA 2500 is executed the content of the memory location 2500 remains unaltered.

## i. MOV Rd, Rs

- Move Data; Move the content of the from source register to destination register.

- ii. MOV Rd, M -Move the content of memory register to destination register.

- iii. MOV M, Rs. -Move the content of register to memory.

- iv. MVI r, data. -Move immediate data to register.

- v. MVI M, data- Move immediate data to memory.

- vi. LXI rp, data 16- Load register pair immediate.

- vii. LDA addr- Load Accumulator direct.

- viii. STA addr- Store accumulator direct.

- ix. .LHLD addr- Load H-L pair direct

- x. SHLD addr- Store H-L pair direct

- xi. LDAX rp. -LOAD accumulator indirect

- xii. STAX rp- Store accumulator indirect

- xiii. XCHG- Exchange the contents of H-L with D-E pair [H-L] <--> [D-E].

**1.10.2 Arithmetic Instructions:** The instructions of this group perform arithmetic operations such as addition, subtraction; increment or decrement of the content of a register or memory. Examples are: ADD, SUB, INR, DAD etc.

Logical Group: The Instructions under this group perform logical operation such as AND, OR, compare, rotate etc. Examples are: ANA, XRA, ORA, CMP, and RAL etc.

Branch Control Group: This group includes the instructions for conditional and unconditional jump, subroutine call and return, and restart. Examples are: JMP, JC, JZ, CALL, CZ, RST etc.

I/O and Machine Control Group: This group includes the instructions for input/output ports, stack and machine control. Examples are: IN, OUT, PUSH, POP, and HLT etc. Intel 8085 Instructions

- i. ADD r. (Add register to accumulator) [A]  $\square$  [A] + [r].

- ii. ADD M. (Add memory to accumulator)  $[A]^{\Box} [A] + [[H-L]].$

- iii. ADC r. (Add register with carry to accumulator).  $[A] \square [A] + [r] + [CS]$ .

- iv. ADC M. (Add memory with carry to accumulator)  $[A]^{\Box} [A] + [[H-L]] [CS].$

- V. ADI data (Add immediate data to accumulator)  $[A] \square [A] + data$ .

- vi. ACI data (Add with carry immediate data to accumulator). [A]  $\square$  [A] + data + [CS].

- vii. DAD rp. (Add register paid to H-L pair).  $[H-L] \square [H-L] + [rp]$ .

- viii. SUB r. (Subtract register from accumulator).  $[A] \ [A] [r]$ .

- ix. SUB M. (Subtract memory from accumulator). [A]  $\Box$  [A] [[H-L]].

- X. SBB r. (Subtract register from accumulator with borrow). [A]  $\square$  [A] [r] -[CS].

- xi. SBB M. (Subtract memory from accumulator with borrow). [A]  $\square$  [A] [[H-L]] [CS].

- xii. SUI data. (Subtract immediate data from accumulator)  $[A]^{\Box}[A]$  data.

- xiii. SBI data. (Subtract immediate data from accumulator with borrow). [A]  $\square$  [A] - data - [CS].

- xiv. INR r (Increment register content)  $[r]^{\Box} [r] + 1$ .

- xv. INR M. (Increment memory content)  $[[H-L]]^{\Box} [[H-L]] + 1$ .

- xvi. DCR r. (Decrement register content).  $[r]^{\Box} [r] 1$ .

- xvii. DCR M. (Decrement memory content)  $[[H-L]]^{\Box} [[H-L]] 1$ .

- xviii. INX rp. (Increment register pair)  $[rp]^{\Box} [rp] 1$ .

- xix. DCX rp (Decrement register pair)  $[rp]^{\Box}$  [rp] -1.

- xx. DAA (Decimal adjust accumulator).

The instruction DAA is used in the program after ADD, ADI, ACI, ADC, etc instructions. After the execution of ADD, ADC, etc instructions the result is in hexadecimal and it is placed in the accumulator. The DAA instruction operates on this result and gives the final result in the decimal system. It uses carry and auxiliary carry for decimal adjustment. 6 is added to 4 LSBs of the content of the accumulator if their value lies in between A and F or the AC flag is set to 1. Similarly, 6 is also added to 4 MSBs of the content of the accumulator if their value lies in between A and F or the CS flag is set to 1. All status flags are affected. When DAA is used data should be in decimal numbers.

## **1.10.3 Logical Instructions**

- i. ANA r. (AND register with accumulator) [A]  $\square$  [A]  $\wedge$  [r].

- ii. ANA M. (AND memory with accumulator).  $[A] \square [A] \land [[H-L]]$ .

- iii. ANI data. (AND immediate data with accumulator)  $[A]^{\Box}[A]^{A}$  data.

- iv. ORA r. (OR register with accumulator) [A]  $\square$  [A] v [r].

- V. ORA M. (OR memory with accumulator)  $[A]^{\Box}$  [A] v [[H-L]]

- vi. ORI data. (OR immediate data with accumulator)  $[A]^{\Box}[A] v data$ .

- vii. XRA r. (EXCLUSIVE OR register with accumulator) [A]  $\Box$  [A] v [r]

- viii. XRA M. (EXCLUSIVE-OR memory with accumulator)  $[A] \square [A] v [[H-L]]$

- ix. XRI data. (EXCLUSIVE-OR immediate data with accumulator) [A] [A] v data.

- X. CMA. (Complement the accumulator)  $[A]^{\Box}[A]$

- **x.** CMC. (Complement the carry status)  $[CS]^{\Box}$  [CS]

- xi. STC. (Set carry status) [CS]  $\Box$  1.

- xii. CMP r. (Compare register with accumulator) [A] [r]

- xiii. CMP M. (Compare memory with accumulator) [A] [[H-L]]

- xiv. CPI data. (Compare immediate data with accumulator) [A] data.

- XV. RLC (Rotate accumulator left)  $[An+1] \ [An], [A0] \ [A7], [CS] \ [A7].$

The content of the accumulator is rotated left by one bit. The seventh bit of the accumulator is moved to carry bit as well as to the zero bit of the accumulator. Only CS flag is affected.

- xvi. RRC. (Rotate accumulator right)  $[A7] \ [A0], [CS] \ [A0], [An] \ [An+1]$ . The content of the accumulator is rotated right by one bit. The zero bit of the accumulator is moved to the seventh bit as well as to carry bit. Only CS flag is affected.

- xvii. RAL. (Rotate accumulator left through carry)  $[An+1] \ [An], [CS] \ [A7], [A0] \ [CS].$

- xviii. RAR. (Rotate accumulator right through carry) [An]  $\Box$  [An+1], [CS]  $\Box$  [A0], [A7]  $\Box$  [CS]

## **1.10.4 Branching Instruction:**

- i. JMP addr (label). (Unconditional jump: jump to the instruction specified by the address). [PC] <sup>[]</sup> Label.

- ii. Conditional Jump addr (label): After the execution of the conditional jump instruction the program jumps to the instruction specified by the address (label) if the specified condition is fulfilled. The program proceeds further in the normal sequence if the specified condition is not fulfilled. If the condition is true and program jumps to the specified label, the execution of a conditional jump takes 3 machine cycles: 10 states. If condition is not true, only 2 machine cycles; 7 states are required for the execution of the instruction.

a. JZ addr (label). (Jump if the result is zero)

- b. JNZ addr (label) (Jump if the result is not zero)

- c. JC addr (label). (Jump if there is a carry)

- d. JNC addr (label). (Jump if there is no carry)

- e. JP addr (label). (Jump if the result is plus)

- f. JM addr (label). (Jump if the result is minus)

- g. JPE addr (label) (Jump if even parity)

- h. JPO addr (label) (Jump if odd parity)

- iii. CALL addr (label) (Unconditional CALL: call the subroutine identified by the operand)

CALL instruction is used to call a subroutine. Before the control is transferred to the subroutine, the address of the next instruction of the main program is saved in the stack. The content of the stack pointer is decremented by two to indicate the new stack top. Then the program jumps to subroutine starting at address specified by the label.

- iv. RET (Return from subroutine)

- v. RST n (Restart) Restart is a one-word CALL instruction. The content of the program counter is saved in the stack. The program jumps to the instruction starting at restart location.

### 1.10.5 Stack, I/O and Machine Control Instruction :

- i. IN port-address. (Input to accumulator from I/O port) [A] [Port]

- ii. OUT port-address (Output from accumulator to I/O port) [Port]  $\Box$  [A]

- iii. PUSH rp (Push the content of register pair to stack)

- iv. PUSH PSW (PUSH Processor Status Word)

- v. POP rp (Pop the content of register pair, which was saved, from the stack)

- vi. POP PSW (Pop Processor Status Word)

- vii. HLT (Halt)

- viii. XTHL (Exchange stack-top with H-L)

- ix. SPHL (Move the contents of H-L pair to stack pointer)

- x. EI (Enable Interrupts)

- xi. DI (Disable Interrupts)

- xii. SIM (Set Interrupt Masks)

- xiii. RIM (Read Interrupt Masks)

- xiv.NOP (No Operation)

## 1.11. Interrupts in 8085 Microprocessor

## **1.11.1 Software interrupts:**

The software interrupts are program instructions. These instructions are inserted at desired locations in a program. The 8085 has eight software interrupts from RST 0 to RST 7.

RST 0- 0000<sub>H</sub> RST 1-0008<sub>H</sub> RST 2- 0010<sub>H</sub> RST 3-0018<sub>H</sub> RST 4-0020<sub>H</sub> RST5 -0028<sub>H</sub> RST6- 0030<sub>H</sub> RST 7- 0038<sub>H</sub>

## **1.11.2 Hardware interrupts:**

An external device initiates the hardware interrupts and placing an appropriate signal at the interrupt pin of the processor. If the interrupt is accepted then the processor executes an interrupt service routine.

The 8085 has five hardware interrupts

TRAP RST 7.5 RST 6.5 RST 5.5 INTR

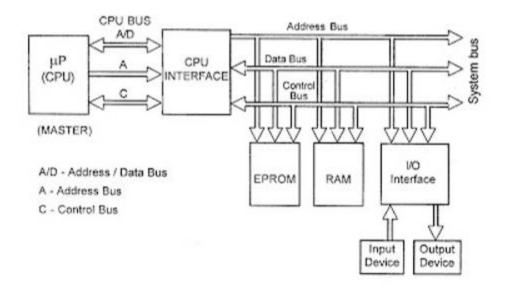

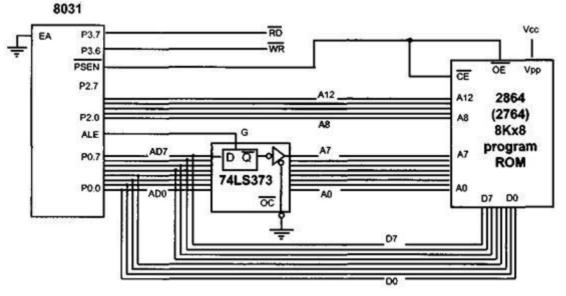

## 1.12 8085 Microprocessor Based system design

- The microprocessor is a semiconductor device (Integrated Circuit) manufactured by the VLSI (Very Large Scale Integration) technique. It includes the ALU, register arrays and control circuit on a single chip.

- A system designed using a microprocessor as its CPU is called a microcomputer. The Microprocessor based system (single board microcomputer) consists of microprocessor as CPU, semiconductor memories like EPROM and RAM, input device, output device and interfacing devices.

- The memories, input device, output device and interfacing devices are called peripherals. The popular input devices are keyboard and floppy disk and the output devices are printer, LED/LCD displays, CRT monitor,

## Figure 1.10 Microprocessor interfacing with External Memory

- In the  $\mu$ P based system, the microprocessor is the master and all other peripherals are slaves. The master controls all the peripherals and initiates all operations. The work done by the processor can be classified into the following three groups.

- Work done internal to the processor

- Work done external to the processor

- Operations initiated by the slaves or peripherals.

- The work done internal to the processors are addition, subtraction, logical operations, data transfer operations, etc.

- The work done external to the processor are reading/writing the memory and reading/writing the I/O devices or the peripherals. If the peripheral requires the attention of the master then it can interrupt the master and initiate an operation.

- The microprocessor is the master, which controls all the activities of the system. To perform a specific job or task, the microprocessor has to execute a program stored in memory. The program consists of a set of instructions. It issues address and control signals and fetches the instruction and data from memory.

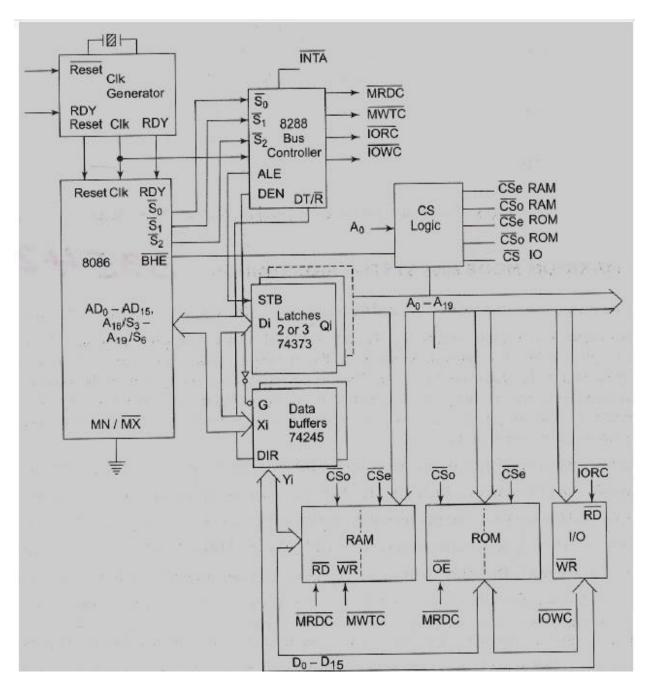

## **BUSES:**

The buses are group of lines that carries data, address or control signals.

- The CPU Bus has multiplexed lines, i.e., same line is used to carry different signals

- The CPU interface is provided to demultiplex, the multiplexed lines, to generate chip select signals and additional control signals.

- The system bus has separate lines for each signal. All the slaves in the system are connected to the same system bus. At any time instant communication takes place between the master and one of the slaves.

## **Peripheral Devices :**

- The EPROM memory is used to store permanent programs and data.

- The RAM memory is used to store temporary programs and data.

- The input device is used to enter the program, data and to operate the system.

- The output device is used for examining the results. Since the speed of I/O devices does not match with the speed of microprocessor, an interface device is provided between system bus and I/O devices. Generally I/O devices are slow devices.

## **Reference Books:**

1.Ramesh S Gaonkar, Microprocessor Architecture, Programming and application with 8085, 4» Edition, Penram International Publishing, New Delhi, 2000

2. Kennith J. Ayala, 8051 Microcontroller, Thomson, 2005.

3. Dougles V. Hall, Microprocessor and Interfacing, Tata MC Graw Hill Publication, 2. (Edition, 1992.

4. Charless M. Gilmore, "Microprocessor Principle and application, McGraw Hill publication, 1995.

5. A.NagoorKani, Microprocessor & Microcontroller, Tata Mc Graw Hill, 3«Edition, 2012

6. B. Ram, Fundamentals of Microprocessors and Microcomputers, Dhanpat Rai Publications, 2001.

## SCHOOL OF BIO AND CHEMICAL ENGINNEERING DEPARTMENT OF BIOMEDICAL ENGINEERING

Unit -II

**Fundamentals of Microprocessor and Microcontroller – SEC1323**

8255 Programmable Peripherals Interface Architecture & various modes of operation – 8251 USART Architecture and programming features – 8237 DMA Controller Architecture & Programming features.

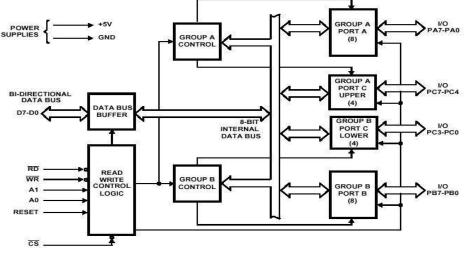

#### **2.1.Programmable peripheral Interface 8255(PPI)**

The parallel input-output port chip 8255 is also called as programmable peripheral input-output port. The Intel"s 8255 is designed for use with Intel"s 8-bit, 16-bit and higher capability microprocessors. It has 24 input/output lines which may be individually programmed in two groups of twelve lines each, or three groups of eight lines. The two groups of I/O pins are named as Group A and Group B. Each of these two groups contains a subgroup of eight I/O lines called as 8-bit port and another subgroup of four lines or a 4-bit port. Thus Group A contains an 8-bit port A along with a 4-bit port C upper. The port A lines are identified by symbols PA0-PA7 while the port C lines are identified as PC4-PC7. Similarly, Group B contains an 8bit port B, containing lines PB0-PB7 and a 4-bit port C with lower bits PC0- PC3. The port C upper and port C lower can be used in combination as an 8-bit port C.Both the port C are assigned the same address. Thus one may have either three 8bit I/O ports or two 8-bit and two 4-bit ports from 8255. All of these ports can function independently either as input or as output ports. This can be achieved by programming the bits of an internal register of 8255 called as control word register (CWR).

The 8-bit data bus buffer is controlled by the read/write control logic. The read/write control logic manages all of the internal and external transfers of both data and control words. RD, WR, A1, A0 and RESET are the inputs provided by the microprocessor to the READ/ WRITE control logic of 8255. The 8-bit, 3-state bidirectional buffer is used to interface the 8255 internal data bus with the external system data bus. This buffer receives or transmits data upon the execution of input or output instructions by the microprocessor. The control words or status information is also transferred through the buffer. The signal description of 8255 are briefly presented as follows :

PA7-PA0: These are eight port A lines that acts as either latched output or buffered input lines depending upon the control word loaded into the control word register.

PC7-PC4: Upper nibble of port C lines. They may act as either output latches or input buffers lines. This port also can be used for generation of handshake lines in mode 1 or mode

PC3-PC0 :These are the lower port C lines, other details are the same as PC7-PC4 lines.PB0-PB7 : These are the eight port B lines which are used as latched output lines or buffered input lines in the same way as port A.

RD : This is the input line driven by the microprocessor and should be low to indicate read operation to 8255.

WR : This is an input line driven by the microprocessor. A low on this line indicates write operation.

CS : This is a chip select line. If this line goes low, it enables the 8255 to respond to RD and WR signals, otherwise RD and WR signal are neglected. A1-A0 : These are the address input lines and are driven by the microprocessor. These lines A1-A0 with RD, WR and CS from the following operations for 8255. These address lines are used for addressing any one of the four registers, i.e. three ports and a control word register as given in table below. In case of 8086 systems, if the 8255 is to be interfaced with lower order data bus, the A0 and A1 pins of 8255 are connected with A1 and A2 respectively.

D0-D7 : These are the data bus lines those carry data or control word to/from the microprocessor.

RESET : A logic high on this line clears the control word register of 8255. All ports are set as input ports by default

Figure 2.1 Block Diagram of 8255 PPI

#### **2.2 Pins Details**

|                                     | $\neg$ $-$ |                          | - F                               |       |                                   |

|-------------------------------------|------------|--------------------------|-----------------------------------|-------|-----------------------------------|

| $PA, \leftrightarrow 1$             | 0          | 40 + PA                  |                                   |       |                                   |

| $PA_2 \leftrightarrow 2$            |            | 39 + PA,                 | $D_0 - D_7$                       |       |                                   |

| $PA_i \leftrightarrow 3$            |            | 38 + PA                  | $\overset{\leftrightarrow}{\ast}$ |       | $PA_7 - PA_0$                     |

| $PA_{0} \leftrightarrow 4$          |            | 37 + PA,                 | °                                 |       | 8                                 |

| $\overrightarrow{RD} \rightarrow 5$ |            | 36 🔶 WR                  | $\overline{RD} \rightarrow$       |       | -                                 |

| $\overline{CS} \rightarrow 6$       |            | 35 - RESET               |                                   |       |                                   |

| $V_{ss} \leftarrow 7$               |            | 34 🔶 D.                  | $\overline{WR} \rightarrow$       |       | PC, - PC,                         |

| $A_1 \rightarrow 8$                 |            | 33 🔶 D,                  |                                   |       | ic, ic,                           |

| $A_0 \rightarrow 9$                 | 8255A      | $32 \leftrightarrow D_2$ | $A_1 \rightarrow$                 | 8255A | 4                                 |

| PC, ↔ 10                            |            | 31 ( > D,                |                                   |       |                                   |

| $PC_{6} \leftrightarrow 11$         | 8          | 30 + D                   | $\sim \rightarrow$                |       |                                   |

| PC, + 12                            |            | 29 + D,                  |                                   |       | <b>DC DC</b>                      |

| PC + 13                             |            | 28 + D F                 | RESET ->                          |       | PC <sub>3</sub> - PC <sub>0</sub> |

| $PC_{o} \leftrightarrow 14$         | 5          | $27 \leftrightarrow D,$  |                                   |       |                                   |

| $PC, \leftrightarrow 15$            |            | $26 \leftarrow V_{cc}$   | $\overline{cs} \rightarrow$       |       | -                                 |

| PC, () 16                           |            | 25 + PB,                 |                                   |       |                                   |

| PC, ↔ 17                            |            | 24 +> PB, (+:            | $(v)_{cc} \rightarrow$            | ÷ .   | PB, - PB                          |

|                                     |            |                          |                                   |       | K/>                               |

|                                     |            | 22 + PB,                 | 0V)V <sub>ss</sub> ←              |       | 8                                 |

| $PB_2 \leftrightarrow 20$           |            | 21 ↔ PB,                 | 1 22                              |       |                                   |

| · · /                               |            |                          | _                                 |       |                                   |

Figure 2.2 Pin Diagram of 8255PPI

It has a 40 pins of 4 groups.

- 1. Data bus buffer

- 2. Read Write control logic

- 3. Group A and Group B controls

- 4. Port A, B and C

Data bus buffer: This is a tristate bidirectional buffer used to interface the 8255 to system databus. Data is transmitted or received by the buffer on execution of input or output instruction by the CPU.

Control word and status information are also transferred through this unit. Read/Write control logic: This unit accepts control signals (RD, WR) and also inputs from address bus and issues commands to individual group of control blocks (Group A, Group B).

• It has the following pins.

a) CS – Chipselect : A low on this PIN enables the communication between CPU and 8255.

b) RD (Read) – A low on this pin enables the CPU to read the data in the ports or the status word through data bus buffer.

c) WR (Write) : A low on this pin, the CPU can write data on to the ports or on to the control register through the data bus buffer.

d) RESET: A high on this pin clears the control register and all ports are set to the input modee) A0 and A1 (Address pins): These pins in conjunction with RD and WR pins control the selection of one of the 3 ports.

• *Group A and Group B controls* : These block receive control from the CPU and issues commands to their respective ports.

• Group A - PA and PCU (PC7 –PC4)

• Group B - PCL (PC3 – PC0)

• Control word register can only be written into no read operation of the CW register is allowed.

a) Port A: This has an 8 bit latched/buffered O/P and 8 bit input latch. It can be programmed in 3 modes – mode 0, mode 1, mode 2.

b) Port B: This has an 8 bit latched / buffered O/P and 8 bit input latch. It can be programmed in mode 0, mode1.

c) Port C : This has an 8 bit latched input buffer and 8 bit out put latched/buffer. This port can be divided into two 4 bit ports and can be used as control signals for port A and port B. it can be programmed in mode 0.

#### 1.2.1 Modes of Operation of 8255

• These are two basic modes of operation of 8255. I/O mode and Bit Set-Reset mode (BSR).

• In I/O mode, the 8255 ports work as programmable I/O ports, while in BSR mode only port C (PC0-PC7) can be used to set or reset its individual port bits.

• Under the I/O mode of operation, further there are three modes of operation of 8255, so as to support different types of applications, mode 0, mode 1 and mode 2.

I/O Modes This mode is also called as basic input/output mode. This mode provides simple input and output capabilities using each of the three ports. Data can be simply read from and written to the input and output.

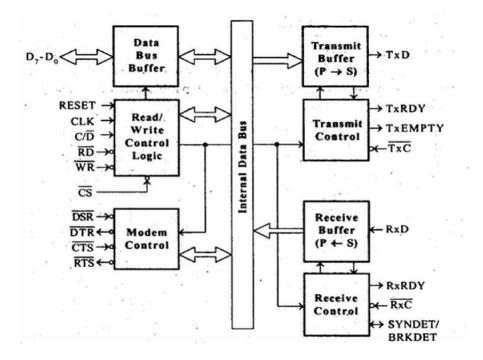

#### 2.3 8251USART

Figure 2.3 Block diagram of the 8251 USART

The 8251 functional configuration is programmed by software. Operation between the 8251 and a CPU is executed by program control. Table 1 shows the operation between a CPU and the device. **Table 2.1 Control Word**

| CS | C/D | $\overline{\mathbf{RD}}$ | WR |                               |

|----|-----|--------------------------|----|-------------------------------|

| 1  | ×   | ×                        | ×  | Data Bus 3-State              |

| 0  | ×   | 1                        | 1  | Data Bus 3-State              |

| 0  | 1   | 0                        | 1  | Status $\rightarrow$ CPU      |

| 0  | 1   | 1                        | 0  | Control Word $\leftarrow$ CPU |

| 0  | 0   | 0                        | 1  | $Data \rightarrow CPU$        |

| 0  | 0   | 1                        | 0  | Data ← CPU                    |

## **2.4 Control Words**

There are two types of control word.

- 1. Mode instruction (setting of function)

- 2. Command (setting of operation)

#### 2.4.1Mode Instruction

Mode instruction is used for setting the function of the 8251. Mode instruction will be in "wait for write" at either internal reset or external reset. That is, the writing of a control word after resetting will be recognized as a "mode instruction." Items set by mode instruction are as follows:

- Synchronous/asynchronous mode

- Stop bit length (asynchronous mode)

- Character length

- Parity bit

- Baud rate factor (asynchronous mode)

- Internal/external synchronization (synchronous mode)

- Number of synchronous characters (Synchronous mode)

The bit configuration of mode instruction is shown in Figures 2 and 3. In the case of synchronous mode, it is necessary to write one-or two byte sync characters. If sync characters were written, a function will be set because the writing of sync characters constitutes part of mode instruction.

#### 2.4.2 Command

Command is used for setting the operation of the 8251. It is possible to write a command whenever necessary after writing a mode instruction and sync characters. Items to be set by command are as follows:

- Transmit Enable/Disable

- Receive Enable/Disable

- DTR, RTS Output of data.

- Resetting of error flag.

- Sending to break characters

- Internal resetting

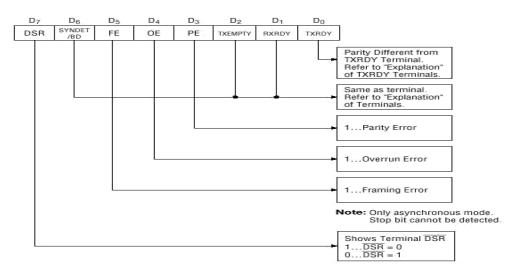

Fig. 5 Bit Configuration of Status Word

#### Figure 2.4 Control Word Format

## 2.4.3Status Word

It is possible to see the internal status of the 8251 by reading a status word. The bit configuration of status word is shown in Fig. 5.

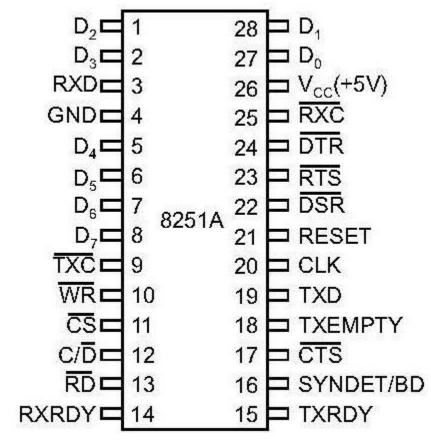

#### 2.5 Pin Description

D 0 to D 7 (l/O terminal)

This is bidirectional data bus which receive control words and transmits data from the CPU and sends status words and received data to CPU.

RESET (Input terminal)

A "High" on this input forces the 8251 into "reset status." The device waits for the writing of "mode instruction." The min. reset width is six clock inputs during the operating status of CLK. CLK (Input terminal)

CLK signal is used to generate internal device timing. CLK signal is independent of RXC or TXC. However, the frequency of CLK must be greater than 30 times the RXC and TXC at Synchronous mode and Asynchronous "x1" mode, and must be greater than 5 times at Asynchronous "x16" and "x64" mode.

#### WR (Input terminal)

This is the "active low" input terminal which receives a signal for writing transmit data and control words from the CPU into the 8251.

#### RD (Input terminal)

This is the "active low" input terminal which receives a signal for reading receive data and status words from the 8251.

C/D (Input terminal)

This is an input terminal which receives a signal for selecting data or command words and status words when the 8251 is accessed by the CPU. If C/D = low, data will be accessed. If C/D = high, command word or status word will be accessed.

#### CS (Input terminal)

This is the "active low" input terminal which selects the 8251 at low level when the CPU accesses. Note: The device won't be in "standby status"; only setting CS = High.

#### TXD (output terminal)

This is an output terminal for transmitting data from which serial-converted data is sent out. The device is in "mark status" (high level) after resetting or during a status when transmit is disabled. It is also possible to set the device in "break status" (low level) by a command.

#### TXRDY (output terminal)

This is an output terminal which indicates that the 8251 is ready to accept a transmitted data character. But the terminal is always at low level if CTS = high or the device was set in "TX disable status" by a command. Note: TXRDY status word indicates that transmit data character is receivable, regardless of CTS or command. If the CPU writes a data character, TXRDY will be reset by the leading edge or WR signal.

#### TXEMPTY (Output terminal)

This is an output terminal which indicates that the 8251 has transmitted all the characters and had no data character. In "synchronous mode," the terminal is at high level, if transmit data characters are no longer remaining and sync characters are automatically transmitted. If the CPU writes a data character, TXEMPTY will be reset by the leading edge of WR signal. Note : As the transmitter is disabled by setting CTS "High" or command, data written before disable will be sent out. Then TXD and TXEMPTY will be "High". Even if a data is written after disable, that data is not sent out and TXE will be "High".After the transmitter is enabled, it sent out. (Refer to Timing

Chart of Transmitter Control and Flag Timing)

#### TXC (Input terminal)

This is a clock input signal which determines the transfer speed of transmitted data. In "synchronous mode," the baud rate will be the same as the frequency of TXC. In "asynchronous mode", it is possible to select the baud rate factor by mode instruction. It can be 1, 1/16 or 1/64 the TXC. The falling edge of TXC sifts the serial data out of the 8251.

RXD (input terminal)

This is a terminal which receives serial data.

## RXRDY (Output terminal)

This is a terminal which indicates that the 8251 contains a character that is ready to READ. If the CPU reads a data character, RXRDY will be reset by the leading edge of RD signal.

Unless the CPU reads a data character before the next one is received completely, the preceding data will be lost. In such a case, an overrun error flag status word will be set.

## RXC (Input terminal)

This is a clock input signal which determines the transfer speed of received data. In "synchronous mode," the baud rate is the same as the frequency of RXC. In "asynchronous mode," it is possible to select the baud rate factor by mode instruction. It can be 1, 1/16, 1/64 the RXC.

#### SYNDET/BD (Input or output terminal)

This is a terminal whose function changes according to mode. In "internal synchronous mode." this terminal is at high level, if sync characters are received and synchronized. If a status word is read, the terminal will be reset. In "external synchronous mode, "this is an input terminal. A "High" on this input forces the 8251 to start receiving data characters.

In "asynchronous mode," this is an output terminal which generates "high level"output upon the detection of a "break" character if receiver data contains a "low-level" space between the stop bits of two continuous characters. The terminal will be reset, if RXD is at high level. After Reset is active, the terminal will be output at low level.

DSR (Input terminal)

This is an input port for MODEM interface. The input status of the terminal can be recognized by the CPU reading status words.

DTR (Output terminal)

This is an output port for MODEM interface. It is possible to set the status of DTR by a command.

CTS (Input terminal)

This is an input terminal for MODEM interface which is used for controlling a transmit circuit. The terminal controls data transmission if the device is set in "TX Enable" status by a command. Data is transmitable if the terminal is at low level.

RTS (Output terminal)

This is an output port for MODEM interface. It is possible to set the status RTS by a command.

Fig 2.5 Pin Diagram of 8251

#### 2.6 DMA Controller

- The DMA I/O technique provides direct access to the memory while the microprocessor is temporarily disabled.

- This chapter also explains the operation of disk memory systems and video systems that are often DMA-processed.

- Disk memory includes floppy, fixed, and optical disk storage. Video systems include digital and analog monitors.

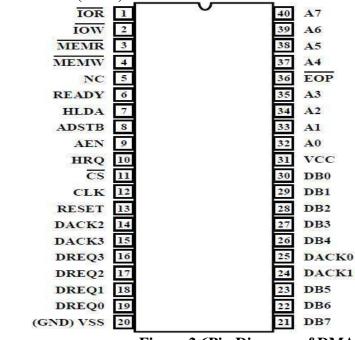

#### 2.6.1 Pin Details of DMA( 8237)

Figure 2.6Pin Diagarm of DMA

A DMA controller is a device, usually peripheral to a CPU that is programmed to perform a sequence of data transfers on behalf of the CPU. A DMA controller can directly access memory and is used to transfer data from one memory location to another, or from an I/O device to memory and vice versa. A DMA controller manages several DMA channels, each of which can be programmed to perform a sequence of these DMA transfers. Devices, usually I/O peripherals, that acquire data that must be read (or devices that must output data and be written to) signal the DMA controller to perform a DMA transfer by asserting a hardware DMA request (DRQ) signal. A DMA request signal for each channel is routed to the DMA controller. This signal is monitored and responded to in much the same way that a processor handles interrupts. When the

DMA controller sees a DMA request, it responds by performing one or many data transfers from that I/O device into system memory or vice versa. Channels must be enabled by the processor for the DMA controller to respond to DMA requests. The number of transfers performed, transfer modes used, and memory locations accessed depends on how the DMA channel is programmed. A DMA controller typically shares the system memory and I/O bus with the CPU and has both bus master and slave capability.

In bus master mode, the DMA controller acquires the system bus (address, data, and control lines) from the CPU to perform the DMA transfers. Because the CPU releases the system bus for the duration of the transfer, the process is sometimes referred to as cycle stealing.

In bus slave mode, the DMA controller is accessed by the CPU, which programs the DMA controller's internal registers to set up DMA transfers. The internal registers consist of source and destination address registers and transfer count registers for each DMA channel, as well as control and status registers for initiating, monitoring, and sustaining the operation of the DMA controller.

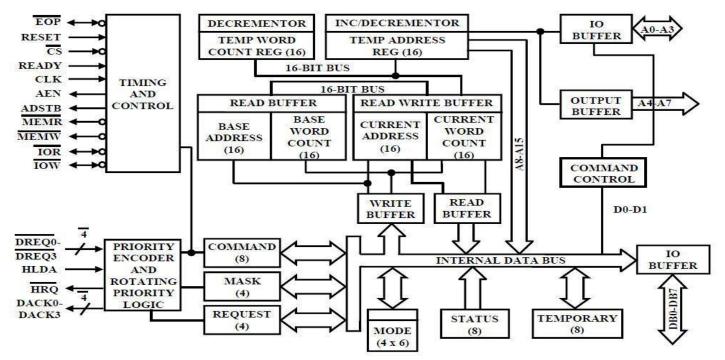

**Figure 2.7 Block Diagram**

#### DMA Controller Operation Steps in a Typical DMA cycle

Device wishing to perform DMA asserts the processors bus request signal.

- 1. Processor completes the current bus cycle and then asserts the bus grant signal to the device.

- 2. The device then asserts the bus grant ack signal.

- 3. The processor senses in the change in the state of bus grant ack signal and starts listening to the data and address bus for DMA activity.

- 4. The DMA device performs the transfer from the source to destination address.

- 5. During these transfers, the processor monitors the addresses on the bus and checks if any location modified during DMA operations is cached in the processor. If the processor detects a cached address on the bus, it can take one of the two actions: Processor invalidates the internal cache entry for the address involved in DMA write operation

Processor updates the internal cache when a DMA write is detected

6. Once the DMA operations have been completed, the device releases the bus by asserting the bus release signal.

#### **Reference Books:**

1.Ramesh S Gaonkar, Microprocessor Architecture, Programming and application with 8085, 4» Edition, Penram International Publishing, New Delhi, 2000

2. Kennith J. Ayala, 8051 Microcontroller, Thomson, 2005.

3. Dougles V. Hall, Microprocessor and Interfacing, Tata MC Graw Hill Publication, 2. (Edition, 1992.

4. Charless M. Gilmore, "Microprocessor Principle and application, McGraw Hill publication, 1995.

5. A.NagoorKani, Microprocessor & Microcontroller, Tata Mc Graw Hill, 3«Edition, 2012

B. Ram, Fundamentals of Microprocessors and Microcomputers, Dhanpat Rai Publications, 2001.

# SCHOOL OF BIO AND CHEMICAL ENGINEERING DEPARTMENT OF BIOMEDICAL ENGINEERING

UNIT- IIII

**Fundamentals of Microprocessor and Microcontroller – SEC1323**

INTRODUCTION TO 8086

Architecture of 8086 - Registers set of 8086 - Special function of general purpose register - Addressing modes of 8086 - Instruction set - pin diagram of 8086 - Timing diagram- memory read, memory write, I/O read and I/O write - Minimum and Maximum mode of operation Interrupts of 8086.

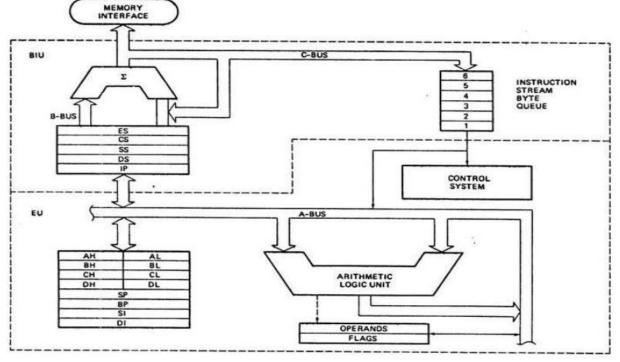

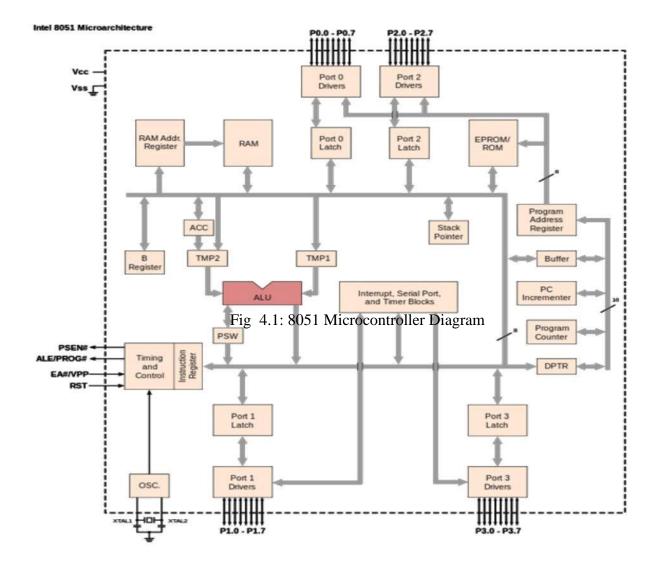

#### 3.1 8086 Microprocessor Architecture

Intel 8086 was the first 16-bit microprocessor introduced by Intel in 1978.

The 8086 architecture supports

- 16-bit ALU.

- a set of 16 bit registers

- provides segmented memory addressing scheme

- a rich instruction set.

- Powerful interrupt structure

- Fetched instruction queue for overlapped fetching and execution step.

The internal block diagram units inside the 8086 microprocessor is shown in the figure.

Fig. 1: Block Diagram of Intel 8086

The architecture of 8086 can be divided into two parts

- Bus Interface unit (BIU)

- Execution unit (EU)

The bus interface unit is responsible for physical address calculations and a predecoding

instruction byte queue ( 6 bytes long). The bus interface unit makes the system bus signal available for external devices. The 8086 addresses a segmented memory. The complete physical address which is 20-bits long is generated using segment and offset registers, each 16-bits long.

#### **1.1 Generation a Physical Address:**

- The content of segment register (segment address) is shifted left bit-wise four times.

- The content of an offset register (offset address) is added to the result of the previous shift operation.

The segment register indicates the base address of a particular segment and *CS*, *DS*, *SS* and *ES* are used to keep the segment address. The offset indicates the distance of the required memory location in the segment from the base address, and the offset may be the content of register *IP*, *BP*, *SI*, *DI* and *SP*. Once the opcode is fetched and decoded, the external bus becomes free while the Execution Unit is executing the instruction. While the fetched instruction is executed internally, the external bus is used to fetch the machine code of the next instruction and arrange it in a queue called as predecoded instruction byte queue. This is a 6 byte long queue, works in first-in first-out policy. While the opcode is fetched by the bus interface unit (BIU), the execution unit (EU) executes the previously decoded instruction concurrently. The execution unit contains.

- b) the register set of 8086 except segment registers and IF.

- c) a 16-bit ALU to perform arithmetic & logic operation

- d) 16-bit flag register reflects the results of execution by the ALU.

- e) the decoding units decodes the op-code bytes issued from the instruction byte queue.

- f) the timing and control unit generates the necessary control signals to execute the instruction op-code received from the queue.

The execution unit may pass the results to the bus interface unit for storing them in memory.

#### **3.2Memory Segmentation:**

The size of address bus of 8086 is 20 and is able to address 1 Mbytes ( $2^{20}$ ) of physical memory. The compete 1 Mbytes memory can be divided into 16 segments, each of 16 Kbytes size. The addresses of the segment may be assigned as 0000*H* to *F*000*H* respectively. The offset values are from 0000*H* to *FFFFFH*. If the segmentation is done as per above mentioned way, the segments are called non-overlapping segments.

In some cases segment may overlap also. Suppose a segment starts at a particular address and its maximum size can go up to 64 Kbytes. But if another segment starts before this 64 Kbytes location of the first segment, the two segments are said to be overlapping segment.

The main advantages of the segmented memory scheme are as follows:

- a Allows the memory capacity to be 1 Mbyte although the actual addresses to be handled are of 16-bit size

- b Allows the placing of code data and stack portions of the same program in different parts (segments) of memory, for data and code protection.

- c Permits a program and/ or its data to be put into different areas of memory each time program is executed, ie, provision for relocation may be done.

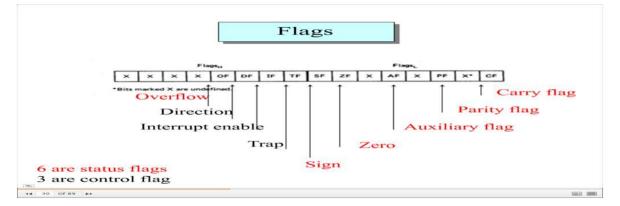

# 3.3 Flag Register

A 16 flag register is used in 8086. It is divided into two parts .

- Condition code or status flags

- Machine control flags

The condition code flag register is the lower byte of the 16-bit flag register. The condition code flag register is identical to 8085 flag register, with an additional overflow flag. The control flag register is the higher byte of the flag register. It contains three flags namely direction flag(D), interrupt flag (I) and trap flag (T). The complete bit configuration of 8086 is shown in the figure 2

Fig 3.2 Flags Format

- S- Sign Flag : This flag is set, when the result of any computation is negative.

- *Z* Zero Flag: This flag is set, if the result of the computation or comparison performed by the previous instruction is zero.

- P- Parity Flag: This flag is set to 1, if the lower byte of the result contains even number of 1's.

- *C* Carry Flag: This flag is set, when there is a carry out of MSB in case of addition or a borrow in case of subtraction.

- *T* Tarp Flag: If this flag is set, the processor enters the single step execution mode.

- *I* Interrupt Flag: If this flag is set, the maskable interrupt are recognized by the CPU, otherwise they are ignored.

- *D* Direction Flag: This is used by string manipulation instructions. If this flag bit is \_0', the string is processed beginning from the lowest address to the highest address, i.e., auto incrementing mode. Otherwise, the string is processed from the highest address towards the lowest address, i.e., auto incrementing mode.

- *AC*-Auxilary Carry Flag: This is set, if there is a carry from the lowest nibble, i.e, bit three during addition, or borrow for the lowest nibble, i.e, bit three, during subtraction.

- *O* Over flow Flag: This flag is set, if an overflow occurs, i.e, if the result of a signed operation is large enough to accommodate in a destination register. The result is of more than 7-bits in size in case of 8-bit signed operation and more than 15-bits in size in case of 16-bit sign operations, then the overflow will be set.

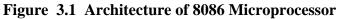

#### 3.4 Pin Details of 8086

The 8086 is a 16-bit microprocessor. These microprocessors operate in single processor or multiprocessor configurations to achieve high performance. The pin configuration of 8086 is shown in the figure. Some of the pins serve a particular function in minimum mode (single processor mode) and others function in maximum mode (multiprocessor mode).

|           |             |      |      | MAX<br>MODE | MIN ×<br>MODE |

|-----------|-------------|------|------|-------------|---------------|

| /ss (GND) | <b>d</b> 1  | 5    | 40   | Voc (5P)    |               |

| AD14      | 02          |      | 39 🗖 | AD15        |               |

| AD13      | <b>d</b> 3  |      | 38 🗖 | A16/S3      |               |

| AD12      | 04          |      | 37 🗖 | A17/S4      |               |

| AD11      | 05          |      | 36   | A18/S5      |               |

| AD10      | 08          |      | 35   | A19/S6      |               |

| AD9       | 07          |      | 34 0 | BHE/S7      |               |

| AD8       | 08          |      | 33   | MN/MX       |               |

| AD7       | <b>D</b> 9  |      | 32   | RD          |               |

| AD8       | <b>D</b> 10 | 8    | 31   | RQ/GTO      | HOLD          |

| AD5       | <b>D</b> 11 | 8086 | 30   | RQ/GT1      | HLDA          |

| AD4       | C 12        | œ    | 29   | LOCK        | WR            |

| AD3       | <b>□</b> 13 |      | 28   | 52          | MIO           |

| AD2       | <b>D</b> 14 |      | 27 0 | ST          | DT/R          |

| AD1       | <b>1</b> 15 |      | 26   | 50          | DEN           |

| ADD       | <b>D</b> 16 |      | 25   | QS0         | ALE           |

| NMI       | <b>C</b> 17 |      | 24   | QS1         | INTA          |

| INTR      | <b>D</b> 18 |      | 23 0 | TEST        |               |

| CLK       | <b>D</b> 19 |      | 22 0 | READY       |               |

| /ss (GND) | <b>D</b> 20 |      | 21   | RESET       |               |

#### Figure 3.3 Pin Configuration

#### 3.5 Description of signals of 8086

$AD_7$   $AD_0$  The address/ data bus lines are the multiplexed address data bus and contain the right most eight bit of memory address or data. The address and data bits are

separated by using ALE signal.

- $AD_{15}$   $AD_8$  The address/data bus lines compose the upper multiplexed address/data bus. This lines contain address bit  $A_{15}$   $A_8$  or data bus  $D_{15}$   $D_8$ . The address and data bits are separated by using *ALE* signal.

- $A_{19} / S_6$   $A_{18} / S_3$  The address/status bus bits are multiplexed to provide address signals  $A_{19} A_{16}$ and also status bits  $S_6 S_3$ . The address bits are separated from the status bits using the ALE signals. The status bit  $S_6$  is always a logic 0, bit  $S_5$  indicates the condition of the interrupt flag bit. The  $S_4$  and  $S_3$  combinedly indicate which segment register is presently being used for memory access.

| $S_4$ | <b>S</b> <sub>3</sub> | Funtion       |

|-------|-----------------------|---------------|

| 0     | 0                     | Extra segment |

| 0 | 1 | Stack segment      |

|---|---|--------------------|

| 1 | 0 | Code or no segment |

| 1 | 1 | Data Segment       |