# SCHOOL OF ELECTRICAL AND ELECTRONICS

DEPARTMENT OF ELECTRONICS AND COMMMUNICATION ENGINEERING

# UNIT - I ANALOG INTEGRATED CIRCUITS – SEC1302

# 1.1 INTRODUCTION TO OPERATIONAL AMPLIFIER

#### 1.1.1 Integrated Circuit

An Integrated circuit is a miniature electronic circuit comprising of active and passive components irreparably (impossible to rectify or repair) joined together on a single chip of Silicon.

Possible question: Define Integrated Circuit.

1.1.2 Advantages of Integrated circuits over discrete component circuits

The integrated circuits are advantageous than that of discrete component circuit with some advantages listed below.

- 1. Miniaturization and hence density of equipment increased. (Since they are of small size, equipment can hold more components within a same area)

- 2. Cost is reduced when manufactured in batch processing.

- 3. Improvised system reliability due to elimination of soldered joints.

- 4. Complex circuits can be fabricated with better characteristics and thus functional performance is improvised.

- 5. Increased operating speeds due to minimized parasitic capacitance

- 6. Power consumption minimized.

Possible question: List the advantages of IC over discrete circuits.

1.1.3 Building Blocks of an Operational Amplifier

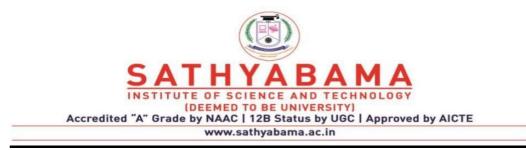

An operational amplifier is internally built by four blocks namely

- 1. Unbalanced differential amplifier,

- 2. Balanced differential amplifier,

- **3.** Buffer and level translator and

- 4. Output stage (Push-pull Amplifier) as shown in the figure, fig. 1.4.

Fig.1.1.3. Building blocks of an OP AMP

Stage 1

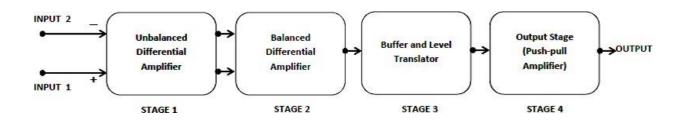

This stage offers high impedance to the input terminals. Since it is an unbalanced amplifier, it amplifies the inputs individually with high impedance and the output shall be fed into next stage of balanced amplifier. (Reference figure, fig.1.1.3.1)

Stage 2

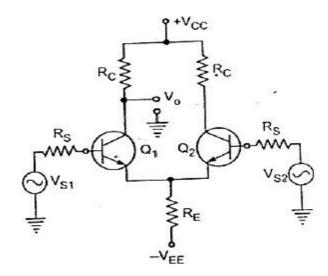

Since it is a balanced amplifier, it gives differential output with high gain. This is the stage where high gain is provided and the output is difference between the input signals with low common mode signal. (Reference figure, fig. 1.1.3.2)

The above differential amplifiers provide high gain and input impedance with less input current entering into it. *Stage 3*

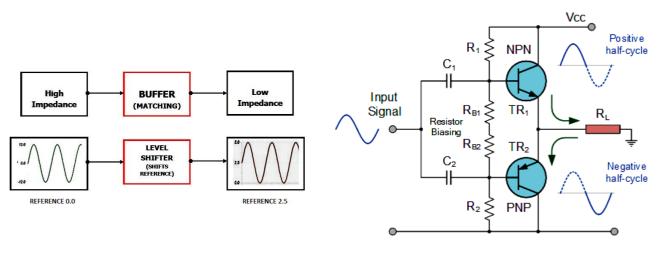

This stage comprises of buffer and level shifter circuits.

Level shifter circuit shifts the reference level of a signal. As shown in figure, fig.1.1.3.3, the input reference level 0.0 is shifted to 2.5 in output signal. Thus this circuit can shift the reference level of the input.

Buffer circuit matches an input circuit of impedance low (or high) with an output load of high (or low) impedance. If they both are connected without this buffer matching circuit, the load drains more current from the input circuit leading to shift of operating point which in turn induces unwanted effect.

#### Stage 4

Stage four (output stage) is for improvising current, thus a push-pull complementary symmetry amplifier as shown in figure, fig.1.1.3.4. The amplifier separately amplifies positive and negative cycle with NPN and PNP resistors respectively. During positive cycle, current flows into load resistance RL, but in negative cycle current flows from RL in opposite direction. Thus by carefully choosing the value of load resistance, RL, the output amplitude can be varied.

Fig.1.1.3.1. Unbalanced Differential Amplifier

Fig.1.1.3.2. Unbalanced Differential Amplifier

**Fig.1.1.3.3. Buffer and Level translator**

Fig.1.1.3.4. Push-pull Amplifier

Possible question: Elaborately explain the building blocks of an operational amplifier with neat sketches.

1.1.4 Ideal operational amplifier

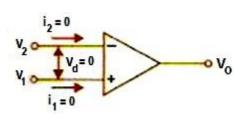

An Ideal operational amplifier is shown in the figure, fig. 1.1.4.a.

In an ideal op amp,

- 1. The currents entering the input terminals 1 and 2, i1 and i2 respectively, shall be zero. i1=i2=0.

- 2. The voltages between reference and the input terminals 1 and 2, V1 and V2 respectively, shall be equal. V1=V2.

- 3. The difference between input terminal voltages, Vd shall be zero. Vd=V2 V1.

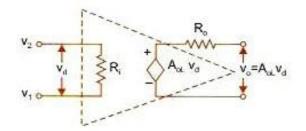

As per the figure shown as equivalent circuit, fig. 1.1.4.b, input resistance Ri, output resistance R<sub>0</sub> and open loop gain AOL shall be explained further.

- 4. Input resistance Ri shall be very high (Ideally  $Ri=\infty$ )

- 5. Output resistance R<sub>0</sub> shall be very low (Ideally R<sub>0</sub>=0)

- 6. Open loop gain AOL shall be very high (Ideally AOL=∞)

Fig.1.1.4.a. Ideal OP AMP

Fig. 1.1.4.b. OP AMP equivalent circuit

Thus ideal op amp shall be an infinite gain amplifier with zero input currents, infinite input resistance and zero output resistance.

Possible question: What are all the characteristics of Ideal operational amplifier?

## **1.2 DC AND AC CHARACTERISITCS**

The two main categories of op amp characteristics are DC and AC Characterisitics.

# **1.2.1 DC Characteristics**

DC characteristics are analyzed when input of the op amp is dc signal. The dc characteristics of op amp and thus it shall be discussed in following section.

**1.2.1.1** Input offset voltage (VIOS)

The dc voltage connected any one of the input terminal to make the output offset voltage.

When output offset voltage is more than zero, the non-inverting terminal is supposed to have higher potential than that of inverting terminal due to internal imbalance. So input offset voltage is connected to inverting terminal to compensate the offset and the output voltage to zero.

When output offset voltage is less than zero, the inverting terminal is supposed to have higher potential than that of non-inverting terminal due to internal imbalance. So input offset voltage is connected to non-inverting terminal to compensate the offset and the output voltage to zero.

Thus this dc input offset voltage is known as compensating voltage for output offset voltage.

Possible question: Define Input offset voltage, input offset current, input bias current and output offset voltage.

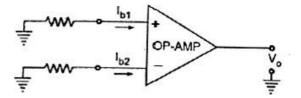

# **1.2.1.2** Input bias current (IB)

For an ideal op amp, the dc currents entering the input terminals shall be zero. But practically a minimum amount of current enters the terminals and they are termed as bias currents.

Fig. 1.2.1.2.a. Input bias currents

The bias current entering non-inverting terminal is Ib1 and entering inverting terminal is Ib2. These currents flow into the respective terminals when both input terminals are grounded. The total input bias current is the average currents entering into both the terminals.

$$l_{B} = \frac{l_{b1} + l_{b2}}{2}$$

(Eq.1.2.1.2)

# **1.2.1.3** Input offset current (IIOS)

Input dc offset current is the difference between the magnitudes of bias currents Ib1 and Ib2 as shown in the equation 1.2.1.3. Practically this current is very small in magnitude in the order of nano-amperes.

$$= b_1 - b_2$$

(Eq.1.2.1.3)

# **1.2.1.4** Total Output offset voltage (VOOS)

As shown in the figure, fig.1.2.1.2.a, when both the inputs are connected to ground potential, the output dc voltage  $V_0$  should be zero ideally. But practically the output voltage is not zero. The value of this output voltage is termed as Total output offset voltage.

# **1.2.2** AC characteristics

AC characteristics are analyzed when input of the op amp is ac signal. Slew rate is a major ac characteristic of op amp and thus it shall be discussed in next section.

# **1.2.2.1** Slew rate

Slew rate is defined as the maximum rate of change of output voltage with time.

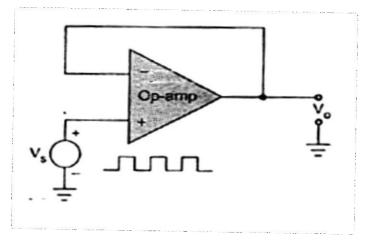

For this, a voltage follower circuit is chosen where output is fed-back directly to inverting terminal and the inverting terminal is connected to a rectangular pulse of 50% duty cycle (Square wave) as shown in figure, fig.1.2.2.1.a.

Fig. 1.2.2.1.a Measurement of slew rate of OP AMP

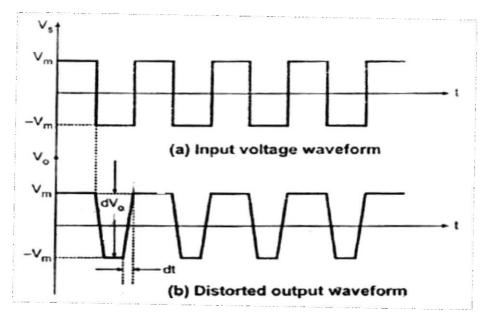

The output  $V_0$  is to follow the input. But as shown in figure, fig.1.2.2.1.b, the output wave is distorted and not a rectangular wave as input. Thus the variation of output is denoted by  $dV_0$ , change in voltage with change in time dt. Thus maximum change in output voltage with change in time is

Slew rate = S =

$$\frac{dV_o}{dt}\Big|_{max}$$

This is due to charging and discharging rate of an internal capacitance C of the op amp. The capacitor charges to maximum current  $I_{max}$  due to the input voltage fed in the capacitor. The sudden change in input voltage from low to high, allows the capacitor to charge to its maximum. Thus change in output voltage  $dV_0/dt$  mainly depends upon charging current  $I_{max}$  and the capacitance C.

Fig. 1.2.2.1.b. slew rate waveforms

Thus slew rate in terms of internal capacitance C is

$$S = \frac{l_{max}}{C}$$

**Slew Rate Equation**

Let the input voltage  $V_S$  is purely sinusoidal. In this case the output voltage  $V_0$  will be also purely sinusoidal, as the circuit used to derive the equation is voltage follower circuit as shown in the fig.1.2.2.1 (a). in such circuit output voltage follows input voltage.

So

And

But  $\frac{dV_o}{dt}$  maximum is nothing but theslew rate S. For maximum  $\frac{dV_{,in}}{dt}$  the equation above  $\cos(\Box t)$  must be maximum. i.e. 1.

$$S = \left[\frac{dV_o}{dt}\right]_{max} = \omega V_m$$

$$S = 2\pi f V_m V/sec$$

This is required slew-rate equation.

For the distortion free output, the maximum allowable frequency of operation *fm* can be decided by the slew rate.

Methods of improving Slewrate

It is known that the slew rate is given by,

$$S = \frac{I_{max}}{C}$$

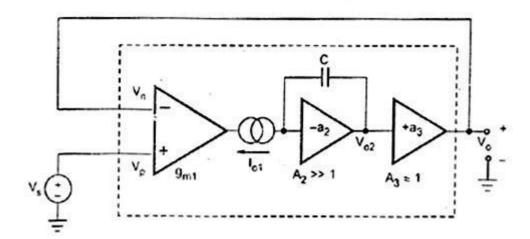

For understanding the methods of improving slew rate consider the op-amp model for the analysis of the slew rate as shown in the Fig. 1.2.2.3.

Fig.1.2.2.3 Op-amp model for slew rate analysis

The op-amp used is in voltage follower mode in which the output  $V_0 = V_i$ . The circuit is similar to that used earlier to derive slew rate equation, only the op-amp is replaced by its model.

When input overdrives the input stage then  $I_{max} = \pm I_{01}$  (sat) which are saturation current levels of the input stage. Under this condition, op-amp is said to be operating under large-signal conditions.

The saturation of the input stage limits the slew rate because under saturation condition, the rate at which capacitor C can charge or discharge, according to the input overdrive is at its maximum.

From the fig.1.2.2.3, we can write,

$$b_1(sat) = C \frac{dV_{02}}{dt}$$

$$\therefore \frac{dV_{02}}{dt} = \frac{b_1(sat)}{C}$$

This rate of change of V02 is maximum, due to the saturation effect. Now

the gain of the third stage  $a_3 \approx 1$ , hence  $V_0 = V_{02}$ ,

$$\therefore \frac{dV_{\mathcal{U}}}{dt} = \frac{dV_{\mathcal{U}}}{dt} = \frac{b_1(sat)}{C}$$

But maximum rate of change of output voltage is the slew rate.

$$S = \frac{b_1(sat)}{C}$$

Analyzing the op-amp model used, we can write,

$$V_{02} = dropacrossC = lo_1 Z_C$$

The input stage is a transconductance amplifier. i.e. voltage input, current output amplifier. For sufficiently small differential input voltage the relation between input voltage and output current for such an amplifier is,

$OutputCurrent = g_m(differentialInput)$

or inputstage

$$\therefore I_{01} = g_{m1}(V_p - V_n)$$

$$\therefore V_{02} = Z_C g_{m1}(V_p - V_n)$$

But,

$$V_{02} \approx V_o as a_3 \approx 1$$

$$\therefore V_0 = Z_C g_{m1} (V_p - V_n)$$

$$V_0 = \left[\frac{1}{j\omega C}\right] g_{m1} (V_p - V_n)$$

As,

$$Z_{C} = X_{C} = \left[-\frac{j}{\omega C}\right] = \frac{1}{j\omega C}$$

$$\therefore Op - amp \ gain = \frac{|V_{o}|}{|V_{p} - V_{n}|}$$

$$\therefore |a| = \frac{|V_{o}|}{|V_{p} - V_{n}|} = \frac{g_{m1}}{\omega C} = \frac{g_{m1}}{2\pi f C}$$

$$\therefore |a|f = \frac{g_{m1}}{2\pi C}$$

Here in the above equation Saturation current  $I_{01(sat)}$ , mutual conductance  $g_{m1}$ , and gain-bandwidth product  $f_t$  of the op amp can be set in accordingly to improve *slew rate*.

Improving slew rate by

1. Increasing saturation current  $I_{01(sat)}$ : This is very tough to increase because this may affect the operating point of the transistors used in the circuit.

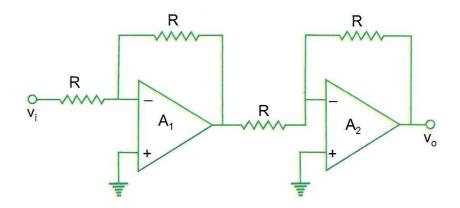

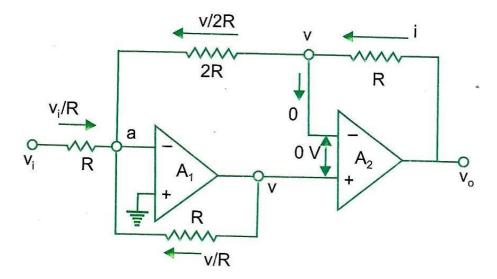

2. Increasing gain-bandwidth product ft: This is done by using feed-forward compensation. That is two op amps connected in series that one's output is fed into other. This improves the bandwidth by increasing gain-bandwidth product, thus improving slew rate.

**3**. Decreasing mutual conductance  $g_m1$ : This is done by replacing BJT by FET's. Normally FET's are having less mutual conductance  $g_m$  by improving slewrate.

Possible question: Define slew rate and write the slew rate equation. Explain about the methods of improving slew rate.

**1.2.2.2** Thermal drift

In op amp, effect of variation in all parameters is severe due to variations in temperature.

Effect on input offset voltage

Input offset voltage varies with variation in temperature and thus ratio of change in input offset voltage to change in temperature is termed as *thermal drift on input offset voltage*.

Inputoffsetvoltagedrift=  $\frac{\Delta V_{ios}}{\Delta T}$  (Eq.1.2.2.2.1)

Where  $\Delta T$ - change in temperature, $\Delta V_{00}$ - change in input offset voltageEffect on input offset current

Input offset current varies with variation in temperature and thus ratio of change in input offset current to change in temperature is termed as *thermal drift on input offset current*.

Input of f set current drift =  $\Delta T$

(Eq.1.2.2.2.2)

Where  $\Delta T$ - change in temperature, $\Delta I_{00}$ - change in input offset currentEffect on input bias current

A 1.1

Input bias current varies with variation in temperature and thus ratio of change in input bias current to change in temperature is termed as *thermal drift on input bias current*.

Inputbiascurrentdrift=

$$\frac{\Delta \Omega_{\rm LD}}{\Delta T}$$

(Eq.1.2.2.2.3)

Where  $\Delta T$ - change in temperature, $\Delta b$ - change in input bias current

Effect on slew rate

Slew rate varies with variation in temperature and thus ratio of change in slew rate to change in temperature is termed as *thermal drift on slew rate*.

slewratedrift=  $\Delta S / \Delta T$  — (Eq.1.2.2.2.4)

Where  $\Delta T$ -change in temperature, $\Delta S$ -change in slew ratePossible question: Explain Thermal drift on various parameters of op amp.

**1.2.2.3** Common Mode Rejection Ratio -CMRR

When the same voltage is applied to both the terminals of op amp, then the op amp is said to be operated in common mode configuration. Op amp is to be operated only in differential mode and common mode signals shall be noise or disturbance signal. The ability of differential amplifier is to reject the common mode signal and expressed as a ratio termed as Common mode rejection ratio (CMRR).

It is defined as ratio of the differential voltage gain (Ad) to common

$CMRR = \rho = \left|\frac{A_d}{A_c}\right|$  $CMRR \text{ in } dB = 20\log\left|\frac{A_d}{A_c}\right| \text{ in } dB$

Practically CMRR should be larger and ideally it shall be  $\infty$ . Possible questions: *Define CMRR*. **Open loop and closed loop configurations**

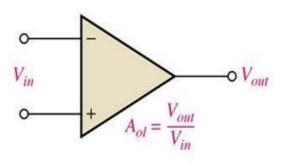

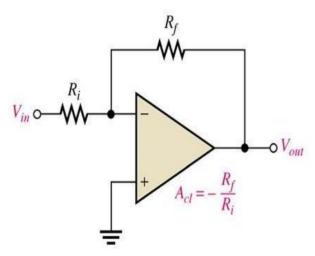

Fig.1.2.3.a Open loop configuration

Fig.1.2.3.b Closed loop configuration

**Open loop configuration**

$\label{eq:Asshown in figure, fig. 1.2.3.a, V_{in} is the input given between input terminals and V_{out} is the output derived.$  The open loop gain Aol is ratio of the output voltage (V\_{out}) to the input voltage (V\_{in}).

The open loop gain,  $A_{d} = \frac{V_{out}}{V_{in}}$  (Eq.1.2.3.1)

As stated above in eq.1.2.3.1, the gain cannot be controlled or changed. Thus this gain is implicit (in-built) and never be changed explicitly. This gain is very large in terms of 10000.

**Closed loop configuration**

As shown in figure, fig.1.2.3.b, Vin is the input given into inverting terminal through a resistance R<sub>i</sub> and a feed-back resistor Rf connected between output terminal and inverting terminal. Vout is the output derived. The open loop gain Acl is ratio of the feed-back resistor (Rf) to the resistance (Ri). The feedback is *negative*.

The closed loop gain,

$$A_d = -\frac{R_f}{R_i}$$

(Eq.1.2.3.2)

As stated above in eq.1.2.3.2, the gain now can be controlled or changed. Thus this gain is explicit and by changing the resistor values, gain can be altered.

Thus closed loop gain is advantageous over open loop gain because it can be changed by changing resistor values.

Possible question: Elaborately explain open loop and closed loop configurations of an op amp with neat sketches.

1.3.1 OP-AMP used in mathematical operations

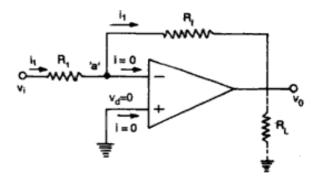

1.3.1 **Inverting Amplifier**

The amplifier in which the output is inverted i.e. having 180<sup>0</sup> phase shift with respect to the input is called an inverting amplifier.

This is possibly the most widely used of all the op-amp circuits. The circuit is shown in Fig. 1.3.1. The output voltage  $V_0$  is fed back to the inverting input terminal through the Rf – R1 network where Rf is the feedback resistor. Input signal vi is applied to the inverting input terminal through R1 and non-inverting input terminal of op-amp is grounded.

Assume an ideal op-amp. As Vd = 0, node 'a' is at ground potential and the current i1 through R1 is

Fig. 1.3.1. Inverting amplifier

Also since op-amp draws no current, all the current flowing through R1 must flow through Rf. The output voltage is given by

$$v_{o} = -i_{1}R_{f} = -v_{i}\frac{R_{f}}{R_{1}}$$

Hence, the gain of the inverting amplifier (also referred as closed loop gain) is given by

$$A_{\rm CL} = \frac{v_0}{v_{\rm i}} = -\frac{R_{\rm f}}{R_{\rm i}}$$

Alternatively, the nodal equation at the node 'a' in Fig. 1.3.1 is given by

$$\frac{v_{\rm a} - v_{\rm i}}{R_{\rm 1}} + \frac{v_{\rm a} - v_{\rm 0}}{R_{\rm f}} = 0$$

where v<sub>a</sub> is the voltage at node 'a'. Since node 'a' is at virtual ground v<sub>a</sub>=0. Therefore, we get,

$$A_{\rm CL} = \frac{v_0}{v_i} = -\frac{R_{\rm f}}{R_{\rm i}}$$

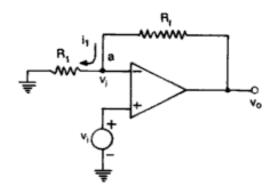

#### **1.3.2** Non-Inverting Amplifier

The amplifier in which the output is amplified without any phase shift in between input and output is called non inverting amplifier.

If the signal is applied to the non-inverting input terminal and feedback is given as shown in Fig. 1.3.2. The circuit which amplifies without inverting the input signal. It may be noted that it is also a negative feed-back system as output is being fed back to the inverting input terminal.

As the differential voltage Vd at the input terminal of op-amp is zero, the voltage at node 'a' in Fig. 1.3. 2. is Vi same as the input voltage applied to non-inverting input terminal. Now Rf and R1 form a potential divider. Hence

Fig. 1.3.2 Non-inverting amplifier

$$v_i = \frac{v_o}{R_1 + R_f} R_1$$

As no current flows into the op-amp.

$$\frac{v_{0}}{v_{i}} = \frac{R_{1} + R_{f}}{R_{1}} = 1 + \frac{R_{f}}{R_{1}}$$

Thus, for non-inverting amplifier the voltage gain,

$$A_{\rm CL} = \frac{v_0}{v_1} = 1 + \frac{R_{\rm f}}{R_1}$$

The gain can be adjusted to unity or more, by proper selection of resistors Rf and R1. Compared to the inverting amplifier, the input resistance of the non-inverting amplifier is extremely large (=  $\Box$ ) as the op-amp draws negligible current from the signal source.

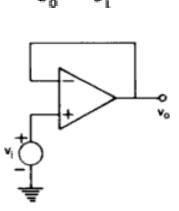

#### 1.3.3 Voltage Follower

In the non-inverting amplifier of Fig. 1.3.1, if Rf = 0 and  $R1 = \Box$ , we get the modified circuit of Fig. 1.3.3. The voltage equation becomes

Fig. 1.3.3. Voltage follower

That is, the output voltage is equal to input voltage, both in magnitude and phase. In other words, we can also say that the output voltage follows the input voltage exactly. Hence, the circuit is called a voltage follower. The use of the unity gain circuit lies in the fact that its input impedance is very high (i.e.  $M\Omega$  order) and output impedance is zero. Therefore, it draws negligible current from the source. Thus a voltage follower may be used as buffer for impedance matching, that is, to connect a high impedance source to a low impedance load.

# **1.3.4 SUMMING AMPLIFIER**

Op-amp may be used to design a circuit whose output is the sum of several input signals. Such a circuit is called a summing amplifier or a summer. An inverting summer or a non-inverting summer may be obtained as discussed now.

**1.3.4.1** Inverting summing amplifier

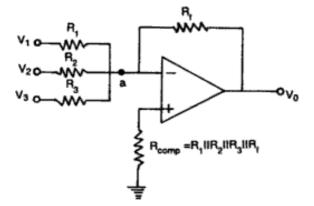

A typical summing amplifier with three input voltages V1, V2 and V3, three input resistors R1, R2, R3 and a feedback resistor Rf is shown in Fig. 1.3.4.1. The following analysis is carried out assuming that the op-amp is an ideal

one, that is,  $AOL = \Box$  and  $Ri = \Box$ . Since the input bias current is assumed to be zero, there is no voltage drop across the resistor RComp and hence the non-inverting input terminal is at ground potential.

Fig. 1.3.4.1 Inverting Summing Amplifier

The voltage at node 'a' is zero as the non-inverting input terminal is grounded. The nodal equation by KCL at node 'a' is

$$\frac{V_1}{R_1} + \frac{V_2}{R_2} + \frac{V_3}{R_3} + \frac{V_o}{R_f} = 0$$

$$V_o = -\left(\frac{R_f}{R_1}V_1 + \frac{R_f}{R_2}V_2 + \frac{R_f}{R_3}V_3\right)$$

Thus the output is an inverted, weighted sum of the inputs. In the special case, when  $R_1 = R_2 = R_3 = R_f$ , we have

$$V_{0} = -(V_{1} + V_{2} + V_{3})$$

in which case the output V<sub>0</sub>. is the inverted sum of the input signals. We may also set

$$R_1 = R_2 = R_3 = 3R_f$$

,

in which case

$$V_{\rm o} = -\left(\frac{V_1 + V_2 + V_3}{3}\right)$$

Thus the output is the average of the input signals (inverted). In a practical circuit, input bias current is compensated by using resistor Rcomp. To find Rcomp, make all inputs V1 = V2 = V3 = 0. So the effective input resistance Ri =R1IIR2IIR3.Therefore Rcomp= RiIIRf =R1IIR2IIR3IIRf.

Design an adder circuit using an op-amp to get the output expression as

$$V_{o} = -(0.1 V_1 + V_2 + 10 V_3)$$

where  $V_1$ ,  $V_2$ , and  $V_3$  are the inputs.

## Solution

The output in Fig. 4.2 (a) is

say

$$V_{o} = -[(R_{f}/R_{1}) V_{1} + (R_{f}/R_{2})V_{2} + (R_{f}/R_{3})V_{3}]$$

$$R_{f} = 10 \text{ k}\Omega, R_{1} = 100 \text{ k}\Omega, R_{2} = 10 \text{ k}\Omega, R_{3} = 1 \text{ k}\Omega$$

Then the desired output expression is obtained.

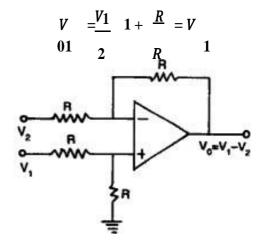

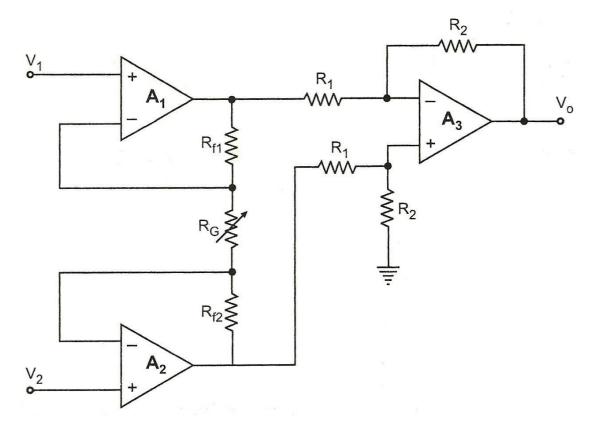

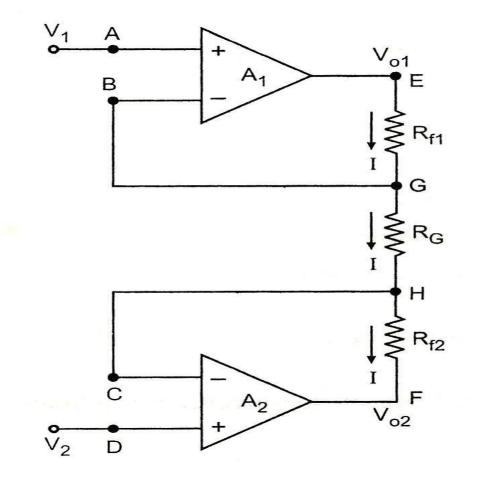

#### 1.3.4.2 Non-inverting Summing Amplifier

A summer that gives a non-inverted sum is the non-inverting summing amplifier and is shown in fig.1.3.4.2. Let the voltage at the (-) input terminal be  $V_a$ . The voltage at (+) input terminal will also be  $V_a$ . The nodal equation at node 'a' is given by

$$\frac{V_1 - V_a}{R_1} + \frac{V_2 - V_a}{R_2} + \frac{V_3 - V_a}{R_3} = 0$$

From which we have

$$V_{a} = \frac{\frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{2}} + \frac{V_{3}}{R_{3}}}{\frac{1}{R_{1}} + \frac{1}{R_{2}} + \frac{1}{R_{3}}}$$

Fig. 1.3.4.2 Non-inverting summing amplifier

The op-amp and two resistors Rf and R constitute a non-inverting amplifier with

$$V_{\rm o} = \left(1 + \frac{R_{\rm f}}{R}\right) V_{\rm a}$$

Therefore, the output voltage is

$$V_{o} = \left(1 + \frac{R_{f}}{R}\right) \frac{\left(\frac{V_{1}}{R_{1}} + \frac{V_{2}}{R_{2}} + \frac{V_{3}}{R_{3}}\right)}{\frac{1}{R_{1}} + \frac{1}{R_{2}} + \frac{1}{R_{3}}}$$

which is a non-inverted weighted sum of inputs.

Let R1 = R2 = R3 = R = Rf / 2. Then,  $V_0 = VI + V2 + V3$

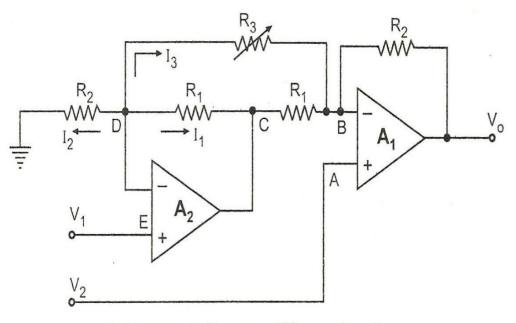

## 1.3.5 Differential Amplifier (Subtracting Amplifier)

The basic difference amplifier can be used as a subtractor or subtracting amplifier as shown in below fig.1.3.5

If all resistors are equal in value, then the output voltage can be derived by using superposition principle. To find the output V01 due to V1 alone, make V2=0. Then the circuit of fig.1.3.5 becomes a non-inverting amplifier having input voltage V1/2 at the non-inverting input terminal and the output becomes

Fig.1.3.5 Subtractor or Subtracting Op-amp

Similarly the output V02 due to V2 alone (with V1 grounded) can be written simply for an inverting amplifier as

$$V_{02} = -V_2$$

Thus the output voltage V0 due to both the inputs can be written as

$$V_0 = V_{01} + V_{02} = V_1 - V_2$$

Hence the output voltage V<sub>0</sub> is subtraction of input voltages V<sub>1</sub> and V<sub>2</sub>.

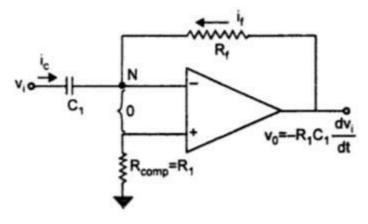

#### **1.3.6 DIFFERENTIATOR**

One of the simplest of the op-amp circuits that contain capacitor is the differentiating amplifier, or differentiator. As the name suggests, the circuit performs the mathematical operation of differentiation, that is, the output waveform is the derivative of input waveform. A differentiator circuit is shown in Fig. 1.3.6.

The node N is at virtual ground potential i.e.,  $v_N = 0$ . The current  $i_C$  through the capacitor is,

$$i_{\rm C} = C_1 \frac{d}{dt} (v_{\rm i} - v_{\rm N}) = C_1 \frac{dv_{\rm i}}{dt}$$

The current  $i_f$  through the feedback resistor is  $v_o/R_f$  and there is no current into the op-amp. Therefore, the nodal equation at node N is,

$$C_1 \frac{dv_{\rm i}}{dt} + \frac{v_{\rm o}}{R_{\rm f}} = 0$$

from which we have

$$v_0 = -R_f C_1 \frac{dv_i}{dt}$$

Fig. 1.3.6 Differentiator

Thus the output voltage  $v_0$  is a constant  $(-R_f C_1)$  times the derivative of the input voltage  $v_i$  and the circuit is a differentiator. The minus sign indicates a 180° phase shift of the output waveform  $v_0$  with respect to the input signal.

The phasor equivalent is,  $V_0(s) = -R_f C_1 s V_i(s)$  where  $V_0$ and  $V_i$  is the phasor representation of  $v_0$  and  $v_i$ . In steady state, put  $s = j\omega$ . We may now write the magnitude of gain A of the differentiator as,

. .

$$|A| = \left| \frac{V_o}{V_i} \right| = \left| -j\omega R_f C_1 \right| = \omega R_f C_1$$

one can draw the frequency response of the opamp differentiator. Equation (4.70) may be rewritten as

$$|A| = \frac{f}{f_a}$$

where  $f_a = \frac{1}{2\pi R_f C_1}$

At  $f = f_a$ , |A| = 1, i.e., 0 dB, and the gain increases at a rate of +20 dB/decade. Thus at high frequency, a differentiator may become unstable and break into oscillation. There is one more problem in the differentiator of Fig. The input impedance (i.e.,  $1/\omega C_1$ ) decreases with increase in irequency, thereby making the circuit sensitive to high frequency noise.

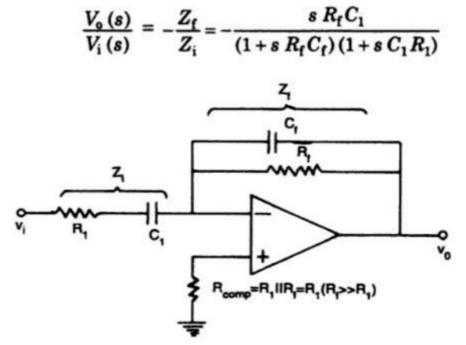

A practical differentiator of the type shown in Fig. eliminates the problem of stability and high frequency noise.

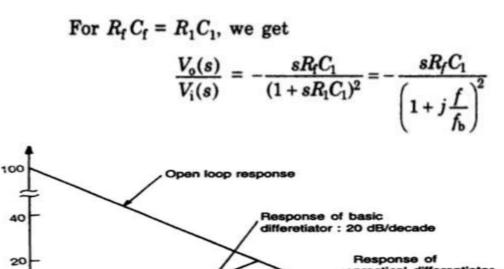

The transfer function for the circuit in Fig. is given by,

1.3.6.1 Practical DifferentiatorFig. 1.3.6.1 Practical Differentiator

Fig. 1.3.6.2 Frequency response of Differentiator

where,

$$f_{\rm b}=\frac{1}{2\pi R_{\rm l}C_{\rm l}}$$

From Eq. it is evident that the gain increases at +20 dB/ decade for frequency  $f < f_b$  and decreases at -20 dB/decade for  $f > f_b$ as shown by dashed lines in Fig. . This 40 dB/decade change in gain is caused by  $R_1 C_1$  and  $R_f C_f$  factors. For the basic differentiator of Fig. the frequency response would have increased continuously at the rate of +20 dB/decade even beyond  $f_b$  causing stability problem at high frequency. Thus the gain at high frequency is reduced significantly, thereby avoiding the high frequency noise and stability problems. The value of  $f_b$  should be selected such that,

$$f_a < f_b < f_c$$

where  $f_c$  is the unity gain-bandwidth of the op-amp in open-loop configuration.

For good differentiation, one must ensure that the time period T of the input signal is larger than or equal to  $R_{f}C_{1}$ , that is,

$$T \geq R_f C_1$$

It may be noted that for  $R_f C_1$  much greater than  $R_1 C_1$  or  $R_f C_f$ , Eq. is reduced to,  $V_o/V_i = -sR_f C_1$ , that is, the expression of the output voltage remains the same as in the case of an ideal differentiator as

$$v_{\rm o} = -R_{\rm f}C_1 \, \frac{dv_{\rm i}}{dt}$$

A resistance  $R_{comp}$  (=  $R_1 || R_f$ ) is normally connected to the (+) input terminal to compensate for the input bias circuit.

A good differentiator may be designed as per the following steps:

- 1. Choose  $f_a$  equal to the highest frequency of the input signal. Assume a practical value of  $C_1$  (< 1µF) and then calculate  $R_f$ .

- 2. Choose  $f_b = 10 f_a$  (say). Now calculate the values of  $R_1$  and  $C_f$  so that  $R_1C_1 = R_fC_f$ .

# Example

- (a) Design an op-amp differentiator that will differentiate an input signal with  $f_{max} = 100$  Hz.

- (b) Draw the output waveform for a sine wave of 1V peak at 100 Hz applied to the differentiator.

- (c) Repeat part (b) for a square wave input.

(a) select,

$$f_a = f_{max} = 100$$

Hz  $= \frac{1}{2\pi R_f C_1}$

Let  $C_1 = 0.1 \, \mu F$ ,

then

$$R_{\rm f} = \frac{1}{2\pi (10^2) (10^{-7})} = 15.9 \, \rm k\Omega$$

Now choose

$$f_{b} = 10 f_{a}$$

$$= 1 \text{ kHz}$$

$$= \frac{1}{2\pi R_{1}C_{1}}$$

Therefore,

$$R_1 = \frac{1}{2\pi (10^3) (10^{-7})} = 1.59 \text{ k}\Omega$$

Since  $R_f C_f = R_1 C_1$ , we get,  $C_f = \frac{1.59 \times 10^3 \times 10^{-7}}{15.9 \times 10^3} = 0.01 \,\mu\text{F}$

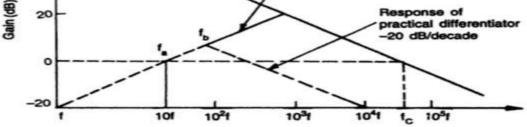

(b)

$$v_i = 1 \sin 2\pi (100)t$$

From Eq.

$v_o = -R_f C_1 \frac{dv_i}{dt}$

$= -(15.9 \text{ k}\Omega) (0.1 \mu\text{F}) \frac{d}{dt} [(1 \text{ V}) \sin (2\pi) (10^2) t]$

$= -(15.9 \text{ k}\Omega) (0.1 \mu\text{F}) (2\pi) (10^2) \cos [(2\pi) (10^2)t]$

$= -0.999 \cos [2\pi (10^2)t]$

$= -1 \cos [(2\pi) (10^2) t]$

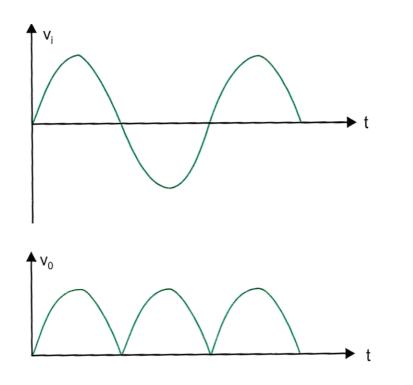

The input and output waveforms are shown in Fig. (a).

(c) For a square wave input, say 1V peak and 1 KHz, the output waveform will consist of positive and negative spikes of magnitude  $V_{sat}$  which is approximately 13V for  $\pm$  15V op-amp power supply. During the time periods for which input is constant at  $\pm$  1V, the differentiated output will be zero. However, when input transits between  $\pm$  1V levels, the slope of the input is infinite for an ideal square wave. The output, therefore, gets clipped to about  $\pm$  13V for a  $\pm$  15V op-amp power supply as shown in Fig. (b).

Fig. 1.3.6.3 (a) Sine-wave input and cosine output (b) Square wave input and spike output

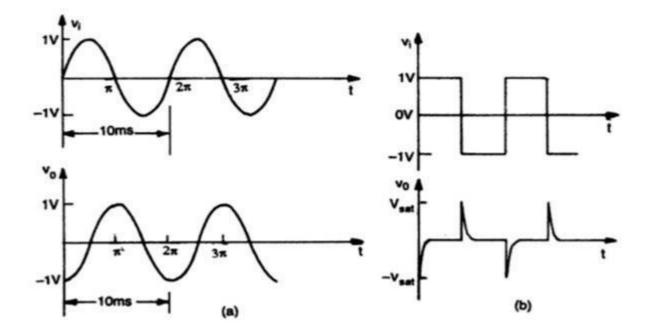

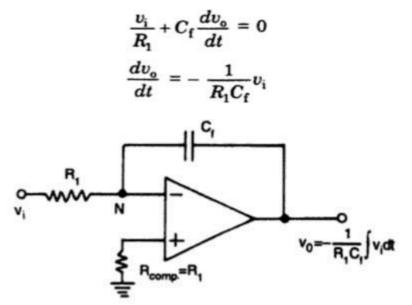

# 1.3.7 INTEGRATOR

If we interachange the resistor and capaction of the differentiator of Fig 1.3.6 (Differentiator), we have the circuit of Fig.1.3.7 which as we will see, is an integrator. The nodal equation at node N is,

Fig. 1.3.7 Integrator

Integrating both sides, we get,

$$\int_{0}^{t} dv_{0} = -\frac{1}{R_{1}C_{f}} \int_{0}^{t} v_{i} dt$$

$$v_{0}(t) = -\frac{1}{R_{1}C_{f}} \int_{0}^{t} v_{i}(t) dt + v_{0}(0)$$

where  $v_{o}(0)$  is the initial output voltage.

The circuit, thus provides an output voltage which is proportional to the time integral of the input and  $R_1C_f$  is the time constant of the integrator. It may be noted that there is a negative sign in the output voltage, and therefore, this integrator is also known as an inverting integrator. A resistance,  $R_{comp} = R_1$  is usually connected to the (+) input terminal to minimize the effect of input bias current.

The operation of the integrator can also be studied in the frequency domain. In phasor notation, Eq. can be written as

$$V_{\rm o}(s) = -\frac{1}{sR_{\rm I}C_{\rm f}}V_{\rm i}(s)$$

In steady state, put  $s = j\omega$  and we get

$$V_{o}(j\omega) = -\frac{1}{j\omega R_{I}C_{f}}V_{i}(j\omega)$$

So, the magnitude of the gain or integrator transfer function is

$$|A| = \left| \frac{V_{o}(j\omega)}{V_{i}(j\omega)} \right| = \left| -\frac{1}{j\omega R_{i}C_{f}} \right| = \frac{1}{\omega R_{i}C_{f}}$$

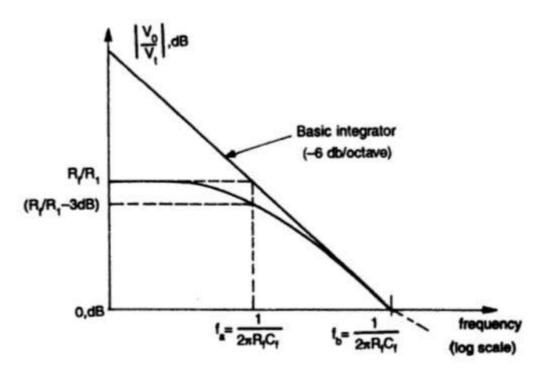

The frequency response or Bode Plot of this basic integrator is shown in the fig.1.3.7. The bode plot is a straight line of slope -6 dB/ Octave or equivalently -20 dB/Decade. The frequency *fb*, in fig.1.3.7 is the frequency at which the gain f the integrator is 0 dB and is given by

$$fb = \frac{1}{2\pi R_{-}} c_{f}$$

Fig. 1.3.7.1 Frequency response of basic and lossy integrator

As the gain of the integrator decreases with increasing frequency, the integrator circuit does not have any frequency problem as faced in a differentiator. However, at low frequencies such as at dc ( $\omega \approx 0$ ), the gain becomes infinite (or saturates). The solution to this problem is discussed in the following.

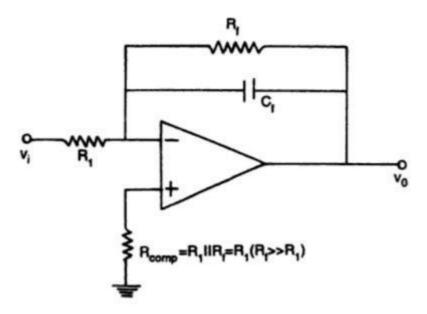

# **1.3.7.1** Practical Integrator (Lossy Integrator)

The gain of an integrator at low frequency (dc) can be limited to avoid the saturation problem if the feedback capacitor is shunted by a resistance  $R_f$  as shown in Fig. 2.15 . The parallel combination of  $R_f$ and  $C_f$  behaves like a practical capacitor which dissipates power unlike an ideal capacitor. For this reason, this circuit is also called a lossy integrator. The resistor  $R_f$  limits the low frequency gain to  $-R_f/R_1$ (generally  $R_f = 10 R_1$ ) and thus provides dc stabilization.

Fig. 1.3.7.2 Practical or lossy integrator The

nodal equation at the inverting input terminal of the op-amp of fig. 1.3.7.1 is

$$\frac{V_{i}(s)}{R_{1}} + s C_{f} V_{o}(s) + \frac{V_{o}(s)}{R_{f}} = 0$$

from which we have,

$$V_{\rm o}(s) = -\frac{1}{sR_1C_{\rm f} + R_1/R_{\rm f}} V_{\rm i}(s)$$

If  $R_f$  is large, the lossy integrator approximates the ideal integrator. For  $s = j\omega$ , magnitude of the gain of lossy integrator is given by

$$|A| = \left| \frac{V_{o}}{V_{i}} \right| = \frac{1}{\sqrt{\omega^{2} R_{1}^{2} C_{f}^{2} + R_{1}^{2} / R_{f}^{2}}} = \frac{R_{f} / R_{1}}{\sqrt{1 + (\omega R_{f} C_{f})^{2}}}$$

The bode plot of the lossy integrator is also shown in fig.1.3.7.1. At low frequencies gain is constant at Rf/R1. The break frequency (f=fa) at which the gain is 0.707 (Rf/R1) or -3dB below its value of Rf/R1) is claculated from Equation below

$$\sqrt{1 + (\omega R_f C_f)^2} = \sqrt{2}$$

Solving for  $f = f_a$ , we get

$$f_{\rm a} = \frac{1}{2\pi R_{\rm f} C_{\rm f}}$$

This is a very important frequency. It tells us where the useful integration range starts. If the input frequency is lower than  $f_a$  the circuit acts like a simple inverting amplifier and no integration results. At input frequency equal to  $f_a$ , 50% accuracy results. The practical thumb rule is that if the input frequency is 10 times  $f_a$ , than 99% accuracy can result.

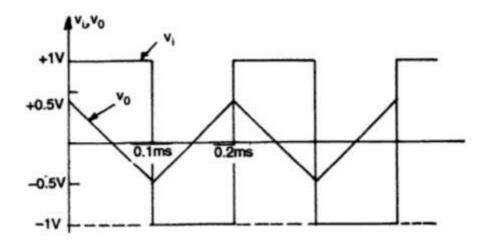

**1.3.7.2** Input and output waveforms

Fig. 1.3.7.3 Input and output waveforms integrator

## 1.3.8 LOGARITHMIC (LOG) AMPLIFIERS

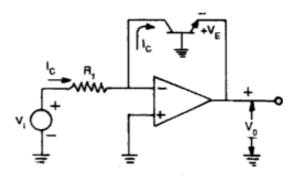

Log-amp can also be used to compress the dynamic range of a signal. The fundamental log-amp circuit is shown in Fig. 1.3.8 where a grounded base transistor is placed in the feedback path.

Fig. 1.3.8 Log amplifier

Since the collector is held at virtual ground and the base is also grounded, the transistor's voltage-current relationship becomes that of a diode and is given by

$$I_{\rm E} = I_{\rm s} \left( e^{qV_{\rm E}/kT} - 1 \right)$$

Since, IC=IE for a grounded base transistor

$$I_{\rm C} = I_{\rm s} \left( e^{qV_{\rm E}/kT} - 1 \right)$$

$I_S$  = emitter saturation current  $-10^{-13}$  A

*k* = Boltzmann's Constant

T =absolute temperature (in  $^{0}$ K)

Therefore,

$$\frac{I_{\rm C}}{I_{\rm s}} = (e^{q \, V_{\rm E}/kT} - 1)$$

$$e^{q \, V_{\rm E}/kT} = \frac{I_{\rm C}}{I_{\rm s}} + 1$$

$$= \frac{I_{\rm C}}{I_{\rm s}} \qquad [\text{as } I_{\rm s} = 10^{-13} \text{ A, } I_{\rm C} >> I_{\rm s}]$$

Taking natural log on both sides, we get

$$V_{\rm E} = \frac{kT}{q} \ln\left(\frac{I_{\rm C}}{I_{\rm s}}\right)$$

Also in Fig. 1.3.8,

$$I_{\rm C} = \frac{V_{\rm I}}{R_{\rm I}}$$

$$V_{\rm E} = -V_{\rm o}$$

$$V_{\rm o} = -\frac{kT}{q} \ln\left(\frac{V_{\rm i}}{R_{\rm I}I_{\rm s}}\right) = -\frac{kT}{q} \ln\left(\frac{V_{\rm i}}{V_{\rm ref}}\right)$$

$$V_{\rm ref} = R_{\rm I}I_{\rm s}$$

v

The output voltage is thus proportional to the logarithm of input voltage. Although the circuit gives natural log(In), one can find log10 by proper scaling

#### $\log 10 X = 0.4343 In X$

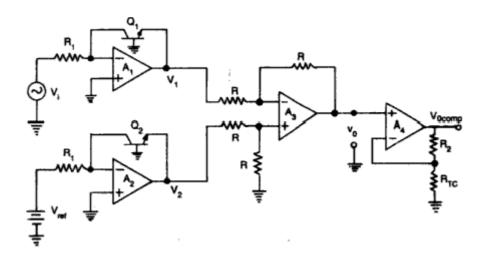

The circuit however has one problem. The emitter saturation current  $I_s$ , varies from transistor to transistor and with temperature. Thus a stable reference voltage  $V_{ref}$  cannot be obtained. This is eliminated by the circuit given in Fig. 1.3.8.1. The input is applied to one log-amp, while a reference voltage is applied to another log.amp. The two transistors are integrated close together in the same silicon wafer. This provides a close match of saturation currents and ensures good thermal tracking.

Fig.1.3.8.1. Log-amp with saturation current and temperature compensation

Assume,

$$I_{g1} = I_{g2} = I_{g}$$

$$V_{1} = -\frac{kT}{q} \ln\left(\frac{V_{i}}{R_{i}I_{s}}\right)$$

$$V_{2} = -\frac{kT}{q} \ln\left(\frac{V_{ref}}{R_{i}I_{s}}\right)$$

$$V_{o} = V_{2} - V_{1} = \frac{kT}{q} \left[\ln\left(\frac{V_{i}}{R_{i}I_{s}}\right) - \ln\left(\frac{V_{ref}}{R_{i}I_{s}}\right)\right]$$

$$V_{o} = \frac{kT}{q} \ln\left(\frac{V_{i}}{V_{ref}}\right)$$

The voltage V0 is still dependent upon temperature and is directly proportional to T. This is compensated by the last op-amp stage A4 which provides a non-inverting gain of (1 + R2/RTC). Now, the output voltage is,

$$V_{\rm o \ comp} = \left(1 + \frac{R_2}{R_{\rm TC}}\right) \frac{kT}{q} \ln\left(\frac{V_{\rm i}}{V_{\rm ref}}\right)$$

where RTC is a temperature-sensitive resistance with a positive coefficient of temperature, so that the slope of the equation becomes constant as the temperature changes.

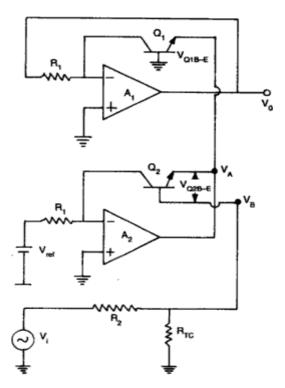

Fig. 1.3.8.2 Log-amp using two op-amps only

The circuit in Fig. 1.3.8.1 requires four op-amps, and becomes expensive if FET op-amps are used for precision. The same output can be obtained by the circuit of Fig. 1.3.8.2 using two op-amps only.

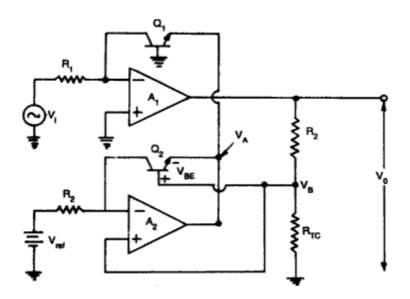

# 1.3.9 ANTILOG AMPLIFIER

The circuit is shown in Fig. 1.3.9. The input V<sub>1</sub> for the antilog-amp is fed into the temperature compensating voltage divider R2 and RTC and then to the base of Q2. The output V<sub>0</sub> of the antilog-amp is fed back to the inverting input of A1 through the resistor R1. The base to emitter voltage of transistors Q1 and Q2 can be written as

$$V_{\text{Q1 B-E}} = \frac{kT}{q} \ln\left(\frac{V_{\text{o}}}{R_{\text{i}}I_{s}}\right)$$

$$V_{\text{Q2 B-E}} = \frac{kT}{q} \ln\left(\frac{V_{\text{ref}}}{R_{\text{i}}I_{s}}\right)$$

Since the base of Q1 is tied to ground, we get

$$V_{\rm A} = -V_{\rm Q1 \ B-E} = -\frac{kT}{q} \ln\left(\frac{V_{\rm o}}{R_{\rm i}I_{\rm s}}\right)$$

The base voltage VB of Q2 is

$$V_{\rm B} = \left(\frac{R_{\rm TC}}{R_2 + R_{\rm TC}}\right) V_{\rm i}$$

The voltage at the emitter of Q2 is

$$V_{Q2 E} = V_{B} + V_{Q2 E-B}$$

$$V_{Q2 E} = \left(\frac{R_{TC}}{R_{2} + R_{TC}}\right) V_{i} - \frac{kT}{q} \ln\left(\frac{V_{ref}}{R_{i}I_{s}}\right)$$

Fig. 1.3.9 Antilog amplifier

But the emitter voltage of Q2 is VA, that is

$$V_{A} = V_{Q2 E}$$

$$-\frac{kT}{q} \ln \frac{V_{0}}{R_{I}I_{s}} = \frac{R_{TC}}{R_{2} + R_{TC}} V_{i} - \frac{kT}{q} \ln \frac{V_{ref}}{R_{I}I_{s}}$$

$$\frac{R_{TC}}{R_{2} + R_{TC}} V_{i} = -\frac{kT}{q} \left( \ln \frac{V_{0}}{R_{I}I_{s}} - \ln \frac{V_{ref}}{R_{I}I_{s}} \right)$$

$$-\frac{q}{kT} \frac{R_{TC}}{R_{2} + R_{TC}} V_{i} = \ln \left( \frac{V_{0}}{V_{ref}} \right)$$

Changing natural log, i.e., in to log10 , we get

$$-0.4343 \left(\frac{q}{kT}\right) \left(\frac{R_{\rm TC}}{R_2 + R_{\rm TC}}\right) V_{\rm i} = 0.4343 \times \ln\left(\frac{V_0}{V_{\rm ref}}\right)$$

$$-K'V_{\rm i} = \log_{10}\left(\frac{V_0}{V_{\rm ref}}\right)$$

$$\frac{V_0}{V_{\rm ref}} = 10^{-K'V_{\rm i}}$$

$$V_0 = V_{\rm ref} (10^{-K'V_{\rm i}})$$

$$\frac{33}{5}$$

$$\mathbf{K}' = \mathbf{0.4343} \quad \frac{q}{kT} \quad \frac{RTC}{R2 + RTC}$$

Hence an increase of input by one volt causes the output to decrease by a decade. The IC755 log/antilog amplifier IC chip is available as a functional module which may require some external components also to be connected to it.

#### **1.4 OP-AMP USED AS COMPARATORS**

## **1.4.1 COMPARATOR**

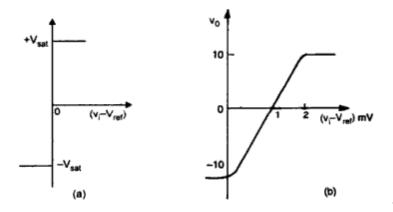

A comparator is a circuit which compares a signal voltage applied at one input of an op-amp with a known reference voltage at the other input. It is basically an open-loop op-amp with output  $\pm V_{sat}$  (=V<sub>cc</sub>) as shown in the ideal transfer characteristics of Fig. 1.4.1(a). However, a commercial op-amp has the transfer characteristics of Fig. 1.4.1(b).

Fig. 1.4.1 The transfer characteristics (a) ideal comparator. (b) Practical comparator There are basically two types of comparators:

Non-inverting comparator

**Inverting comparator**

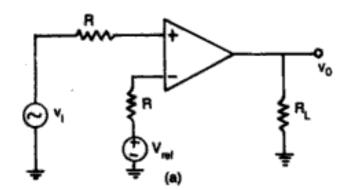

The circuit of Fig. 1.4.1.1(a) is called a non-inverting comparator. A fixed reference voltage V<sub>ref</sub> applied to (-) input and a time varying signal V<sub>i</sub> is applied to (+) input. The output voltage is at -V<sub>sat</sub> for V<sub>i</sub><V<sub>ref</sub> and V<sub>0</sub> goes to +V<sub>sat</sub> for V<sub>i</sub>>V<sub>ref</sub>. The output waveform for a Sinusoidal input signal applied to the (+) input is shown in Fig. 1.4.1.1 (b and c) for positive and negative V<sub>ref</sub> respectively.

Fig. 1.4.1.1(a) Comparator

Fig. 1.4.1.1. Input and output of a Comparator when (a)Vref>0 V (b) Vref< 0V

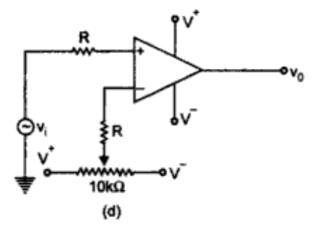

In a practical circuit  $V_{ref}$  is obtained by using a  $10K\Omega$  potentiometer which forms a voltage divider with the supply voltages V+ and V- with the wiper connected to (-) input terminal as shown in Fig. 1.7.4.1 (d). Thus a Vref of desired amplitude and polarity can be obtained by simply adjusting the  $10K\Omega$  potentiometer.

## Fig. 1.7.1.1 (d) Non-inverting comparator. Input and output waveforms for (b) Vref

#### Positive (c) Vref negative (d) Practical non-inverting comparator

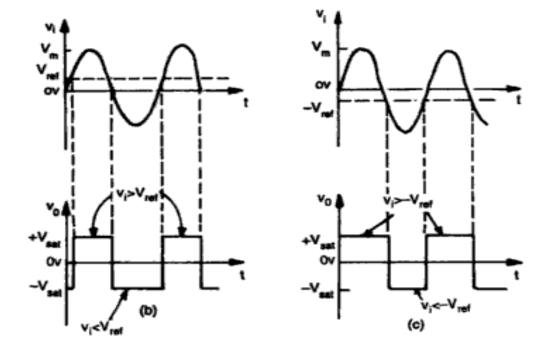

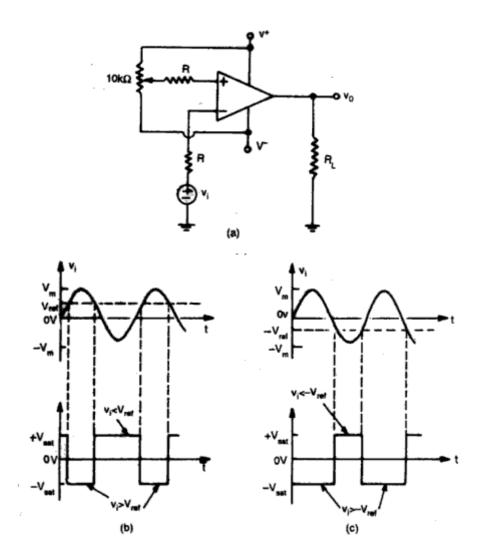

Figure 1.7.1.2(a) shows a practical inverting comparator in which the reference voltage Vref is applied to (+) input and vi is applied to (-) input. For a sinusoidal input signal, the output waveform is shown in Fig. 1.7.1.2(b) and (c) for Vref positive and negative respectively.

Fig. 1.7.1.2.(a) Inverting comparator. Input and output waveforms for (b) Vref Positive (c) Vref negative

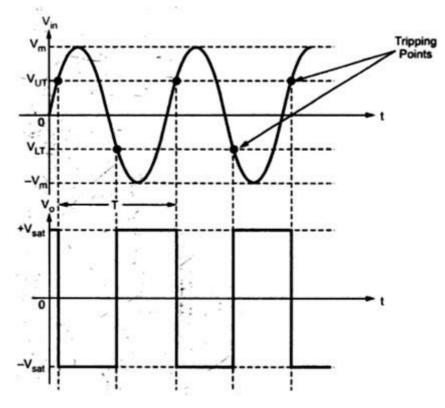

# 1.7.2 REGENERATIVE COMPARATOR (SCHMITT TRIGGER)

We have seen that in a basic comparator, a feedback is not used the op-amp is used in the open loop mode. As open loop gain of op-amp is very large, very small noise voltages also can cause triggering of the comparator, to change its state. Such a false triggering may cause lot of problems in the applications of comparator as zero- crossing detector. This may give a wrong indication of zero-crossing due to zero-crossing of noise voltage rather than zero crossing of input wanted signals. Such unwanted noise causes the output to jump between high and low states. The comparator circuit used to avoid such unwanted triggering is called *regenerative comparator or Schmitt trigger*, which basically uses a positive feedback.

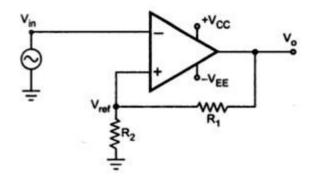

The figure 1.4.2 shows the basic Schmitt trigger circuit. As the input is applied to the inverting terminal, it is also called inverting Schmitt trigger circuit. The inverting mode produces opposite polarity output. This is fed-back to the non-inverting input which is of same polarity as that of the output. This ensures a positive feedback.

Figure 1.4.2 Schmitt trigger using op amp.(Inverting)

The fig.1.4.2 shows the basic inverting Schmitt trigger circuit.

- As the input is applied to the inverting terminal, it is also called inverting Schmitt trigger circuit.

- The inverting mode produces opposite polarity output (180 🗆 phase shift)

- This is fed-back to the non-inverting input which is of same polarity as that of output.

- This ensures positive feedback.

Case 1: When V<sub>in</sub> is slightly positive than V<sub>ref</sub>, the output is driven into negative saturation at  $-V_{sat}$  level. Case 2: When V<sub>in</sub> is slightly negative than V<sub>ref</sub>, the output is driven into positive saturation at  $+V_{sat}$  level. Thus the output voltage is always at  $+V_{sat}$  or  $-V_{sat}$  but the voltage at which it changes its state now can be controlled by the resistance R1 and R2. Thus V<sub>ref</sub> can be obtained as per requirement.

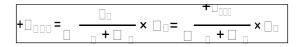

Now R1 and R2 forms a potential divider and we can write,

Positive saturation

Negative saturation

+ Vref is for positive saturation when V0 = + Vsat and is called as upper threshold voltage denoted as VUT

-Vref is for positive saturation when V0 = -Vsat and is called as lower threshold voltage denoted as VLT

The values of these voltages can be determined and adjusted by selecting proper values of R1 and R2. Thus

| —Vur= | +V <sub>sat</sub> R <sub>2</sub>              |

|-------|-----------------------------------------------|

|       | <b>R</b> <sub>1</sub> + <b>R</b> <sub>2</sub> |

and

| -V <sub>LT</sub> = | -V <sub>sat</sub> R <sub>2</sub>              |

|--------------------|-----------------------------------------------|

|                    | <b>R</b> <sub>1</sub> + <b>R</b> <sub>2</sub> |

The output voltage remaains in a given state until the input voltage exceed the threshold volage level either postive or negative.

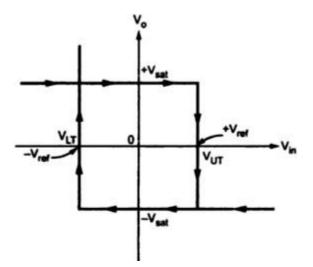

The fig.1.4.2.1 shows the graph of output voltage against input voltage. This is called transfer characteristics of Schmitt trigger.

The graph indicated that once the output changes its state it remains there indefinitely until the input voltage crosses any of the threshold voltage levels. This is called hysteresis of Schmitt trigger. The hysteresis is also called as dead- zone or dead-band.

Fig. 1.4.2.1 Hysteresis of Schmitt trigger.

The difference between VUT and VLT is called width of the hysteresis denoted as H.

$$H = V_{UT} - V_{LT}$$

$$H = \frac{+V_{sat}R_2}{R_{1+}R_2} - \frac{-V_{sat}R_2}{R_{1+}R_2}$$

$$H = \frac{2V_{sat}R_2}{R_{1+}R_2}$$

The schmitt trigger eliminates the effect of noise voltages less than the hysterisis H, cannot cause triggering. As for postive Vin greater than VUT, the output becomes –Vsat and for negative Vin less than VLT, the output becomes +Vsat, this is called *inverting schmitt trigger*.

In short,

$$V_{in} < V_{LT}, V_0 = +V_{sat}$$

$V_{in} > V_{UT}, V_0 = -V_{sat}$

# V<sub>LT</sub>< V<sub>in</sub>< V<sub>UT</sub>, V<sub>o</sub>= Previous state a chieved

If input applied is purely sinusoidal, the input and output waveforms for inverting Schmitt trigger can be shown as in fig.1.4.2.2.

Fig. 1.4.2.2 Input and output waveforms of Schmitt trigger

## **Text Book References:**

- 1. Ramakant A.Gayakwad, "0P-AMP and Linear ICs", 4th Edition, Prentice Hall / Pearson Education, 1994.

- 2. D.Roy Choudary, Shail Jain, "Linear Integrated Circuits", New Age International Pvt. Ltd., 2000.

- 3. Grey and Meyer, "Analysis and Design of Analog Integrated Circuits, 4th Edition, Wiley International, 2001.

- 4. Michael Jacob, "Applications and Design with Analog Integrated Circuits, 2nd Edition, Prentice Hall of India, 1993.

- 5. S. Salivahanan, V.S. Kanchana Bhaaskaran, "Linear integrated circuits", 3rd Edition, McGraw-Hill, 2011.

- 6. William D.StaneIy, "Operational Amplifiers with Linear Integrated Circuits", 4th Edition, Pearson Education, 2004.

# SCHOOL OF ELECTRICAL AND ELECTRONICS

DEPARTMENT OF ELECTRONICS AND COMMMUNICATION ENGINEERING

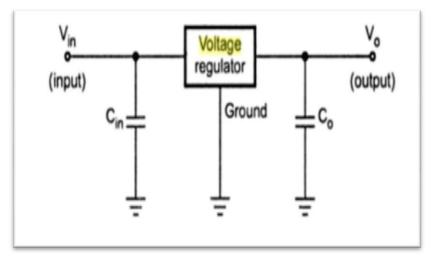

ANALOG INTEGRATED CIRCUITS - SEC1302 UNIT-II FILTERS AND OSCILLATORS

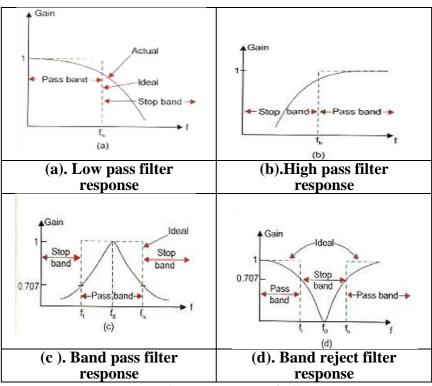

## **2.1** ACTIVE FILTERS

FILTERS are circuits used for select signal components of required frequencies and reject other unwanted frequency components. Thus selectivity is one of the main criteria for a filter circuit in communication engineering.

These filters are actually allowing the required frequency bands and attenuate the unwanted frequency bands but they are not adaptive and precise. The allowing band is termed as pass band and attenuating band is termed as stop band. The output gain of the filters in pass band is high and that in stop band is very low (negligible). For ideal filters, pass band gain is infinite and stop band gain is zero. The frequency that acts as a barrier between stop and pass band is termed as cut-off frequency. The design of a filter is based particularly on this cut-off frequency. It is found that the practical value of the cut-off frequency is 3dB less than the maximum frequency allowed.

These filters are considered to be passive when passive components like resistors, capacitors and inductors are used in constructing the circuits. Passive filters are the basic filters used in communication engineering but they are not adaptive and precise. For a good filter, the slope of frequency response plot from pass band to stop band or vice versa should be high. But passive filters sometimes have very low slope for changing input signals and other factors. Even in pass band the gain is not constant but varies. These problems are minimized by using active filters which are adaptive (manage the gain to be constant throughout the pass band and slope to be very high for even a major change in input signals).

Active filters use OP AMP to be adaptive in nature with lager controllable gain value.

- Advantages of active filters over passive filters:

- **1.** Reduced size and weight

- **2.** Increased reliability and improved performance

- 3. Simple design and good voltage gain

- 4. When fabricated in larger quantities, cheaper than passive filters

**Disadvantages of Active Filters:**

- **1.** Limited bandwidth only.

- **2.** Quality factor is also limited

- **3.** Require power supply (passive doesn't require power supply)

2

4. Changes due to environmental factors.

Possible question: What is an active filter? What are its advantages over passive filters?

### **2.1.1** Order of Butterworth filters

Butterworth filters were designed by a British engineer Stephen Butterworth as a maximally flat-response filter. This filter minimizes ripples and manages to maintain a flat response in pass band.

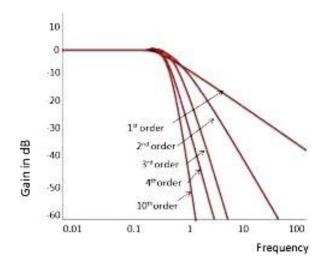

Order of a filter is the magnitude of voltage transfer function of a filter that decreases by -(20\*n)dB/decade as the order "n' increases in stop band and flat in pass band. This is shown in the fig. 2.1.

Fig. 2.1. Filter Responses of all types.

For example, if the order is 50, then the filter response in stop band decreases by -100 dB/decade. So if order increases

**1.** The magnitude of voltage transfer function in stop band is very high and slope decreases by 20 db/decade.

**2.** but the circuit complexity increases.

Fig.2.1.1. A Sample Butterworth Filter Response - Order wise

Note: Butterworth filters have flat response in pass bands and decrease in response of -20dB /per decade in pass bands.

Possible question: Write short notes on the order of Butterworth filters.

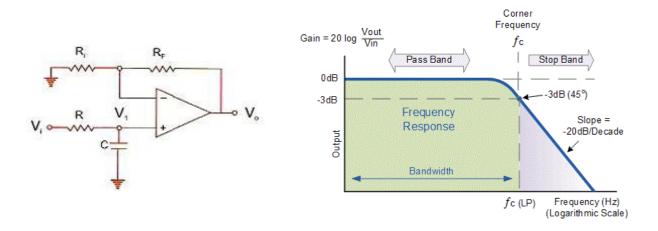

## 2.1.1.1. Low Pass Filters

A low pass filter allows low frequencies upto a corner frequency (cut-off frequency) and attenuates (stops) high frequencies above cut-off frequency. This is shown in the frequency response fig. 2.1.1.1.b.

The circuit is a simple non-inverting amplifier, where a RC low pass filter circuit is connected to the input. Capacitor allows high frequencies through it and blocks low frequencies. This characteristic of capacitor is used in these filters.

(a). Filter Circuit (b). Filter Response

Therefore,

$$H(s) = \frac{V_{o}(s)}{V_{i}(s)} = \frac{A_{o}}{\frac{s}{\omega_{h}} + 1} = \frac{A_{o}\omega_{h}}{s + \omega_{h}}$$

$f_{\rm h}$

This is the standard form of the transfer function of a first order low pass system To determine the frequency response, put  $s = j\omega$  in Eq. (7.8). Therefore, we get

$$H(j\omega) = \frac{A_o}{1+j\omega RC} = \frac{A_o}{1+j(f/f_h)}$$

where

$$= \frac{1}{2\pi RC}$$

and  $f = \frac{\omega}{2\pi}$

$|H(j\omega)| \simeq A_{o}$

At very low frequency, i.e.  $f \ll f_h$

$\mathbf{At}$

$$\left|H\left(j\omega\right)\right| = \frac{A_{\rm o}}{\sqrt{2}} = 0.707 A_{\rm o}$$

At very high frequency i.e.  $f >> f_h$

$$|H(j\omega)| \ll A_0 \simeq 0$$

$f = f_{\rm h}$ ,

The voltage  $V_1$  across the capacitor C in the s-domain is

$$V_1(s) = \frac{\frac{1}{sC}}{R + \frac{1}{sC}} V_i(s)$$

So,  $\frac{V_1(s)}{V_i(s)} = \frac{1}{RCs+1}$

where V(s) is the Laplace transform of v in time domain. The closed loop gain  $A_o$  of the op-amp is,

$$A_{\rm o} = \frac{V_{\rm o}(s)}{V_{\rm 1}(s)} = \left(1 + \frac{R_{\rm F}}{R_{\rm i}}\right)$$

So, the overall transfer function from Eqs. (7.4) and (7.5) is

$$H(s) = \frac{V_{0}(s)}{V_{1}(s)} = \frac{V_{0}(s)}{V_{1}(s)} \cdot \frac{V_{1}(s)}{V_{1}(s)} = \frac{A_{0}}{RCs + 1}$$

Let

$\omega_{\rm h} = \frac{1}{RC}$

5

Therefore,

$$H(s) = \frac{V_o(s)}{V_i(s)} = \frac{A_o}{\frac{s}{\omega_h} + 1} = \frac{A_o \omega_h}{s + \omega_h}$$

This is the standard form of the transfer function of a first order low pass system To determine the frequency response, put  $s = j\omega$  in Eq. (7.8). Therefore, we get

$$H(j\omega) = \frac{A_{o}}{1+j\omega RC} = \frac{A_{o}}{1+j(f/f_{h})}$$

$|H(j\omega)| \simeq A_{o}$

where

$$f_{\rm h} = \frac{1}{2\pi RC}$$

and  $f = \frac{\omega}{2\pi}$

At very low frequency, i.e.  $f \ll f_h$

At

$$\left|H\left(j\omega\right)\right| = \frac{A_{\rm o}}{\sqrt{2}} = 0.707 A_{\rm o}$$

$f = f_{\rm h}$ ,

At very high frequency i.e.  $f >> f_h$

$\left| H\left( j\omega\right) \right| << A_{0} \simeq 0$

Here resistor R, smoothens the input signal and the capacitor C allows higher frequencies to reach the ground. Thus high frequency signals never reach the input terminal and only low frequency signal reaches the input terminal.

How corner frequency is obtained?

In the response fig. 2.1.1.1.b., a frequency is noted where the response curve point meets a -3dB line drawn below the maximum gain. The frequency is considered as *corner frequency* ( $f_c$ ) above which the filter attenuates the input signal and below which it allows the signal.

As shown in the fig. 2.1.1.1.b response -20 dB/decade slope is obtained.

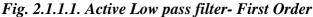

## Second order Low pass filter and its response c). Filter Circuit

(d). Frequency response

Fig. 2.1.1.1.c & d: Second Order Active Low Pass Filter

With first order circuit, another RC circuit is added as shown in the fig. 2.1.1.1.c and the response is shown in fig. 2.1.1.1.d for second order LPF with a slope of -40 dB/ decade. This is due to the fact that each RC network introduces -20dB decrease in stop band response slope.

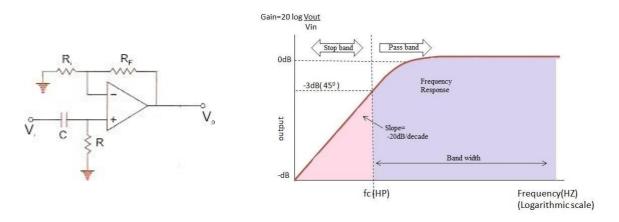

## 2.1.1.2. High Pass Filters

A high pass filter attenuates low frequencies below corner frequency (cut-off frequency) and allows high frequencies above cut-off frequency. This is shown in the frequency response fig. 2.1.1.2.b.

The circuit is a simple non-inverting amplifier, where a RC low pass filter circuit is connected to the input.

(a). Filter Circuit

(b). Frequency response

Fig. 2.1.1.2. First Order Active High Pass Filter

As shown in the above fig. 2.1.1.2.(a)., Capacitor C blocks low frequency signals below the corner frequency f<sub>c</sub> as shown in fig. 2.1.1.2.(b). The response curve increases 20 dB per decade at low frequencies below corner frequencies.

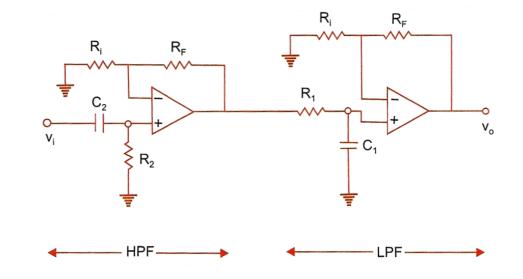

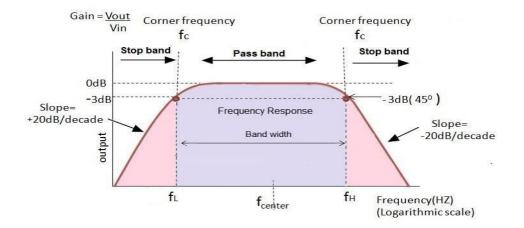

### 2.1.1.3. Band Pass Filters

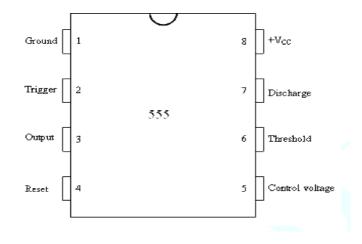

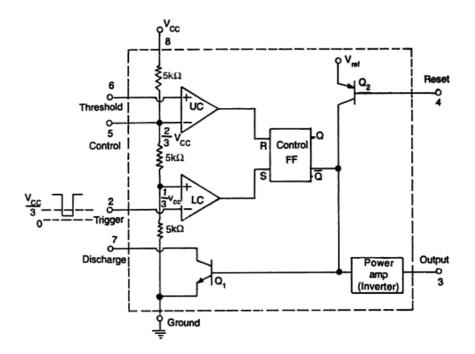

A Band pass filter allows a band of frequencies and blocks lower and higher frequencies other than the allowed band as shown in fig. 2.1.1.3.b. As shown in the fig. 2.1.1.3.a, high pass and low pass filters are connected in series.

Fig. 2.1.1.3. a. Active Band Pass Filter

The corner frequency of low pass filter  $f_L$  is chosen to be lower than that of high pass filter  $f_H$ . Thus the difference between  $f_H$  and  $f_L$  is considered to be the pass band. In low frequency stop band, the response increases 20 dB per decade and in high frequency stop band, the response decreases by 20 dB per decade.

Fig. 2.1.1.3.b. Response of Active Band Pass Filter

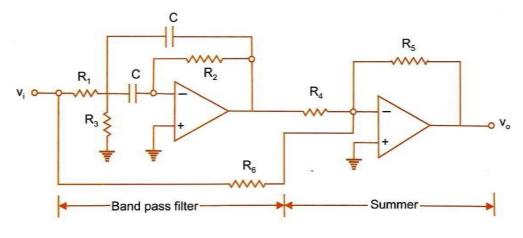

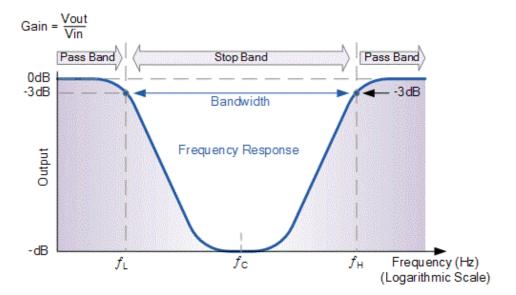

## **2.1.1.4.** Band Reject Filters (Notch filter)

A Band pass filter blocks a band of frequencies and allows lower and higher frequencies other than the blocked band as shown in fig. 2.1.1.4.b. As shown in the fig. 2.1.1.4.a, band pass filter is connected to a summer circuit. The input and output of the band pass filter is summed up at the inverting summer input. The bands are inverted by the inverting summer and so pass band of band pass filter becomes stop band and stop bands becomes pass bands. Thus this filter only allows particular band above lower corner frequency  $f_L$  and below upper corner frequency

f<sub>H</sub>.

Fig. 2.1.1.4.a. Active Band Reject Filter

Fig. 2.1.1.4.b. Response of Active Band Reject Filter

## **Possible questions:**

Write briefly about first and second order Butterworth Low-pass filter with neat sketches. Write briefly about first and second order Butterworth high-pass filter with neat sketches. Write briefly about first order Butterworth band-pass filter with neat sketches. Write briefly about first order Butterworth band-reject filter with neat sketches. . Write briefly about Notch filter with neat sketches.

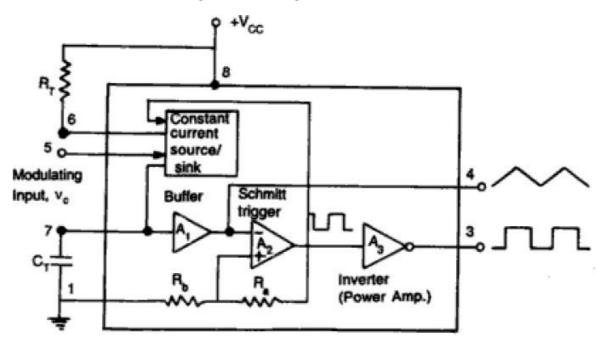

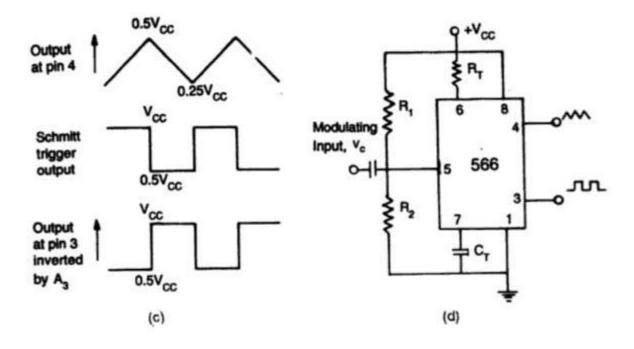

# **2.2** OP-AMP OSCILLATORS

In electronics, oscillators are circuits that generate sinusoidal or non-sinusoidal waveforms used as reference signals in communication engineering. The non-sinusoidal waveforms are triangular, ramp, saw-tooth, pulse, TTL, rectangular, spike etc.

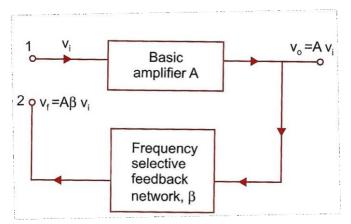

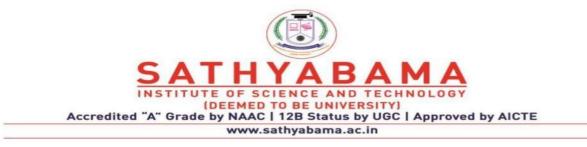

The oscillator shall have an amplifier with a positive feedback for generating oscillations. The basic oscillator circuit with feedback is shown below fig. 2.2.a.

Fig.2.2.a. Basic Feedback Oscillator

Fig.2.2.b. Feedback Oscillator Output

But for sustained (continuous and steady) oscillations Barkhausen's criteria are to be satisfied. The criteria states that **1.** The total gain of the circuit should be equal to or more than one and

**2.** The overall phase shift in the circuit (amplifier and feedback circuit) shall be

zero. If gain of the amplifier is considered as A and feedback factor is  $\beta$ , then

Criterion 1: $\Box A \beta \Box \Box 1$

Modulus of the product of the amplifier gain A and feedback factor of feedback network  $\beta$  should be equal to or greater than zero.

Criterion 2:  $\Box A \beta = 0^{\circ} \text{ or } 360^{\circ} (0 \text{ or } 2 \Box \text{ radians})$

Phase angle between the amplifier gain A and feedback factor of feedback network  $\beta$  or total phase shift in the circuit should be equal to or greater than zero. Criterion 1 and 2 are *Barkhausen's criteria for sustained oscillations*.

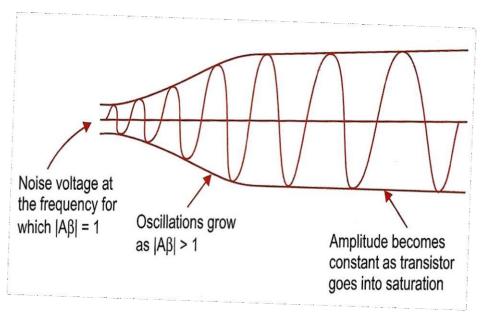

As shown in fig. 2.2.b, a noise voltage introduced by existing imbalances in the circuit is amplified by the circuit itself. The frequency of noise voltage depends on the design aspects of the circuit and when multiplication factor of total gain  $\Box A \beta \Box = 1$  and when  $\Box A \beta \Box \Box 1$ , the amplitude of the generated voltage increases till saturation is reached. Then the oscillation at the particular frequency is generated and sustained. This is done when the phase shift of the circuit is 0° or 360° (0 or 2 $\Box$  radians).

In the following sections two such sinusoidal oscillators are being explained. They

are (1). RC phase shift oscillator and

(2). Wien Bridge oscillator

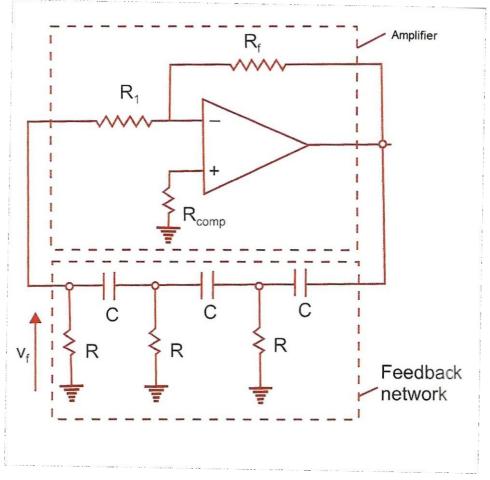

### 2.2.1. RC Phase Shift Oscillators

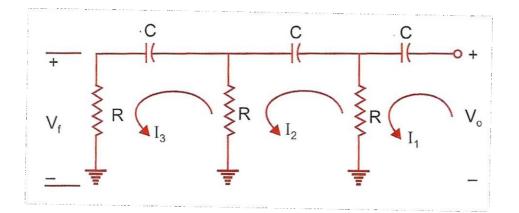

RC phase shift oscillator generates sinusoidal output and thus categorized under sinusoidal oscillators. Here in this oscillator the amplifier used is a negative feedback inverting Operational amplifier connected to a RC feedback network.

Fig.2.2.1.a. RC Phase Shift Oscillator

Construction: As described earlier the oscillator comprising of a negative feedback inverting operational amplifier whose input resistor is R1 and feedback resistor is R2 as shown in the fig. 2.2.1.a.

An RC network where one end of the resistor R is connected to the ground, the other end is connected to a capacitor C and the other end of the capacitor acts as an input terminal. The combined end of the capacitor and resistor acts as output terminal. Each RC network provides  $60^{\circ}$  ( $\Box/3$  radians) phase shift between their input and output terminals. Thus three networks are connected in series, so as to provide a phase shift of  $180^{\circ}$  or  $\Box$  radians. The feedback RC network shifts the phase this is termed as RC phase shift oscillator. As said earlier the amplifier is an inverting amplifier, and so  $180^{\circ}$  or  $\Box$  radians phase shift between input and output. Hence second Barkhausen's criterion is fulfilled.

Choosing the value of amplifier voltage gain to be more (nearly 30 or so), we can fulfill first Barkhausen's criterion of having overall gain more than 1.

Working: Practically an OP AMP is not perfect and so imbalances are prevailing between their input terminals. This imbalance generates a minor sinusoidal noise voltages fed between the input terminals. This noise voltage is amplified by the amplifier and a sinusoidal output voltage  $V_0$  is generated at the output terminal.

As discussed earlier, the RC network provides  $180^{\circ}$  or  $2\Box$  radians where  $V_0$  is fed into the feedback RC network and an inverse voltage of  $V_f$  shown in fig. 2.2.1.b. We can understand that  $V_f$  is  $180^{\circ}$  (or  $2\Box$  radians) phase shifted  $V_0$ . This  $V_f$  is fed into the inverting terminal of the operational amplifier through an input resistor R1. This voltage is phase inverted of  $180^{\circ}$  (or  $2\Box$  radians) by the amplifier and the output  $V_0$  is inverse of  $V_f$ .

Since the circuit fulfills the criteria for sustained oscillations, the circuit continuously generates sinusoidal output.

Fig.2.2.1.b. RC Phase Shift Oscillator- Feedback network

# Derivation of frequency of oscillation of RC Phase shift oscillator

Fig. 2.13

Applying KVL to various loops we get,

$$I_1\left(R + \frac{1}{j\omega C}\right) - I_2 R = V_i \qquad \dots (15)$$

$$-I_1 R + I_2 \left(2R + \frac{1}{j\omega C}\right) - I_3 R = 0 \qquad ... (16)$$

$$0 - I_2 R + I_3 \left( 2R + \frac{1}{j\omega C} \right) = 0 \qquad ... (17)$$

Replacing  $j\omega$  by s and writing the equations in the matrix form,

$$\begin{array}{c|cccc} R + \frac{1}{sC} & -R & 0 \\ -R & 2R + \frac{1}{sC} & -R \\ 0 & -R & 2R + \frac{1}{sC} \end{array} \begin{vmatrix} I_1 \\ I_2 \\ I_3 \end{vmatrix} = \begin{bmatrix} V_i \\ 0 \\ 0 \end{bmatrix} \qquad \dots (18)$$

Using the Crammer's rule to obtain I<sub>3</sub>

$$D = \begin{vmatrix} \frac{1+sRC}{sC} & -R & 0\\ -R & \frac{1+2sRC}{sC} & -R\\ 0 & -R & \frac{1+2sRC}{sC} \end{vmatrix}$$

$$= \frac{(1+sRC)(1+2sRC)^2}{s^3 C^3} - \frac{R^2(1+2sRC)}{sC} - \frac{R^2(1+sRC)}{sC}$$

$$= \frac{(1+sRC)(1+4sRC+4s^2 C^2 R^2) - R^2 s^2 C^2 [1+2sRC+1+sRC]}{s^3 C^3}$$

$$= \frac{1+5sRC+8s^2 C^2 R^2 + 4s^3 C^3 R^3 - 3s^3 R^3 C^3 - 2R^2 s^2 C^2}{s^3 C^3}$$

$$= \frac{1+5sRC+6s^2 C^2 R^2 + s^3 C^3 R^3}{s^3 C^3} \qquad \dots (19)$$

$$D_3 = \begin{vmatrix} \frac{1+sRC}{sC} & -R & V_i \\ -R & \frac{1+2sRC}{sC} & 0 \\ 0 & -R & 0 \end{vmatrix}$$

$$= V_i R^2 \qquad \dots (20)$$

$$I_3 = \frac{D_3}{D} = \frac{V_i R^2 s^3 C^3}{1+5sRC+6s^2 C^2 R^2 + s^3 C^3 R^3}$$

*:*.

Now

.:.

$$V_o = V_f = I_3 R = \frac{V_i R^2 s^3 C^3}{1 + 5 sRC + 6s^2 C^2 R^2 + s^3 C^3 R^3} \dots (21)$$

$$\beta = \frac{V_o}{V_i} = \frac{R^3 s^3 C^3}{1 + 5sCR + 6s^2 C^2 R^2 + s^3 C^3 R^3} \qquad \dots (22)$$

Replacing s by j

$$\omega$$

, s<sup>2</sup> by -  $\omega^2$ , s<sup>3</sup> by - j $\omega^3$

$$\therefore \qquad \beta = \frac{-j\omega^3 R^3 C^3}{1+5j\omega CR-6\omega^2 C^2 R^2 - j\omega^3 C^3 R^3}$$

Dividing numerator and denominator by  $-j\omega^3 R^3 C^3$  and replacing  $\frac{1}{\omega RC}$  by  $\alpha$  we get,

$$\beta = \frac{1}{1+6j\alpha-5\alpha^2-j\alpha^3}$$

$$\beta = \frac{1}{(1-5\alpha^2)+j\alpha(6-\alpha^2)} \qquad \dots (23)$$

To have phase shift of 180°, the imaginary part in the denominator must be zero.

$\therefore \qquad \alpha(6-\alpha^2) = 0$

neglecting zero value

...

$$\alpha^2 = 6$$

$$\alpha = \sqrt{6}$$

$$\frac{1}{\omega RC} = \sqrt{6}$$

$$\omega = \frac{1}{RC\sqrt{6}}$$

$$f = \frac{1}{2\pi RC\sqrt{6}}$$

...

This is the frequency with which circuit oscillates,

At this frequency,

$$\beta = \frac{1}{1 - 5 \times (\sqrt{6})^2} = -\frac{1}{29}$$

The negative sign indicates a phase shift of  $180^\circ$

$$|\beta| = \frac{1}{29} \qquad \dots (25)$$

Now to have the oscillations,  $|A\beta| \ge 1$

...

...

$$|\mathbf{A}| |\beta| > 1$$

$$|\mathbf{A}| \geq \frac{1}{|\beta|} \geq \frac{1}{\left(\frac{1}{29}\right)}$$

Thus circuit will work as an oscillator which will produce a sinusoidal waveform if the gain is 29 and total phase shift around a loop is 360°. This satisfies the Barkhausen criterion for the oscillator. These oscillators are used over the audio frequency range i.e. about 20 Hz up to 100 kHz. Pblm.2.2.1-Solved Problem:

The capacitor value of an RC phase shift oscillator using OP AMP is 0.01µF and the desired frequency of oscillation is 25 KHz. The voltage gain of the amplifier should be 30. Thus calculate the value of R of RC feedback network, input resistor R1 and feedback resistor R2 connected to the amplifier.

Solution:

Value of R in RC feedback network:

Given C=0.01 µF, and Frequency f= 25 KHz.

$$f = \frac{1}{2\pi RC\sqrt{6}}$$

$$R = \frac{1}{2\pi f C \sqrt{6}}$$

$$R = \frac{1}{2\pi * 25 * 10^3 * 0.01 * 10^{-6} * \sqrt{6}}$$

$R = 260 \, K \Omega$

Thus Resistor R value in RC network is 260 K $\square$ .

Value of R1 in amplifier circuit:

Given A=30. R1 or R2 are not given and thus we can assume any one resistor value. If R1 is assumed to be 1K□ then R2 can be estimated. Since it is an inverting amplifier Its gain is,

$$A = \left| \frac{-R2}{R1} \right|$$

$$30 = \frac{R2}{1K\Omega}$$

$$R2 = 30 K\Omega$$

Thus Resistor R2 (acts as a feedback resistor) value in amplifier is 30 K  $\square$  .

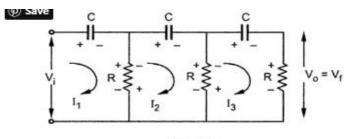

#### 2.2.2. Wien's Bridge Oscillators

Unlike RC phase shift oscillator, Wien bridge oscillator never uses phase-shift concept. It uses balancing concept of lead-lag network.

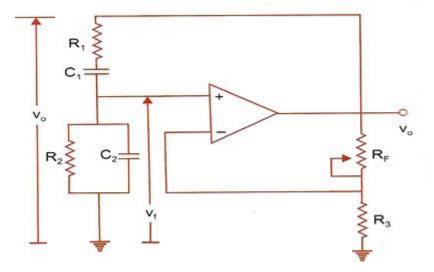

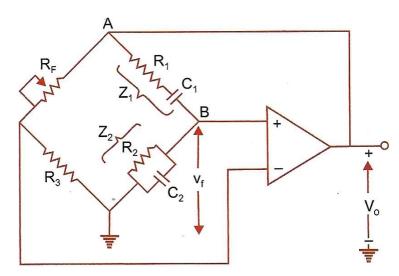

Construction: Here this oscillator is connected in a bridge fashion. The inverting terminal is connected to a junction where resistors R<sub>3</sub> and R<sub>F</sub> are connected. The other end of R<sub>3</sub> is grounded and R<sub>F</sub> is connected to output terminal of the amplifier. This forms a reference voltage across R<sub>3</sub> being fed into inverting terminal as shown in the fig. 2.2.2.a & 2.2.2.b

Fig.2.2.2.a. Wien's Bridge Oscillator

The non-inverting connected in between two reactance offering components  $Z_1$  and  $Z_2$  as shown in the fig. 2.2.2.b.  $Z_1$  comprises of serially connected resistor  $R_1$  and capacitor  $C_1$  whereas  $Z_2$  comprises of parallel connected resistor  $R_2$  and capacitor  $C_2$ . This combination of  $Z_1$  and  $Z_2$  is termed as *lead-lag circuit*.

Fig.2.2.2.b. Wien's Bridge Oscillator-Reconstructed

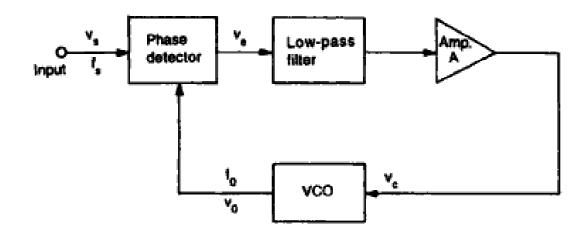

Working: Here the reactive circuits  $Z_1$  and  $Z_2$  connected to non-inverting terminal at B as shown in the fig. 3.3.2.b. A noise voltage is generated between the imbalanced input terminals is amplified by the amplifier and fed in the bridge circuit.

For particular low-frequencies, the capacitors act as open circuit and thus the output voltage of lead-lag circuit shall be zero and for high frequencies the capacitors cat as short circuit and thus voltage shall be zero. Only for a particular frequency called *resonant frequency*, resistance value equals to capacitive reactance value. Thus maximum current is available at this frequency only. So the output appears only for resonant frequency.

The other resistor values of R<sub>3</sub> and R<sub>F</sub> of bridge are adjusted to enhance the output to a maximum level. Thus the oscillation is generated.

The amplifier is a non-inverting amplifier circuit and so no phase shift is introduced. Phase shift is  $0^{\circ}$  (or  $2\Box$ ) for the whole circuit. And the overall gain shall be also more than 1. Thus the Barkhausen's criteria for sustained oscillations are satisfied.

If  $R_1 = R_2 = R$  and  $C_1 = C_2 = C$  then  $R = X_C$  at resonant frequency where  $X_C$  is capacitive reactance of C.

Thus

$$R = X_C = \frac{1}{2\pi fC}$$

$$f = \frac{1}{2\pi RC}$$

This is the frequency of oscillation

### **2.3** OP-AMP MULTIVIBRATORS

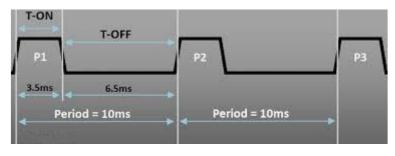

Multivibrators are square wave oscillators that produce pulse waveforms with various ON time and OFF time. As shown in fig. 2.3.a, P1, P2 and P3 are ON time of the pulse whose total time period is 10 ms with ToN and ToFF are 3.5 ms and 6.5 ms respectively. ToN and ToFF are two states of the pulse. The place where ToN transits to ToFF or ToFF to ToN is termed as *state*

transition.

The state transition may have slope (with a small time for transition) or infinite slope (No time for transition-being abrupt).

There are three types of multivibrators available according to their state transition. They are (a.) astable, (b.) monostable, and (c). bistable multivibrators.

Astable multivibrator is one that generates pulses those transits from one state to another without any external trigger. It is done by its free-will controlled by the design aspects. Thus this is called *free-running* multivibrator. So the states are not stable for a long time, the states can be termed as Quasi-stable states. Hence this multivibrator generates pulses of no stable states, it is termed as astable multivibrator.

Monostable multivibrator is one that generates pulses those transits from one state to another with the help of *one* external trigger. The multivibrator remains in one state (stable state) and when an external pulse is applied then it transits state from present Stable state to a quasi- stable state. It remains at quasi-stable state for a time period of T as it is designed and then returns to a stable state without any external trigger. Since it changes state from stable to quasi- stable using one external trigger, it is termed as one-shot multivibrator or monostable multivibrator.

Bistable multivibrator is one that generates pulses those transits from one state to another with the help of two external trigger. The multivibrator remains in one state (stable state) and when an external pulse is applied then it transits state from present Stable state to a next stable state. It remains at second stable state until another external trigger is applied. Thus this multivibrator has stable states only and the transitions happen only when triggers are applied, it is termed as bistable multivibrators.

Other related terminology: Duty cycle means

$$D = \frac{T_{ON}}{T_{ON} + T_{OFF}} \%$$

If  $T_{ON}$  is 5 ms and  $T_{OFF}$  is 10 ms, then Duty cycle D=5/15 ms, D=33%. D=50%, then  $T_{ON} = T_{OFF}$

Possible questions: What is a Multivibrator? Define the terminology of astable, monostable and bistable multivibrators.

2.3.1. Astable Multivibrators

These multivibrators are termed as *"Free Running"* multivibrators, and they have only quasi stable states as seen earlier in introduction.

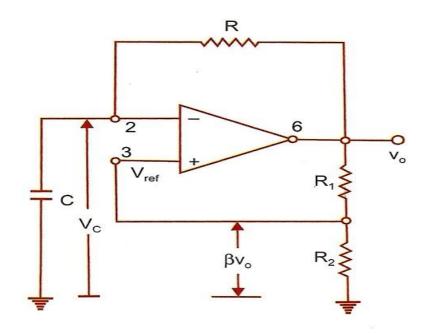

The circuit diagram of astable multivibrator using Operational amplifier is shown below fig.

2.3.1.a.

Fig.2.3.1.a. Astable Multivibrator – Circuit Diagram

**Construction:**

The circuit as simple and resembles like OP AMP Schmitt trigger circuit. One end of a capacitor C and a resistor R are connected to the inverting terminal. The other end of the resistor is connected to the output terminal and that of capacitor is connected to ground terminal. This capacitor C and feedback resistor R decide the period for oscillation of the multivibrator. A resistor R1 is connected between the output terminal and non-inverting terminal and another resistor R2 is

connected between non-inverting terminal and ground terminals. If the output voltage is considered as  $V_0$ , then the voltage tapped between R2 shall be a reference voltage applied to the non-inverting terminal with amplitude of  $\beta V_0$  where  $\beta$  is feedback factor for comparison.

Working:

Considering fig. 2.3.1.a and 2.3.1.b, the working part of this generator can be explained.

At Time 0: At time 0, assume the output transits from  $-V_{sat}$  to  $+V_{sat}$ . Since the output is  $+V_{sat}$  at time 0, reference voltage  $+\beta V_0$  and capacitor voltage is  $-\beta V_0$ .

From Time 0 to Time T1: Since reference is at  $+\beta V_0$ , the inverting terminal is also at  $+\beta V_0$ due to virtual ground. Now the capacitor tries to charge till the output voltage  $+V_0$ . It reaches  $+\beta V_0$  and tries to charge more, then the inverting terminal go beyond reference voltage  $+\beta V_0$ after time constant RC.

At Time T1: At time T1, since the inverting terminal goes little above than reference voltage  $+\beta V_0$ , the output transits from  $+V_{sat}$  to  $-V_{sat}$ . Now capacitor voltage remains at  $+\beta V_0$ . The reference voltage at non-inverting terminal is at  $-\beta V_0$ . The time T1 is decided by RC (time constant) factor.

After Time T1: Since reference is at  $-\beta V_0$ , the inverting terminal is also at  $-\beta V_0$  due to virtual ground. Now the capacitor tries to charge till the output voltage  $-V_0$ . It tries to reach  $-\beta V_0$  and tries to charge more, then the inverting terminal go beyond reference voltage  $-\beta V_0$  after time RC (time constant). Now again whatever happened at time 0 happens again. These 3 steps repeat periodically till power is available for the circuit.

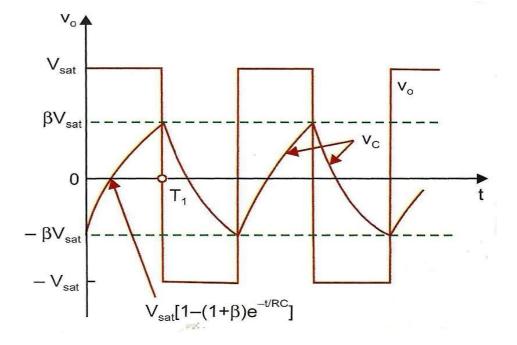

Fig.2.3.1.b. Astable Multivibrator – Output Waveforms

# **DERIVATION OF FREQUENCY OF OSCILLATION FOR OP-AMP ASTABLE MULTIVIBRATOR**

Generally

$$V_{C} = V_{final} + (V_{initial} - V_{final})e^{-t/RC}$$

Where  $V_C$  is capacitor voltage,  $V_{initial}$  and  $V_{final}$  are capacitors' initial and final charging voltages respectively, t is the time function, RC is time constant where R and C are value of Resistor and capacitor attached to inverting terminal of the opamp.

In this circuit

$$V_{initial} = -\beta V_{sat}$$

$V_{final} = V_{sat}$

but capacitor charges upto  $+\beta V_{sat}$  only

Now substituting these values in equation above

$$V_{C} = V_{sat} + (-\beta V_{sat} - V_{sat})e^{-t/RC}$$

$$V_{C} = V_{sat} - V_{sat}(1+\beta)e^{-t/RC}$$

At time T<sub>1</sub>, V<sub>C</sub>, is  $+\beta V_{sat}$  (in waveform fig.2.3.1.b), the above equation becomes

$$V_{\mathcal{C}} = \beta V_{sat} = V_{sat} - V_{sat} (1+\beta) e^{-T_1/RC}$$

At time T<sub>1</sub>, V<sub>G</sub> is  $+\beta$ V<sub>sat</sub> (in waveform fig.2.3.1.b), the above equation becomes

$$V_{C} = \beta V_{sat} = V_{sat} - V_{sat} (1+\beta) e^{-T_{1}/RC}$$

$$V_{sat}(1+\beta)e^{-T_1/RC} = V_{sat} - \beta V_{sat}$$

$$V_{sat}(1+\beta)e^{-T_1/RC} = V_{sat}(1-\beta)$$

$$e^{-T_{1}/RC} = \frac{V_{sat}(1-\beta)}{V_{sat}(1+\beta)}$$

$$\frac{1}{e^{T_1/RC}} = \frac{(1-\beta)}{(1+\beta)}$$

Inverting both sides we get,

$$e^{T_1/RC} = \frac{(1+\beta)}{(1-\beta)}$$

Taking Natural logarithm on both sides,

$$T_1/RC = ln \frac{(1+\beta)}{(1-\beta)}$$

$$T_1 = RC ln \frac{(1+\beta)}{(1-\beta)}$$

But as shown in the figure,  $T_1$  is only ON time and T is the total cycle time which is  $T_1+T_2$  where  $T_2$  is considered = $T_1$ . Then T=2T<sub>1</sub>,

$$T = 2RC \ln \frac{(1+\beta)}{(1-\beta)}$$

Since

$$\beta = \frac{R_2}{R_1 + R_2}$$

(feedback Factor), R<sub>1</sub> and R<sub>2</sub> decides value of  $\beta$ ,

Case 1:

If R<sub>1</sub>=R<sub>2</sub>, then  $\beta = \frac{1}{1+1} = 0.5$ . Then

$$T = 2RC \ln \frac{(1.5)}{(0.5)}$$

$$T = 2RC \ln(3)$$

$$T = 2RC (1.0986)$$

$$T = 2.1972 RC$$

Case 2:

If R<sub>1</sub>=1.16 R<sub>2</sub>, then  $\beta = \frac{1}{1+1.16} = 0.462$  Then  $T = 2RC \ln(2.718)$ as  $\ln(2.718) = 1$ T = 2RC (1)

T = 2RC

Thus when R<sub>1</sub>=1.16 R<sub>2</sub>,

The frequency of oscillation of Astable multivibrator is

$$f = 1/T = 1/2RC$$

## **2.3.2.** Monostable Multivibrators

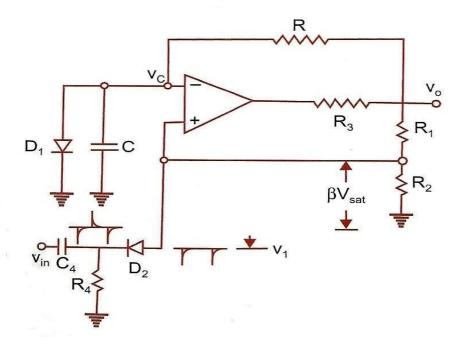

These multivibrators are termed as *"one-shot multivibrators"* and they have only one stable state and other is quasi-stable state induced by single external trigger as seen earlier in introduction.

The circuit diagram of monostable multivibrator using Operational amplifier is shown below fig. 2.3.2.a.

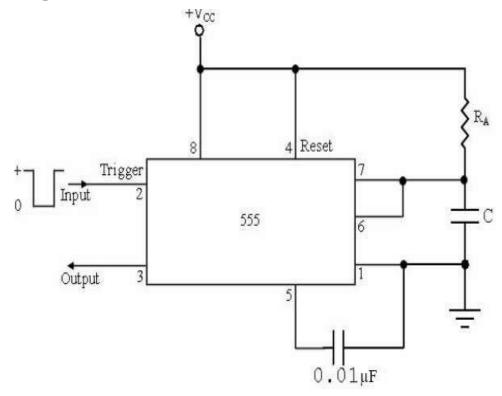

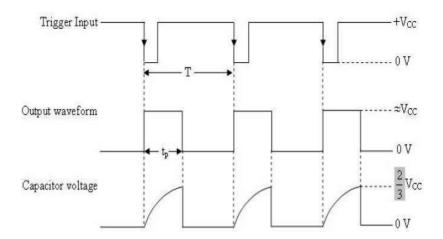

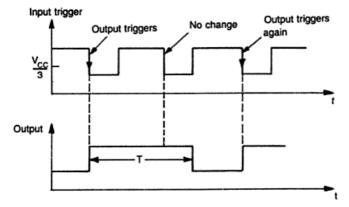

Fig.2.3.2.a. Monostable Multivibrator Using OP AMP

### **Construction:**

The circuit as simple and resembles like OP AMP Schmitt trigger circuit. One end of a capacitor C and a resistor R are connected to the inverting terminal. The other end of the resistor is connected to the output terminal and that of capacitor is connected to ground terminal. A diode D1 is connected parallel to the capacitor C. This capacitor C and feedback resistor R decide the period for T of the multivibrator. A resistor R1 is connected between the output terminal and non-inverting terminal and another resistor R2 is connected between non-inverting terminal and ground terminals. If the output voltage is considered as V<sub>0</sub>, then the voltage tapped between R2 shall be a reference voltage applied to the non-inverting terminal with amplitude of  $\beta V_0$  where  $\beta$  is feedback factor for comparison.

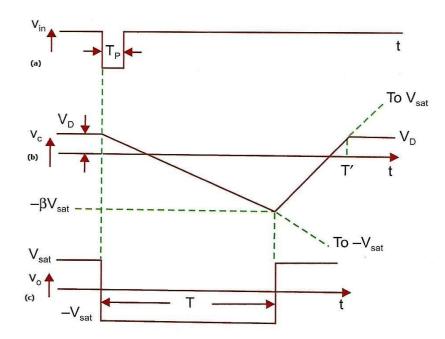

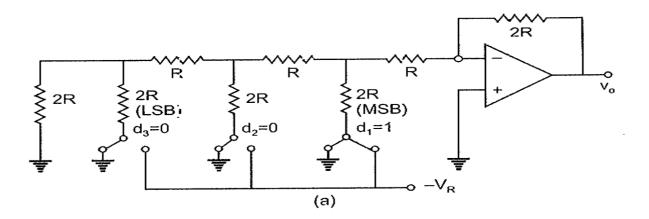

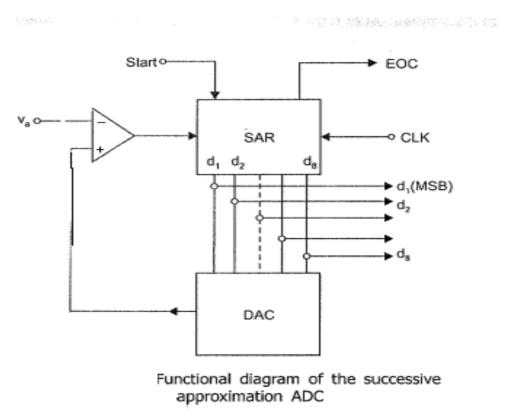

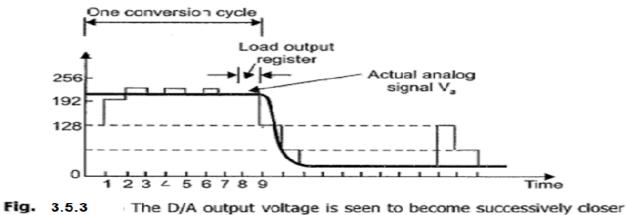

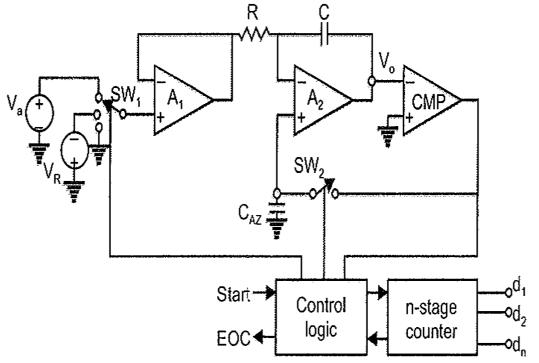

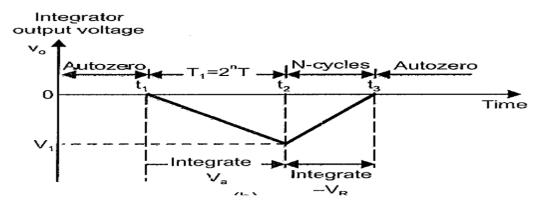

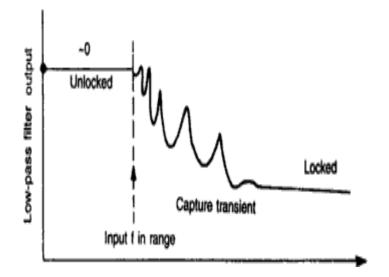

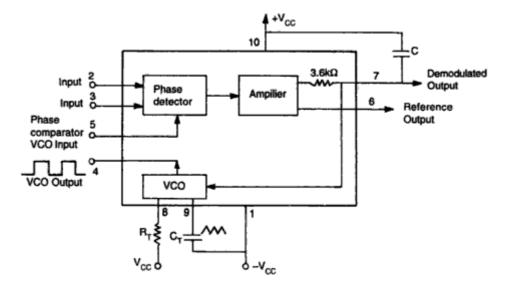

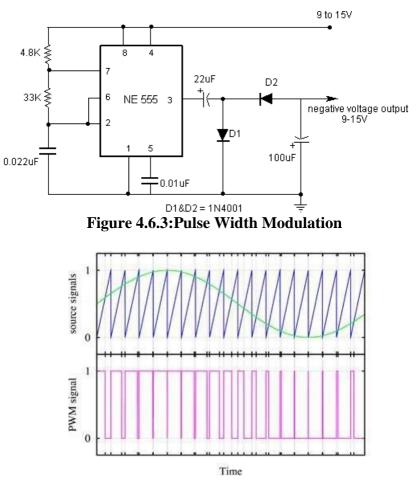

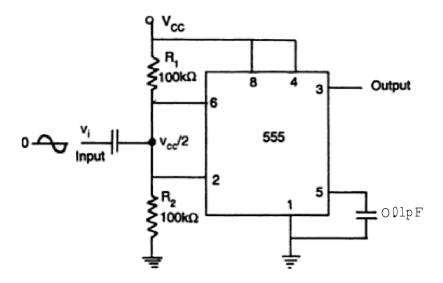

A pulse trigger circuit consisting of diode D2 and a differentiator circuit connected to pulse generator of negative pulse width  $T_p$ . The anode of the diode D2 is connected to non-inverting terminal