### SCHOOL OF COMPUTING

### DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

**UNIT-I- SOFTWARE TESTING – SBS1604**

#### **COURSE OBJECTIVES:**

- To study fundamental concepts in software testing.

- To discuss various software testing issues and solutions in software unit test, integration and system testing.

- To expose the advanced software testing topics, such as object-oriented software testing methods.

- Finding defects which may get created by the programmer while developing the software.

#### **COURSE OUTCOMES:**

At the end of this course student will:

- List a range of different software testing techniques and strategies and be able to apply specific(automated) unit testing method to the projects.

- Distinguish characteristics of structural testing methods.

- Demonstrate the integration testing which aims to uncover interaction and compatibility problems as early as possible.

- Discuss about the functional and system testing methods.

- o Demonstrate various issues for object-oriented testing.

#### UNIT 1

**Introduction:** Software testing – Role of software testing – Three step process to becoming a world class testing organization - A structural approach to testing – Test strategy – methods for developing test strategy

#### **Introduction:** Software testing

#### The Evolving Profession of Software Engineering

- This is an exciting time to be a software developer.

- Software systems are becoming more challenging to build.

- They are playing an increasingly important role in society.

- People with software development skills are in demand.

- New methods, techniques, and tools are becoming available to support development and maintenance tasks.

- Because software now has such an important role in our lives both economically and socially, there is pressure for software professionals to focus on quality issues.

- Poor quality software that can cause loss of life or property is no longer acceptable to society.

- Failures can result in catastrophic losses.

- Conditions demand software development staff with interest and training in the areas of software product and process quality.

- Highly qualified staff ensure that software products are built on time, within budget, and are of the highest quality concerning attributes such as reliability, correctness, usability, and the ability to meet all user requirements.

- In response to the demand for high-quality software, and the need for well-educated software professionals, there is a movement to change the way software is developed and maintained, and the way developers and maintainers are educated.

- The profession of software engineering is slowly emerging as a formal engineering discipline.

- As a new discipline, it will be related to other engineering disciplines, and have associated with it a defined body of knowledge, a code of ethics, and a certification process.

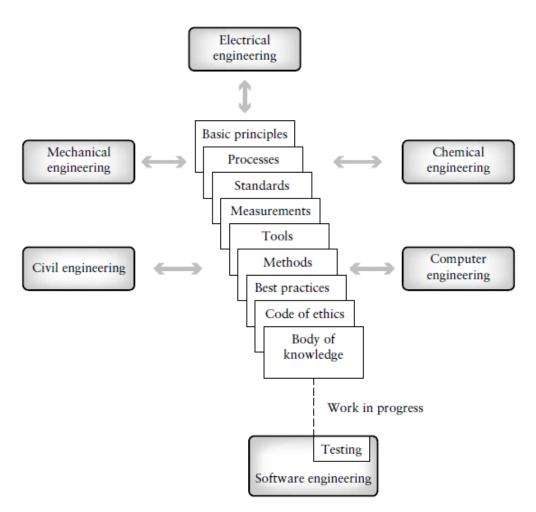

- The education and training of engineers in each engineering discipline are based on the teaching of related scientific principles, engineering processes, standards, methods, tools, measurement, and best practices as shown in the Figure below.

- As a reflection of the movement toward a software engineering profession, and these educational needs, the IEEE Computer Society and the Association of Computing Machinery (ACM), the two principal societies for software professionals, have appointed joint task forces.

- The goals of the task force teams are to define a body of knowledge that covers the software engineering discipline, to discuss the nature of education for this new profession, and to define a code of ethics for the software engineer.

- Foreseeing the emergence of this new engineering discipline, some states are already preparing licensing examinations for software engineers.

- This text is based on the philosophy that software development should be viewed and taught as an engineering discipline and that quality in both the process and the product are of prime importance to professionals in this field.

#### Using an engineering approach to software development implies that:

- The development process is well understood

- Projects are planned

- Life cycle models are defined and adhered to

- Standards are in place for product and process

- Measurements are employed to evaluate product and process quality

- Components are reused

- Validation and verification processes play a key role in quality determination

- Engineers have proper education, training, and certification

- This text aims to support the education of a software professional called a test specialist.

- A test specialist is one whose education is based on the principles, practices, and processes that constitute the software engineering discipline, and whose specific focus is on one area of that discipline—software testing.

- A test specialist who is trained as an engineer should know test-related principles, processes, measurements, standards, plans, tools, and methods, and should learn how to apply them to the testing tasks to be performed.

- This text aims to educate the reader in the testing discipline.

- Testing concepts, instead of being presented as an isolated collection of technical and managerial activities will instead be integrated within the context of a quality testing process that grows incompetency and uses engineering principles to guide improvement growth.

- In this way, all of the elements of the testing discipline emerge incrementally and allow the tester to add knowledge and skills that follow a natural evolutionary pattern.

- $\circ~$  The integrating framework for presenting testing concepts is the Testing Maturity Model.

#### The Role of Process in Software Quality

- The need for software products of high quality has pressured those in the profession to identify and quantify quality factors such as usability, testability, maintainability, and reliability, and to identify engineering practices that support the production of quality products having these favourable attributes.

- Among the practices identified that contribute to the development of high-quality software are project planning, requirements management, development of formal specifications, structured design with use of information hiding and encapsulation, design and code reuse, inspections and reviews, product and process measures, education and training of software professionals, development and application of CASE tools, use of effective testing techniques, and integration of testing activities into the entire life cycle.

- In addition to identifying these individual best technical and managerial practices, software researchers realized that it was important to integrate them within the context of a high-quality software development process.

- Process, in the software engineering domain, is the set of methods, practices, standards, documents, activities, policies, and procedures that software engineers use to develop and maintain a software system and its associated artifacts, such as project and test plans, design documents, code, and manuals.

- It also was clear that adding individual practices to an existing software development process in an ad hoc way was not satisfactory.

- The software development process, like most engineering artifacts, must be engineered.

- That is, it must be designed, implemented, evaluated, and maintained.

- As in other engineering disciplines, a software development process must evolve consistently and predictably, and the best technical and managerial practices must be integrated systematically.

- Models such as the Capability Maturity Model (CMM)\* and SPICE were developed to address process issues.

- These models allow an organization to evaluate its current software process and to capture an understanding of its state.

- Strong support for incremental process improvement is provided by the models, consistent with historical process evolution and the application of quality principles.

- The models have received much attention from the industry, and resources have been invested in process improvement efforts with many successes recorded.

- All the software process improvement models that have had wide acceptance in the industry are high-level models, in the sense that they focus on the software process as a whole and do not offer adequate support to evaluate and improve specific software development sub-processes such as design and testing.

- Most software engineers would agree that testing is a vital component of a quality software process, and is one of the most challenging and costly activities carried out during software development and maintenance.

- Despite its vital role in the production of quality software, existing process evaluation and improvement models such as the CMM, Bootstrap, and ISO-9000 have not adequately addressed testing process issues.

- The Testing Maturity Model (TMM), as described throughout this text, has been developed at the Illinois Institute of Technology by a research group headed by the author, to address deficiencies in these areas.

#### **Testing as a Process**

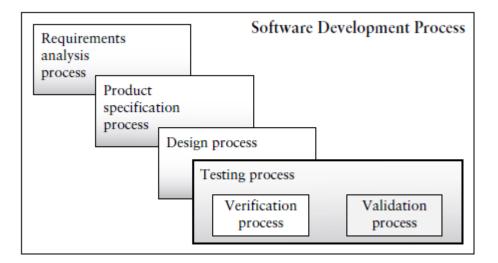

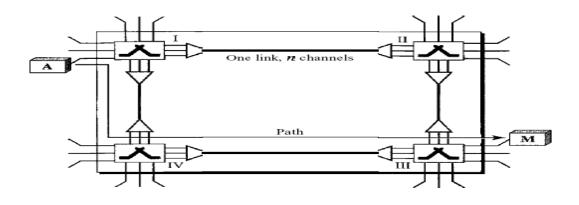

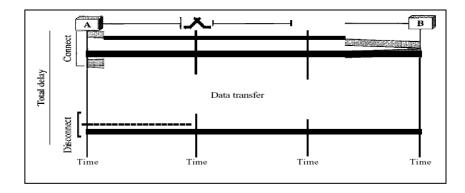

- The software development process has been described as a series of phases, procedures, and steps that result in the production of a software product.

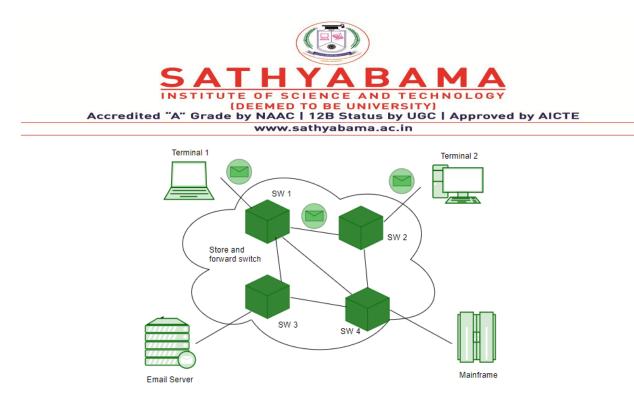

- Embedded within the software development process are several other processes including testing.

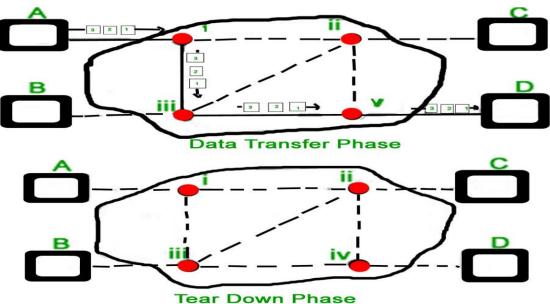

- Some of these are shown in Figure

- Testing itself is related to two other processes called verification and validation as shown in Figure

**Validation** is the process of evaluating a software system or component during, or at the end of, the development cycle to determine whether it satisfies specified requirements.

**Validation** is usually associated with traditional execution-based testing, that is, exercising the code with test cases.

**Verification** is the process of evaluating a software system or component to determine whether the products of a given development phase satisfy the conditions imposed at the start of that phase.

**Verification** is usually associated with activities such as inspections and reviews of software deliverables.

#### Testing itself has been defined in several ways. Two definitions are shown below.

**Testing** is generally described as a group of procedures carried out to evaluate some aspect of a piece of software.

**Testing** can be described as a process used for revealing defects in software, and for establishing that the software has attained a specified degree of quality concerning selected attributes.

**Note** that these definitions of testing are general. They cover both validation and verification activities and include in the testing domain all of the following: technical reviews, test planning, test tracking, test case design, unit test, integration test, system test, acceptance test, and usability test. The definitions also describe testing as a dual-purpose process—one that reveals defects, as well as one that is used to evaluate quality attributes of the software such as reliability, security, usability,

and correctness. Also note that testing and debugging, or fault localization, are two very different activities. The debugging process begins after testing has been carried out and the tester has noted that the software is not behaving as specified.

**Debugging,** or fault localization is the process of (1) locating the fault or defect, (2) repairing the code, and (3) retesting the code.

Testing as a process has economic, technical, and managerial aspects. Economic aspects are related to the reality that resources and time are available to the testing group on a limited basis. In fact, complete testing is in many cases not practical because of these economic constraints. An organization must structure its testing process so that it can deliver software on time and within budget, and also satisfy the client's requirements. The technical aspects of testing related to the techniques, methods, measurements, and tools used to insure that the software under test is as

defect-free and reliable as possible for the conditions and constraints under which it must operate. Testing is a process, and as a process, it must be managed. Minimally that means that an organizational policy for testing must be defined and documented. Testing procedures and steps must be defined and documented. Testing must be planned, testers should be trained, the process should have associated quantifiable goals that can be measured and monitored. Testing as a process should be able to evolve to a level where there are mechanisms in place for making continuous improvements.

#### An Overview of the Testing Maturity Model

Several important test-related issues have emerged from the previous discussion.

We have learned that

- 1. there is a demand for software of high quality with low defects;

- 2. process is important in the software engineering discipline;

- 3. software testing is an important software development sub-process;

- 4. existing software evaluation and improvement models have not adequately addressed testing issues.

An introduction to the Testing Maturity Model is now presented to the reader as a framework for discussion of these issues, and as a means for addressing them. The model is discussed in more detail in later chapters of this text. The focus of the TMM is on testing as a process in itself that can be evaluated and improved.

#### In the testing domain possible benefits of test process improvement are the following:

- Smarter testers

- Higher quality software

- Ability to meet budget and schedule goals

- Improved planning

- Ability to meet quantifiable testing goals

Test process improvement is supported by the set of levels and maturity goals in the TMM. Achievement of the maturity goals results in incremental improvement of an organization's testing process. The TMM Assessment Model supports test process evaluation. Section 1.3 gives the reader an overview of the set of levels and maturity goals. The levels and goals serve as guidelines for the organization of this text and define the sequence for the introduction of testing concepts. The development of version 1.0 of the TMM was guided by the work done on the Capability Maturity Model for software (CMM), a process improvement model that has received widespread support from the software industry in the United States. The CMM is classified architecturally as a staged process improvement model. This type of process improvement model architecture prescribes the stages that an organization must proceed through in an orderly fashion to improve its software development process. Other process improvement models can be described as having a continuous type of architecture, for example, the SPICE model. In this type of architecture, there is no fixed set of levels or stages to proceed through. An organization applying a continuous model can select areas for improvement from many different categories. The CMM has five levels or stages that describe an evolutionary pattern of software process maturity and serve as a guide for improvement. Each level has a set of Key Process Areas (KPA) that an organization needs to focus on to achieve maturity at that level. There are also key practices associated with each level that provide support for implementing improvements at that level. The CMM also has an assessment procedure that allows an organization to evaluate the current state of its software process and identify process strengths and weaknesses.

Other input sources to TMM development include Gelperin and Hetzel's Evolution of Testing Model, which describes the evolution of the testing process in the industry over 40 years; Beizer's testing model, which describes the evolution of the individual tester's thinking; and the Software Testing Practices Survey Report, which identifies best test practices in industry as of 1993. More details relating to these items as well as the TMM maturity goals and the TMM Assessment Model are found in later chapters of this text.

#### **TMM Levels**

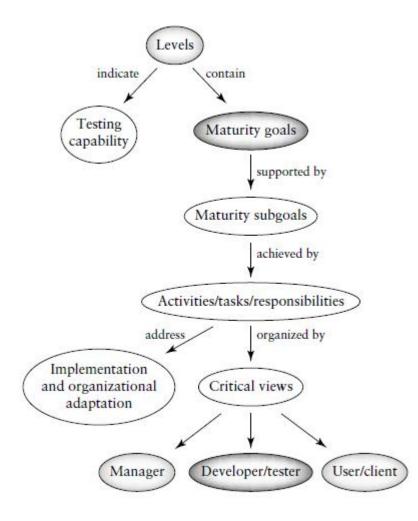

As in the case of the CMM, the TMM also follows what is called a staged architecture for process improvement models. It contains stages or levels through which an organization passes as its testing process evolves from one that is ad hoc and unmanaged to one that is managed, defined, measured, and optimizable. The internal structure of the TMM is rich in testing practices that can be learned and applied in a systematic way to support a quality testing process that improves in incremental steps. There are five levels in the TMM that prescribe a maturity hierarchy and an evolutionary path to test process improvement. The characteristics of each level are described in terms of testing capability organizational goals, and roles/responsibilities for the key players in the testing process, the managers, developers/testers, and users/clients.

## Each level except for level 1 has a structure that consists of the following:

• A set of maturity goals. The maturity goals identify testing improvement goals that must be addressed to achieve maturity at that level. To be placed at a level, an organization must satisfy

the maturity goals at that level. The TMM levels and associated maturity goals are shown in Figure

• **Supporting maturity subgoals.** They define the scope, boundaries, and needed accomplishments for a particular level.

• Activities, tasks, and responsibilities (ATR). The ATRs address implementation and organizational adaptation issues at each TMM level.

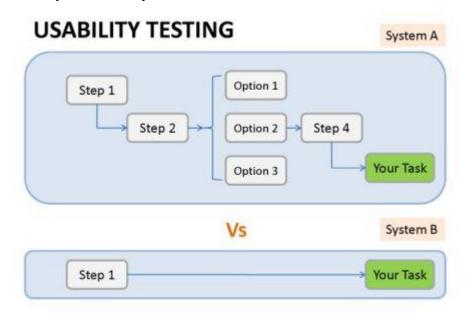

Supporting activities and tasks are identified, and responsibilities are assigned to appropriate groups. Figure 1.4 illustrates the TMM level structure. Each maturity goal at each TMM level is supported by a set of maturity subgoals. The maturity subgoals are achieved through a group of activities and tasks with responsibilities (ATR). Activities and tasks are defined in terms of actions that must be performed at a given level to improve testing capability; they are linked to organizational commitments. Responsibilities are assigned for these activities and tasks to three groups that TMM developers believe represent the key participants in the testing process: managers, developers/ testers, and users/clients. In the model, they are referred to as "the three critical views (CV)." The definition of their roles is essential in developing a maturity framework. The manager's view involves commitment and the ability to perform activities and tasks related to improving testing capability. The developer/tester's view encompasses the technical activities and tasks that, when applied, constitute quality testing practices. The user's or client's view is defined as a cooperating or supporting, view. The developers/ testers work with client/user groups on quality-related activities and tasks that concern user-oriented needs. The focus is on soliciting client/ user support, consensus, and participation in activities such as requirements analysis, usability testing, and acceptance test planning.

The maturity goals at each level of the TMM are shown in Figure 1.5. They are fully described in published papers and are also listed below along with a brief description of the characteristics of an organization at each TMM level [2–6]. The description will introduce the reader to the evolutionary path prescribed in the TMM for test process improvement. Additional details are provided in subsequent text chapters.

#### Level 1—Initial: (No maturity goals)

At TMM level 1, testing is a chaotic process; it is ill-defined, and not distinguished from debugging. A documented set of specifications for software behavior often does not exist. Tests are developed in an ad hoc way after coding is completed. Testing and debugging are interleaved to get the bugs out of the software. The objective of testing is to show the software works (it is minimally functional) [1,5]. Software products are

often released without quality assurance. There is a lack of resources, tools, and properly trained staff. This type of organization would be at level 1 of the CMM.

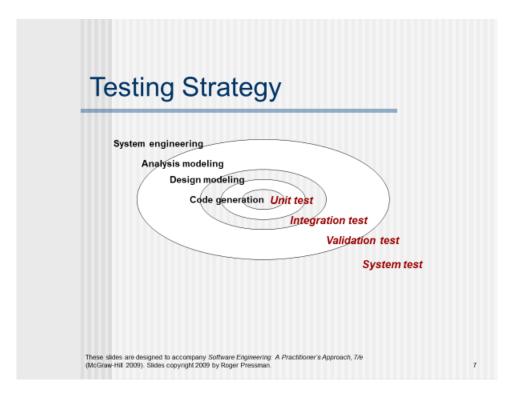

Level 2—Phase Definition: (Goal 1: Develop testing and debugging goals; Goal 2: Initiate a testing planning process; Goal 3: Institutionalize basic testing techniques and methods) At level 2 of the TMM testing is separated from debugging and is defined as a phase that follows coding. It is a planned activity; however, test planning at level 2 may occur after coding for reasons related to the immaturity of the testing process. For example, there may be the perception at level 2, that all testing is execution based and dependent on the code; therefore, it should be planned only when the code is complete. The primary goal of testing at this level of maturity is to show that the software meets its stated specifications [2,5]. Basic testing strategies, and a validation cross-reference matrix. Testing is multileveled: there are unit, integration, system, and acceptance levels. Many quality problems at this TMM level occur because test planning occurs late in the software life cycle. Also, defects are propagated from the requirements and design phases into the code. There are no review programs as yet to address this important issue. Postcode, execution-based testing is still considered the primary testing activity.

# Level 3—Integration: (Goal 1: Establish a software test organization; Goal 2: Establish a technical training program; Goal 3: Integrate testing into the software life cycle; Goal 4: Control and monitor testing)

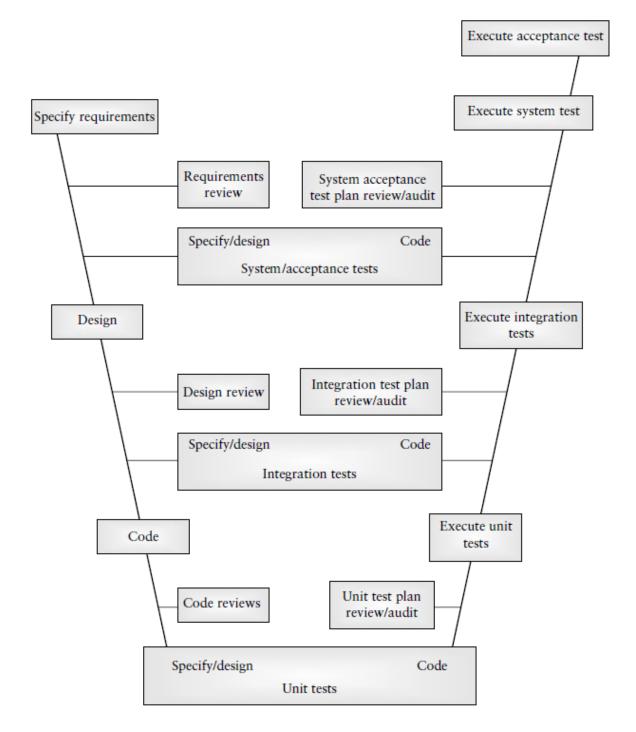

At TMM level 3, testing is no longer a phrase that follows coding but is integrated into the entire software life cycle. Organizations can build on the test planning skills they have acquired at level 2. Unlike level 2, planning for testing at TMM level 3 begins at the requirements phase and continues throughout the life cycle supported by a version of the V-model (see Section 8.7) [2]. Test objectives are established concerning the requirements based on user/client needs and are used for test case design. There is a test organization, and testing is recognized as a professional activity. There is a technical training organization with a testing focus. Testing is monitored to ensure it is going according to plan and actions can be taken if deviations occur. Basic tools support key testing activities, and the testing process is visible in the organization. Although organizations at this level begin to realize the important role of reviews in quality control, there is no formal review program and reviews do not as yet take place across the life cycle. A formal test measurement program has not yet been established to quantify a significant number of process and product attributes.

# Level 4—Management and Measurement: (Goal 1: Establish an organization-wide review program; Goal 2: Establish a test measurement program; Goal 3: Software quality evaluation)

Testing at level 4 becomes a process that is measured and quantified. Reviews at all phases of the development process are now recognized as testing/quality control activities. They are a complement to execution-based tests to detect defects and to evaluate and improve software quality. An extension of the V-model as shown in Figure 1.6 can be used to support the implementation of this goal [6,7]. Software products are tested for quality attributes such as reliability, usability, and maintainability. Test cases from all projects are collected and recorded in a test case database for test case reuse and regression testing. Defects are logged and given a severity level. Some of the deficiencies occurring in the test process are due to the lack of a defect prevention philosophy, and the porosity of automated support for the collection, analysis, and dissemination of test-related metrics.

## Level 5—Optimization/Defect Prevention/Quality Control: (Goal 1: Defect prevention; Goal 2: Quality control; Goal 3: Test process optimization)

Because of the infrastructure that is in place through achievement of the maturity goals at levels 1–4 of the TMM, the testing process is now said to be defined and managed; its cost and effectiveness can be monitored. At level 5, mechanisms are in place so that testing can be fine-tuned and continuously improved. Defect prevention and quality control are practiced. Statistical sampling, measurements of confidence levels, trustworthiness, and reliability drive the testing process. Automated tools support the running and rerunning of test cases. Tools also provide support for test case design, maintenance of test-related items, and defect collection and analysis. The collection and analysis of test-related metrics also have tool support. Process reuse is also a practice at TMM level 5 supported by a Process Asset Library (PAL).

#### **TESTING FUNDAMENTALS**

#### **Initiating a Study of Testing**

The study of software testing in this text begins with a description of essential test-related vocabulary items. Knowledge of these basic terms is essential to ensure that the discussions of testing concepts that follow are based on a common vocabulary that is widely accepted in academia and industry. A set of execution-based testing principles is also presented here to support test specialists. They provide a foundation for developing testing knowledge, acquiring testing skills, and developing an essential group of best practices. This introduction to the field of software testing concludes with a description of the role of the test specialist in a software development organization.

#### **Basic Definitions**

Below is a set of basic definitions for terms that will be used in this text. Additional definitions appear in subsequent chapters to aid in concept understanding. Many of the definitions used in this text are based on the terms described in the IEEE Standards Collection for Software Engineering [1]. The standards collection includes the IEEE Standard Glossary of Software Engineering Terminology, which is a dictionary devoted to describing software engineering vocabulary [2]. It contains working definitions of terms that are in use in both the academic and industrial worlds.

Where a definition has been directly adapted from an IEEE standards document a specific reference is given.

#### Errors

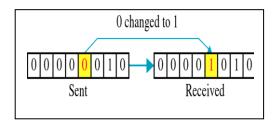

An error is a mistake, misconception, or misunderstanding on the part of a software developer.

In the category of developers we include software engineers, programmers, analysts, and testers. For example, a developer may misunderstand a design notation, or a programmer might type a variable name incorrectly.

#### **Faults (Defects)**

A fault (defect) is introduced into the software as the result of an error. It is an anomaly in the software that may cause it to behave incorrectly, and not according to its specification.

Faults or defects are sometimes called "bugs." Use of the latter term trivializes the impact faults have on software quality. Use of the term "defect" is also associated with software artifacts such as requirements and design documents. Defects occurring in these artifacts are also caused by errors and are usually detected in the review process.

#### Failures

A failure is the inability of a software system or component to perform its required functions within specified performance requirements [2].

During execution of a software component or system, a tester, developer, or user observes that it does not produce the expected results. In some cases a particular type of misbehaviour indicates a certain type of fault is present. We can say that the type of misbehaviour is a symptom of the fault. An experienced developer/tester will have a knowledge base of fault/symptoms/failure cases (fault models as described in Chapter 3) stored in memory. Incorrect behaviour can include producing incorrect values for output variables, an incorrect response on the part of a device, or an incorrect image on a screen. During development failures are usually observed by testers, and faults are located and repaired by developers. When the software is in operation, users may observe failures which are reported back to the development organization so repairs can be made. A fault in the code does not always produce a failure. In fact, faulty software may operate over a long period of time without exhibiting any incorrect behaviour. However, when the proper conditions occur the fault will manifest itself as a failure. Voas is among the researchers who discuss these conditions, which are as follows:

- 1. The input to the software must cause the faulty statement to be executed.

- 2. The faulty statement must produce a different result than the correct statement.

- 3. This event produces an incorrect internal state for the software.

- 4. The incorrect internal state must propagate to the output, so that the result of the fault is observable.

Software that easily reveals its' faults as failures is said to be more testable. From the testers point-of-view this is a desirable software attribute. Testers need to work with designers to insure that software is testable. There are other meanings assigned to the terms "testable" and "testability" that will be described later on in this chapter.

#### **Test Cases**

The usual approach to detecting defects in a piece of software is for the tester to select a set of input data and then execute the software with the input data under a particular set of conditions. In order to decide whether the software has passed or failed the test, the tester also needs to know what are the proper outputs for the software, given the set of inputs and execution conditions. The tester bundles this information into an item called a test case.

A **test case** in a practical sense is a test-related item which contains the following information:

- 1. A set of test inputs. These are data items received from an external source by the code under test. The external source can be hardware, software, or human.

- 2. Execution conditions. These are conditions required for running the test, for example, a certain state of a database, or a configuration of a hardware device.

- 3. Expected outputs. These are the specified results to be produced by the code under test.

The above description specifies the minimum information that should be found in a test case and is based on the IEEE description for this item [2]. An organization may decide that additional information should be included in a test case to increase its value as a reusable object, or to provide more detailed information to testers and developers. As an example, a test objective component could be included to express test goals such as to execute a particular group of code statements or check that a given requirement has been satisfied. Developers, testers, and/or software quality assurance staff should be involved in designing a test case specification that precisely describes the contents of each test case. The content and its format should appear in test documentation standards for the organization.

#### Test

A test is a group of related test cases, or a group of related test cases and test procedures

A group of related tests is sometimes referred to as a test set. A group of related tests that are associated with a database, and are usually run together, is sometimes referred to as a test suite

#### **Test Oracle**

A test oracle is a document, or piece of software that allows testers to determine whether a test has been passed or failed.

A program, or a document that produces or specifies the expected outcome of a test, can serve as an oracle. Examples include a specification (especially one that contains pre- and postconditions), a design document, and a set of requirements. Other sources are regression test suites. The suites usually contain components with correct results for previous versions of the software. If some of the functionality in the new version overlaps the old version, the appropriate oracle information can be extracted. A working trusted program can serve as its own oracle in a situation where it is being ported to a new environment. In this case its intended behaviour should not change in the new environment.

#### Test Bed

A test bed is an environment that contains all the hardware and software needed to test a software component or a software system.

This includes the entire testing environment, for example, simulators, emulators, memory checkers, hardware probes, software tools, and all other items needed to support execution of the tests.

#### **Software Quality**

Two concise definitions for quality are found in the IEEE Standard Glossary of Software Engineering Terminology:

- 1. Quality relates to the degree to which a system, system component, or process meets specified requirements.

- 2. Quality relates to the degree to which a system, system component, or process meets customer or user needs, or expectations.

In order to determine whether a system, system component, or process is of high quality we use what are called quality attributes. These are characteristics that reflect quality. For software artifacts we can measure the degree to which they possess a given quality attribute with quality metrics.

A **metric** is a quantitative measure of the degree to which a system, system component, or process possesses a given attribute [2]. There are product and process metrics. A very commonly used example of a software product metric is software size, usually measured in lines of code (LOC). Two examples of commonly used process metrics are costs and time required for a given task. Many other examples are found in Grady [6]. Appendix I gives additional references that discuss metrics in depth. Quality metrics are a special kind of metric.

A **quality metric** is a quantitative measurement of the degree to which an item possesses a given quality attribute

Many different quality attributes have been described for software, for example, in IEEE Standards for Software Quality Metrics Methodology and work by Schulmeyer and Grady

#### Some examples of quality attributes with brief explanations are the following:

**correctness**—the degree to which the system performs its intended function reliability—the degree to which the software is expected to perform its required functions under stated conditions for a stated period of time

**usability**—relates to the degree of effort needed to learn, operate, prepare input, and interpret output of the software

integrity—relates to the system's ability to withstand both intentional and accidental attacks

**portability**—relates to the ability of the software to be transferred from one environment to another

maintainability-the effort needed to make changes in the software

**interoperability**—the effort needed to link or couple one system to another. Another quality attribute that should be mentioned here is testability. This attribute is of more interest to developers/testers than to clients.

It can be expressed in the following two ways:

- 1. the amount of effort needed to test the software to ensure it performs according to specified requirements (relates to number of test cases needed),

- 2. the ability of the software to reveal defects under testing conditions (some software is designed in such a way that defects are well hidden during ordinary testing conditions). Testers must work with analysts, designers and, developers throughout the software life system to ensure that testability issues are addressed.

#### Software Quality Assurance Group

The software quality assurance (SQA) group in an organization has ties to quality issues. The group serves as the customers' representative and advocate. Their responsibility is to look after the customers' interests. The software quality assurance (SQA) group is a team of people with the necessary training and skills to ensure that all necessary actions are taken during the development process so that the resulting software conforms to established technical requirements.

They work with project managers and testers to develop quality-related policies and quality assurance plans for each project. The group is also involved in measurement collection and analysis, record keeping, and reporting. The SQA team members participate in reviews, and audits (special types of reviews that focus on adherence to standards, guidelines, and procedures), record and track problems, and verify that corrections have been made. They also play a role in software configuration management.

#### Reviews

In contrast to dynamic execution-based testing techniques that can be used to detect defects and evaluate software quality, reviews are a type of static testing technique that can be used to evaluate the quality of a software artifact such as a requirements document, a test plan, a design document, a code component. Reviews are also a tool that can be applied to revealing defects in these types of documents. A definition follows.

## A review is a group meeting whose purpose is to evaluate a software artifact or a set of software artifacts.

The composition of a review group may consist of managers, clients, developers, testers and other personnel depending on the type of artifact under review. A special type of review called an audit is usually conducted by a Software Quality Assurance group for the purpose of assessing compliance with specifications, and/or standards, and/or contractual agreements.

#### **Software Testing Principles**

Principles play an important role in all engineering disciplines and are usually introduced as part of an educational background in each branch of engineering. Figure 1.1 shows the role of basic principles in various engineering disciplines. Testing principles are important to test specialists/ engineers because they provide the foundation for developing testing knowledge and acquiring testing skills. They also provide guidance for defining testing activities as performed in the practice of a test specialist.

A principle can be defined as:

- 1. a general or fundamental, law, doctrine, or assumption;

- 2. a rule or code of conduct;

- 3. the laws or facts of nature underlying the working of an artificial device.

Extending these three definitions to the software engineering domain we can say that software engineering principles refer to laws, rules, or doctrines that relate to software systems, how to build them, and how they behave. In the software domain, principles may also refer to rules or codes of conduct relating to professionals who design, develop, test, and maintain software systems. Testing as a component of the software engineering discipline also has a specific set of principles that serve as guidelines for the tester. They guide testers in defining how to test software systems, and provide rules of conduct for testers as professionals. Glenford Myers has outlined such a set of execution-based testing principles in his pioneering book, The Art of Software Testing [9]. Some of these principles are described below. Principles 1–8, and 11 are derived directly from Myers' original set. The author has reworded these principles, and also has made modifications to the original set to reflect the evolution of testing from an art, to a quality-related process within the context of an engineering discipline. Note that the principles as stated below only relate to execution-based testing. Principles relating to reviews, proof of correctness, and certification as testing activities are not covered.

**Principle 1.** Testing is the process of exercising a software component using a selected set of test cases, with the intent of (i) revealing defects, and (ii) evaluating quality.

Software engineers have made great progress in developing methods to prevent and eliminate defects. However, defects do occur, and they have a negative impact on software quality. Testers need to detect these defects before the software becomes operational. This principle supports testing as an execution-based activity to detect defects. It also supports the separation of testing from debugging since the intent of the latter is to locate defects and repair the software. The term "software component" is used in this context to represent any unit of software ranging in size and complexity

from an individual procedure or method, to an entire software system. The term "defects" as used in this and in subsequent principles represents any deviations in the software that have a negative impact on its functionality, performance, reliability, security, and/or any other of its specified quality attributes. Bertolino, in the Guide to the Software Engineering Body of Knowledge, gives a view of testing as a "dynamic process that executes a program on valued inputs". This view, as well as the definition of testing given in Chapter 1, suggest that in addition to detecting defects, testing is also a process used to evaluate software quality. The purpose of the former has been described in the previous paragraph. In the case of the latter, the tester executes the software using test cases to evaluate properties such as reliability, usability, maintainability, and level of performance. Test results are used to compare the actual properties of the software to those specified in the requirements document as quality goals. Deviations or failure to achieve quality goals must be addressed. The reader should keep in mind that testing can have a broader scope as described in test process improvement models such as the TMM and other quality models. Reviews and other static analysis techniques are included under the umbrella of testing in the models. These techniques, and how they relate to detecting defects and evaluating quality will be described in subsequent chapters of this text.

**Principle 2.** When the test objective is to detect defects, then a good test case is one that has a high probability of revealing a yet undetected defect(s).

Principle 2 supports careful test design and provides a criterion with which to evaluate test case design and the effectiveness of the testing effort when the objective is to detect defects. It requires the tester to consider the goal for each test case, that is, which specific type of defect is to be detected by the test case. In this way the tester approaches testing in the same way a

scientist approaches an experiment. In the case of the scientist there is a hypothesis involved that he/she wants to prove or disprove by means of the experiment. In the case of the tester, the hypothesis is related to the suspected occurrence of specific types of defects. The goal for the test is to prove/disprove the hypothesis, that is, determine if the specific defect is present/absent. Based on the hypothesis, test inputs are selected, correct outputs are determined, and the test is run. Results are analyzed to prove/disprove the hypothesis. The reader should realize that many resources are invested in a test, resources for designing the test cases, running the tests, and recording and analyzing results. A tester can justify the expenditure of the resources by careful test design so that principle 2 is supported.

Principle 3. Test results should be inspected meticulously.

Testers need to carefully inspect and interpret test results. Several erroneous and costly scenarios may occur if care is not taken.

For example:

• A failure may be overlooked, and the test may be granted a "pass" status when in reality the software has failed the test. Testing may continue based on erroneous test results. The defect may be revealed at some later stage of testing, but in that case it may be more costly and difficult to locate and repair.

• A failure may be suspected when in reality none exists. In this case the test may be granted a "fail" status. Much time and effort may be spent on trying to find the defect that does not exist. A careful re-examination of the test results could finally indicate that no failure has occurred.

• The outcome of a quality test may be misunderstood, resulting in unnecessary rework, or oversight of a critical problem.

Principle 4. A test case must contain the expected output or result.

It is often obvious to the novice tester that test inputs must be part of a test case. However, the test case is of no value unless there is an explicit statement of the expected outputs or results, for example, a specific variable value must be observed or a certain panel button that must light up.

Expected outputs allow the tester to determine (i) whether a defect has been revealed, and (ii) pass/fail status for the test. It is very important to have a correct statement of the output so that needless time is not spent due to misconceptions about the outcome of a test. The specification of test inputs and outputs should be part of test design activities. In the case of testing for quality evaluation, it is useful for quality goals to be expressed in quantitative terms in the requirements document if possible, so that testers are able to compare actual software attributes as determined by the tests with what was specified.

Principle 5. Test cases should be developed for both valid and invalid input conditions.

A tester must not assume that the software under test will always be provided with valid inputs. Inputs may be incorrect for several reasons.

For example, software users may have misunderstandings, or lack information about the nature of the inputs. They often make typographical errors even when complete/correct information is available. Devices may also provide invalid inputs due to erroneous conditions and malfunctions. Use of test cases that are based on invalid inputs is very useful for revealing defects since they may exercise the code in unexpected ways and identify unexpected software behaviour. Invalid inputs also help developers and testers evaluate the robustness of the software, that is, its ability to recover when unexpected events occur (in this case an erroneous input).

Principle 5 supports the need for the independent test group called for in Principle 7 for the following reason. The developer of a software component may be biased in the selection of test inputs for the component and specify only valid inputs in the test cases to demonstrate that the software works correctly. An independent tester is more apt to select invalid inputs as well.

**Principle 6.** The probability of the existence of additional defects in a software component is proportional to the number of defects already detected in that component.

What this principle says is that the higher the number of defects already detected in a component, the more likely it is to have additional defects when it undergoes further testing. For example, if there are two components A and B, and testers have found 20 defects in A and 3 defects in B, then the probability of the existence of additional defects in A is higher than B. This empirical observation may be due to several causes. Defects often occur in clusters and often in code that has a high degree of complexity

and is poorly designed. In the case of such components developers and testers need to decide whether to disregard the current version of the component and work on a redesign, or plan to expend additional testing resources on this component to insure it meets its requirements. This issue is especially important for components that implement mission or safety critical functions.

**Principle 7.** Testing should be carried out by a group that is independent of the development group.

This principle holds true for psychological as well as practical reasons. It is difficult for a developer to admit or conceive that software he/she has created and developed can be faulty. Testers must realize that (i) developers have a great deal of pride in their work, and (ii) on a practical level it may be difficult for them to conceptualize where defects could be found.

Even when tests fail, developers often have difficulty in locating the defects since their mental model of the code may overshadow their view of code as it exists in actuality. They may also have misconceptions or misunderstandings concerning the requirements and specifications relating to the software. The requirement for an independent testing group can be interpreted by an organization in several ways. The testing group could be implemented as a completely separate functional entity in the organization. Alternatively, testers could be members of a Software Quality Assurance

Group, or even be a specialized part of the development group, but in the latter case especially, they need the capability to be objective. Reporting to management that is separate from development can support their objectivity and independence. As a member of any of these groups, the principal duties and training of the testers should lie in testing rather than in development.

Finally, independence of the testing group does not call for an adversarial relationship between developers and testers. The testers should not play "gotcha" games with developers. The groups need to cooperate so that software of the highest quality is released to the customer.

Principle 8. Tests must be repeatable and reusable.

Principle 2 calls for a tester to view his/her work as similar to that of an experimental scientist. Principle 8 calls for experiments in the testing domain to require recording of the exact conditions of the test, any special events that occurred, equipment used, and a careful accounting of the results. This information is invaluable to the developers when the code is returned for debugging so that they can duplicate test conditions. It is also useful for tests that need to be repeated after defect repair. The repetition and reuse of tests is also necessary during regression test (the retesting of software that has been modified) in the case of a new release of the software. Scientists expect experiments to be repeatable by others, and testers should expect the same!

#### Principle 9. Testing should be planned.

Test plans should be developed for each level of testing, and objectives for each level should be described in the associated plan. The objectives should be stated as quantitatively as possible. Plans, with their precisely specified objectives, are necessary to ensure that adequate time and resources are allocated for testing tasks, and that testing can be monitored and managed. Test planning activities should be carried out throughout the software life cycle (Principle 10). Test planning must be coordinated with project planning. The test manager and project manager must work together to coordinate activities. Testers cannot plan to test a component on a given date unless the developers have it available on that date. Test risks must be evaluated.

For example, how probable are delays in delivery of software components, which components are likely to be complex and difficult to test, do the testers need extra training with new tools? A test plan template must be available to the test manager to guide development of the plan according to organizational policies and standards. Careful test planning avoids wasteful "throwaway" tests and unproductive and unplanned "test–patch–retest" cycles that often lead to poor-quality software and the inability to deliver software on time and within budget.

Principle 10. Testing activities should be integrated into the software life cycle.

It is no longer feasible to postpone testing activities until after the code has been written. Test planning activities as supported by Principle 10, should be integrated into the software life cycle starting as early as in the requirements analysis phase, and continue on throughout the software life cycle in parallel with development activities. In addition to test planning, some other types of testing activities such as usability testing can also be carried out early in the life cycle by using prototypes. These activities can continue on until the software is delivered to the users. Organizations can use process models like the V-model or any others that support the integration of test activities into the software life cycle [11].

Principle 11. Testing is a creative and challenging task [12].

Difficulties and challenges for the tester include the following:

- A tester needs to have comprehensive knowledge of the software engineering discipline.

- A tester needs to have knowledge from both experience and education as to how software is specified, designed, and developed.

- A tester needs to be able to manage many details.

- A tester needs to have knowledge of fault types and where faults of a certain type might occur in code constructs.

- A tester needs to reason like a scientist and propose hypotheses that relate to presence of specific types of defects.

- A tester needs to have a good grasp of the problem domain of the software that he/she is testing. Familiarly with a domain may come from educational, training, and work-related experiences.

- A tester needs to create and document test cases. To design the test cases the tester must select inputs often from a very wide domain.

Those selected should have the highest probability of revealing a defect (Principle 2). Familiarly with the domain is essential.

- A tester needs to design and record test procedures for running the tests.

- A tester needs to plan for testing and allocate the proper resources.

- A tester needs to execute the tests and is responsible for recording results.

- A tester needs to analyse test results and decide on success or failure for a test. This involves understanding and keeping track of an enormous amount of detailed information. A tester may also be required to collect and analyse test-related measurements.

- A tester needs to learn to use tools and keep abreast of the newest test tool advances.

- A tester needs to work and cooperate with requirements engineers, designers, and developers, and often must establish a working relationship with clients and users.

- A tester needs to be educated and trained in this specialized area and often will be required to update his/her knowledge on a regular basis due to changing technologies.

#### The Tester's Role in a Software Development Organization

Testing is sometimes erroneously viewed as a destructive activity. The tester's job is to reveal defects, find weak points, inconsistent behaviour, and circumstances where the software does not work as expected. As a tester you need to be comfortable with this role. Given the nature of the tester's tasks, you can see that it is difficult for developers to effectively test their own code (Principles 3 and 8). Developers view their own code as their creation, their "baby," and they think that nothing could possibly be wrong with it! This is not to say that testers and developers are adversaries. In fact, to be most effective as a tester requires extensive programming experience in order to understand how code is constructed, and where, and what kind of, defects are likely to occur. Your goal as a tester is to work with the developers to produce high-quality software that meets the customers' requirements. Teams of testers and developers are very common in industry, and projects should have an appropriate developer/tester ratio. The ratio will vary depending on available resources, type of project, and TMM level. For example, an embedded Realtime system needs to have a lower developer/tester ratio (for example, 2/1) than a simple data base application (4/1 may be suitable). At higher TMM levels where there is a well-defined testing group, the developer/ tester ratio would tend to be on the lower end (for example 2/1 versus 4/1) because of the availability of tester resources. Even in this case, the nature of the project and project scheduling issues would impact on the ratio.

In addition to cooperating with code developers, testers also need to work alongside with requirements engineers to ensure that requirements are testable, and to plan for system and acceptance test (clients are also involved in the latter). Testers also need to work with designers to plan for integration and unit test. In addition, test managers will need to cooperate with project managers in order to develop reasonable test plans,

and with upper management to provide input for the development and maintenance of organizational testing standards, polices, and goals. Finally, testers also need to cooperate with software quality assurance staff and software engineering process group members. In view of these requirements for multiple working relationships, communication and teamworking skills are necessary for a successful career as a tester. If you are employed by an organization that is assessed at TMM levels 1 or 2, you may find that there is no independent software test function in your organization. Testers in this case may be a part of the development group, but with special assignment to testing, or they may be part of the software quality assurance group. In fact, even at levels 3 and higher of the TMM the testers may not necessarily belong to a independent organizational entity, although that is the ideal case. However, testers should always have managerial independence from developers as described in Principle 8, and in the TMM at level 3. Testers are specialists, their main function is to plan, execute, record, and analyse tests. They do not debug software. When defects are detected during testing, software

should be returned to the developers who locate the defect and repair the code. The developers have a detailed understanding of the code, and are the best qualified staff to perform debugging. Finally, testers need the support of management. Developers, analysts, and marketing staff need to realize that testers add value to a software product in that they detect defects and evaluate quality as early as possible in the software life cycle. This ensures that developers release code with few or no defects, and that marketers can deliver software that satisfies the customers' requirements, and is reliable, usable, and correct. Low-defect software also has the benefit of reducing costs such as support calls, repairs to operational software, and ill will which may escalate into legal action due to customer dissatisfaction. In view of their essential role, testers need to have a positive view of their work. Management must support them in their efforts and recognize their contributions to the organization.

#### The Three-Step Process to Becoming a World-Class Testing Organization

The roadmap to become a world-class software testing organization is a simple threestep process, as follows:

- 1. Define or adopt a world-class software testing model.

- 2. Determine your organization's current level of software testing capabilities, competencies, and user satisfaction.

- 3. Develop and implement a plan to upgrade from your current capabilities, competencies, and user satisfaction to those in the world-class software testing model.

This three-step process requires you to compare your current capabilities, competencies, and user satisfaction against those of the world-class software testing model. This assessment will enable you to develop a baseline of your organization's performance. The plan that you develop will, over time, move that baseline from its current level of performance to a world-class level. Understanding the model for a world-class software testing organization and then comparing your organization will provide you with a plan for using the remainder of the material in this book.

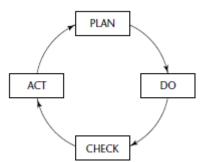

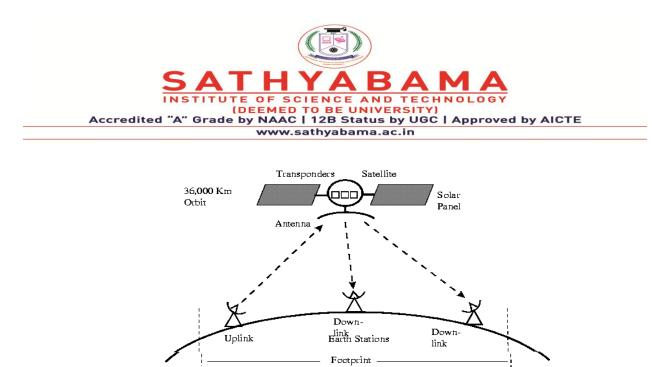

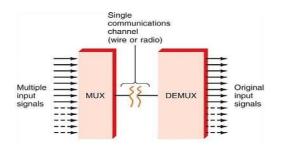

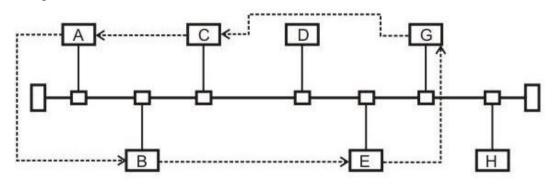

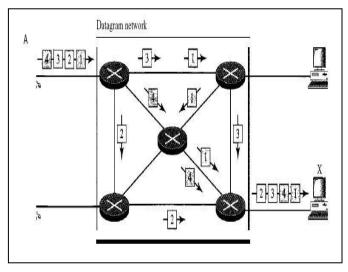

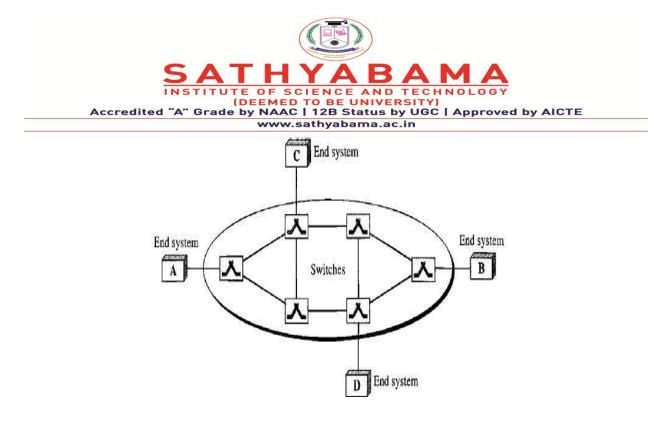

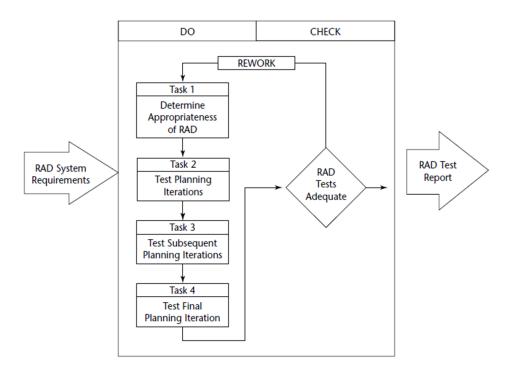

Software testing is an integral part of the software-development process, which comprises the following four components (see Figure 1-1):

- 1. Plan (P): Devise a plan. Define your objective and determine the strategy and supporting methods to achieve it. You should base the plan on an assessment of your current situation, and the strategy should clearly focus on the strategic initiatives/key units that will drive your improvement plan.

- 2. Do (D): Execute the plan. Create the conditions and perform the necessary training to execute the plan. Make sure everyone thoroughly understands the objectives and the plan. Teach workers the procedures and skills they need to fulfil the plan and thoroughly understand the job. Then perform the work according to these procedures.

- 3. Check (C): Check the results. Check to determine whether work is progressing according to the plan and whether the expected results are being obtained. Check for performance of the set procedures, changes in conditions, or abnormalities that may appear. As often as possible, compare the results of the work with the objectives.

- 4. Act (A): Take the necessary action. If your check-up reveals that the work is not being performed according to the plan or that results are not what you anticipated, devise measures to take appropriate actions.

Fig. 1.1. The four components of the software-development process.

Testing involves only the "check" component of the plan-do-check-act (PDCA) cycle. The software development team is responsible for the three remaining components. The development team plans the project and builds the software (the "do" component); the testers check to determine that the software meets the needs of the customers and users. If it does not, the testers report defects to the development team. It is the development team that makes the determination as to whether the uncovered defects are to be corrected.

The role of testing is to fulfil the check responsibilities assigned to the testers; it is not to determine whether software can be placed into production. That is the responsibility of the customers, users, and development team.

#### Step 1: Define a World-Class Software Testing Model

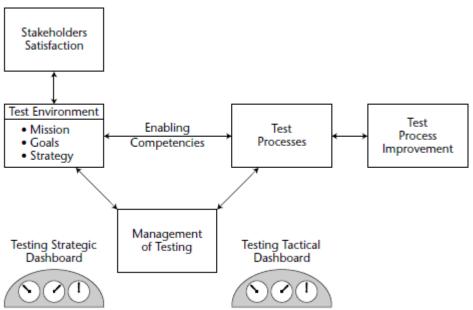

There is no generally accepted model for a world-class software testing organization. However, analysing the best testing organizations among the more than 1,000 IT organizations affiliated with the Quality Assurance Institute (QAI) enabled QAI to identify the attributes of the best software testing organizations (see Figure 1-2). Organizations that follow this model report more effective and efficient testing than those that do not.

Figure 1-2 Model of a world-class software testing organization.

The world-class software testing model includes

**Test environment.** The conditions that management has put into place that both enable and constrain how testing is performed. The test environment includes management support, resources, work processes, tools, motivation, and so forth.

Process to test a single software project. The standards and procedures testers use to test.

Tester competency. The skill sets needed to test software in a test environment.

The three self-assessments that follow are for the above three attributes of a world-class software testing organization. The three self-assessments in this chapter correspond to the preceding three attributes of a world-class software testing organization. The world-class model of a software testing organization focuses on stakeholder satisfaction. This assumes a greater role for a world-class software testing organization than just testing against documented software requirements. Chapter 2 defines the many roles that software testing can adopt; however, those roles include much more than testing documented software requirements. They include testing for quality factors such as ease of use, meeting testing schedules and budgets, and minimizing the risks involved with any software project. According to the world-class model, the following parties have a vested interest in software testing:

Software customer. The party or department that contracts for the software to be developed.

**Software user.** The individual or group that will use the software once it is placed into production. (Note: This may be the customer or it may be parties other than the customer.)

**Software developer.** The individual or group that receives the requirements from the software user or assists in writing them, designing, building, and maintaining the software, as needed.

**Development tester.** The individual or group that performs the test function within the software development group.

**IT management.** The individual or group with responsibility for fulfilling the information technology mission. Testing supports fulfilling that mission.

**Senior management.** The CEO of the organization and other senior executives who are responsible for fulfilling the organization mission. Information technology is an activity that supports fulfilling that mission.

**Auditor.** The individual or group responsible for evaluating the effectiveness, efficiency, and adequacy of controls in the information technology area. Testing is considered a control by the audit function.

**Project manager.** The individual responsible for managing the building, maintaining, and/or implementing of software.

The test mission, strategy, and environment must be focused on stakeholder satisfaction. The mission defines the testing objectives; the strategy defines how the mission will be accomplished; and the environment provides the culture, processes, and tools that are conducive to effective and efficient software testing.

The test processes are those step-by-step procedures that the testers will follow to accomplish their assigned tasks. Test processes executed by trained and competent

testers enable those testers to accomplish the defined test mission. The test processes need to be improved continually for two reasons: to make them more effective and efficient to use, and to incorporate updated approaches into testing new technologies and software development methodologies. The responsibility for ensuring that the execution of the test processes meets the defined test mission lies with management. Management must ensure that testers are following and can accomplish the test plan, and that the plan will, in fact, accomplish the test objectives. If not, management should modify the plan to meet those objectives.

Management and testers need tools to enable them to fulfil their responsibilities. Two very important tools are the testing strategic dashboard and the testing tactical dashboard. The *testing strategic dashboard* includes key indicators such as user satisfaction, staff competency, and the percent of tests completed. The *testing tactical dashboard* includes test indicators such as the number of requirements tested and percent correct, defects uncovered, defects corrected and uncorrected, and the schedule and budget status.

Management must ensure that if you meet the testing tactical key indicators, you will, in fact, meet the objectives defined by the strategic key indicators. Customizing the World-Class Model for Your Organization You can customize the world-class model for software testing by defining the attributes of each of its components (refer to Figure 1-2). The material in this book explains the attributes of all the components: stakeholder satisfaction, test mission, test management and enabling competencies are discussed in Part 2. The test processes are explained in Parts 3 and 4. Test process improvement is described in Part 5 of this book. As you read those parts of the book, you can customize those attributes based on the mission of your organization. For example, in describing a tester's competency, skill sets for testing COTS software and outsourced software will be listed. However, if your organization does not use COTS software or does not outsource the development of software, you would not need those skills in your testing staff. Likewise, if your testers are not responsible for testing security, you would not need a test processes for testing security.

The three self-assessments included in this chapter are based on the model in Figure 1-2. However, it is recognized that few testing organizations need all these testing capabilities and competencies. Therefore, you need to develop the model that is suited to your test mission.

#### **Step 2: Develop Baselines for Your Organization**

This section presents the following three self-assessment categories to enable you to compare your testing organization against the world-class model:

- 1. Assessing the test environment. This includes user satisfaction, management support, environment, planning, tools, test processes, measurement, quality control, and training.

- 2. Assessing the process for testing individual software projects. This category of assessment will assess your testing process against the seven-step process for testing individual software projects presented in Part 3 of this book.

- 3. Assessing the competencies of software testers. This self-assessment will be based on the 2006 Common Body of Knowledge (CBOK) developed by the Certification Board of the Software Certifications Organization. Each of the recommended ten competencies for software tester will be assessed. A more detailed assessment to be used in individuals to compare their specific test competencies against the 2006 CBOK is provided in Chapter 5.

#### **Assessment 1: Assessing the Test Environment**

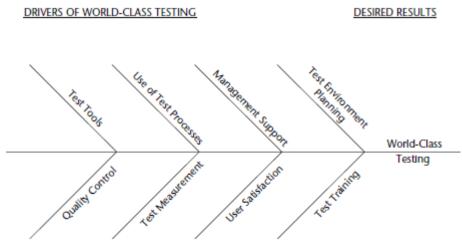

During the past 25 years, the Quality Assurance Institute (QAI) has been studying what makes software testing organizations successful. As a result, QAI has identified the following eight criteria:

Test environment planning Management support Use of test processes Test tools Quality control Test measurement User satisfaction Test training When these eight criteria are in place and working, the result is normally a worldclass testing organization.

The assessment process developed by QAI has five items to address within each of the eight criteria. The more of those items that are in place and working, the more likely that criteria will contribute to world-class testing. Figure 1-3 shows a cause-effect diagram indicating the areas to address, called *drivers*, which results in a world-class testing organization.

Figure 1-3 Overview of the testing environment.

## Software testing organizations can use the results of this assessment in any one of the following three ways:

- 1. To determine their current testing environmental status versus the environment of a world-class testing organization. The responses to the items address will indicate an organization's strengths and weaknesses compared to the environment of a world-class testing organization.

- 2. To develop the goal/objectives to accomplish becoming a world-class testing organization. QAI's world-class criteria indicate a profile of the environment of a world-class testing organization. Achieving those objectives can lead you to become a more effective software testing organization.

- 3. To develop an improvement plan

By doing the assessment, you will develop a Footprint Chart that shows where improvement is needed. Those criteria in which you are deficient become the means for improving the environment of your software testing organization.

#### Implementation Procedures

This practice involves the following four tasks:

- Build the assessment team.

- Complete the assessment questionnaires.

- Build the footprint chart.

- Assess the results.

#### **Building the Assessment Team**

The assessment team should combine people who in totality possess the knowledge of how your organization manages software testing. Before the team is established, the areas to address should be reviewed to determine the makeup of the team. It is recommended that a matrix be prepared with the seven assessment criteria on one dimension and the recommended assessment team on the other. The matrix should indicate which assessment team member is knowledgeable about each of the seven assessment criteria. Once all seven criteria have been associated with an assessment team member, it can be concluded that the team is adequate to perform the assessment.

#### **Completing the Assessment Questionnaire**

The assessment questionnaire in Work Paper 1-1 consists of eight categories, with five items to address for each category. A Yes or No response should be made, as follows:

- A Yes response means all of the following:

- Criteria items are documented and in place.

- Criteria items are understood by testers.

- Criteria items are widely used, where applicable.

- Criteria items have produced some possible results.

- A No response means any of the following:

- No formal item in place.

- Criteria items are applied differently for different test situations.

- No consistency as to when used or used very seldom.

- No tangible results were produced.

The assessment team should read aloud each item and then discuss how that item is addressed in their testing environment. The results should be recorded on Work Paper 1-1. The assessment team may also wish to record comments that clarify the response and/or to provide insight in how that area may be improved.

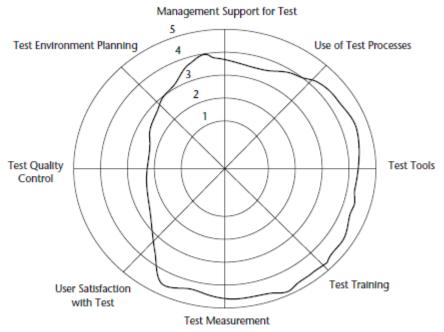

#### **Building the Footprint Chart**

For this task, you should transcribe the results of Work Paper 1-1 onto Work Paper 1-2. To do so, total the number of Yes responses for each criterion. Then place a dot on Work Paper 1-2 on the line representing the number of Yes responses. For example, if you have three Yes responses for test training, you should place a dot on the test training line at the intersection of the line representing three Yes responses. Adot should be marked on the line representing all seven criteria for the number of Yes responses. Then connect the dots with a line, resulting in what is called a "footprint" of the status of your testing environment versus the environment of a world-class testing organization.

#### Assessing the Results

You should make the following two assessments regarding the footprint developed on the Work Paper 1-2:

1. Assess the status of each criteria versus what that criteria should be in the worldclass testing environment. To do this, you need to look at the number of Yes responses you have recorded for each criterion versus a world-class organization, which would have five Yes responses. For example, three Yes responses for test training would indicate that improvements could be made in your test training process. The two items that received No responses are indications of where improvements are needed to move your test training activities to a world-class level.

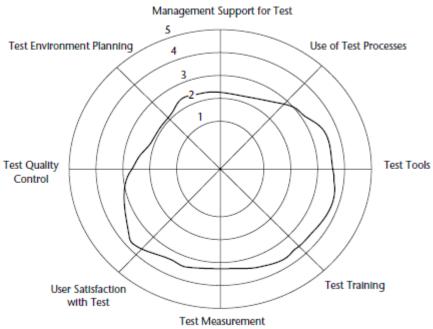

2. **Interpret your testing environment footprint chart.** The footprint in your Work Paper 1-2 provides an overview of your testing environment. Given the footprint, your assessment team should attempt to draw some conclusions about your testing environment. Three examples are given to help in drawing these conclusions, as shown in Figures 1-4, 1-5, and 1-6.

Figure 1-4 Example of a software testing organization using a test as a part of development.

Figure 1-5 Example of a testing organization using, but not enforcing, the test process.

Figure 1-6 Example of a testing organization practicing testing as an art.

#### Verifying the Assessment

The following list of questions, if responded to positively, would indicate that the assessment has been performed correctly:

- 1. Does the assessment team comprise the knowledge needed to answer all of the items to address within the seven criteria?

- 2. Are the individual assessors free from any bias that would cause them not to provide proper responses to the items to address?

- 3. Was there general consensus among the assessment team to the response for each item to address?

- 4. Are the items to address appropriate for your testing organization?

- 5. Have the items to address been properly totaled and posted to the Footprint Chart Work Paper?

- 6. Does the assessment team believe the Footprint Chart is representative of your testing environment?

- 7. Does your assessment team believe that if they improve the items to address, which have No responses, the testing organization will become more effective?

- 8. Does your organization believe that the overall assessment made is representative of your environment?

#### Assessment 2: Assessing the Capabilities of Your Existing Test Processes

To assess the capabilities of your existing test processes, follow the same procedure that you used to assess your test environment. Note that you should use the same team for both assessments. The only change you will need is to substitute self-assessment questionnaires in assessing the test environment process with the self-assessment questionnaires for assessing the test processes included in this section.

The assessment of test processes will be divided into the following seven categories:

- Preparing for a software testing project

- Conducting test planning

- Executing the test plan

- Conducting acceptance testing

- Analyzing test results and preparing reports

- Testing the installation of software

- Post-test analysis

Note that these seven categories of test processes correspond to a seven-step software testing process presented in Part 3 of this book. Thus, each assessment will help you determine your strengths and weaknesses in each of the seven steps of the proposed software testing process. To conduct this self-assessment, answer the questionnaire in Work Paper 1-3 and post your results to Work Paper 1-4, as described in the preceding section.

#### **Assessment 3: Assessing the Competency of Your Testers**

This practice will enable you to assess your testing competencies against the ten skill categories in the Common Body of Knowledge (CBOK) for the Certified Software Tester (CSTE) certificate. At the conclusion of the assessment, you will develop a Foot print Chart that shows your competencies against the skill categories needed to become a CSTE. You can use the results to design a program for improving your personal test competencies.

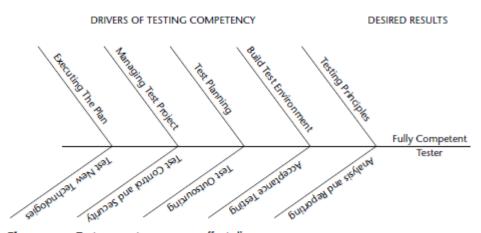

Figure 1-7 shows a cause-effect diagram indicating the areas of competency assessment. In the diagram these are called the drivers that result in becoming a fully competent software tester. The drivers are, in fact, the ten CBOK skill categories.