# SCHOOL OF ELECTRICAL & ELECTRONICS ENGINEERING DEPARTMENT OF ELECTRONICS & INSTRUMENTATION

UNIT-I

EMBEDDED SYSTEM DESIGN- SBMA5201

## **ARM ARCHITECTURE**

ARM Architecture- ARM Design Philosophy, Registers, Program Status Register, Instruction Pipeline, Interrupts and Vector Table, Architecture Revision, ARM Processor Families.

#### 1. History of the ARM Processor

Developed the first ARM Processor (Acorn RISC Machine) in 1985 at Acorn Computers Limited.

• Established a new company named Advanced RISC Machine Limited and developed ARM6.

• Continuation of the architecture enhancements from the original architecture

#### 2.Features of the ARM Processor

Incorporate features of Berkeley RISC design

- -a large register file

- -a load/store architecture

- -uniform and fixed length instruction field

-simple addressing mode

- Other ARM architecture features

- -Arithmetic Logic Unit and barrel shifter

- -auto increment and decrement addressing mode

- -conditional execution of instructions

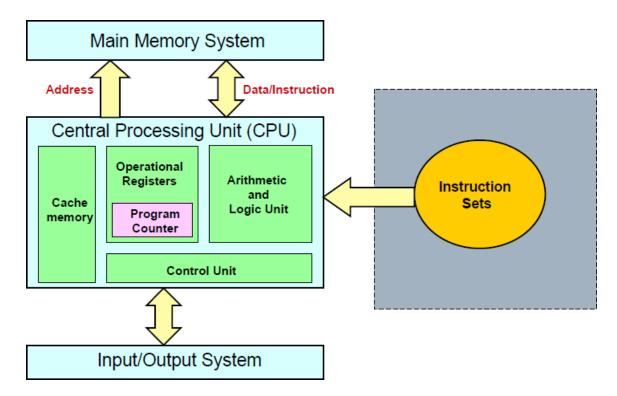

- Based on Von Neumann Architecture or Harvard Architecture

## **3.**The Evolution of the ARM architecture:

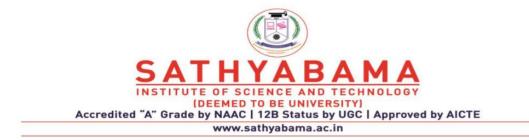

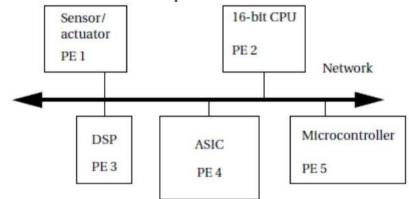

Figure 1.1 ARM Families

Architecture V1 was implemented only in the ARM1 CPU and was not utilized in a commercial product. Architecture V2 was the basis for the first shipped processors. These two architectures were developed by Acorn Computers before ARM became a company in 1990.

After that introduced ARM the Architecture V3, which included many changes over its predecessors .These changes resulted in an extremely small and power-efficient processor suitable for embedded systems .Architecture V4, co-developed by ARM and Digital Electronics Corporation, resulted in the Strong ARM series of processors. These processors are very performance-centric and do not include the on chip debug extensions.

This architecture was further developed to include the Thumb 16-bitinstruction set architecture enabling a 32-bit processor to utilize a 16-bit system. Today, ARM only licenses cores based on Architecture V4T or above.

The latest architectures, version 5TE and 5TEJ, embody added instructions for DSP applications and the Jazelle-Java extensions, respectively.

Currently, the ARM9E and 10E family of processors are theonly implementations of these architectures. Details on these architectures and cores will be provided later in the course.

#### **4.Architecture basics**

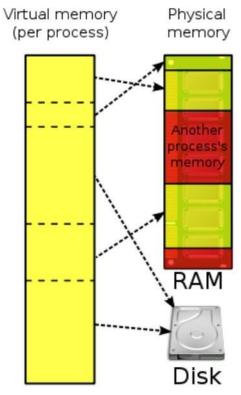

ARM cores use a 32-bit, Load-Store RISC architecture. That means that the core cannot directly manipulate the memory. All data manipulation must be done by loading registers with information located in memory, performing the data operation and then storing the value back to memory. There are 37 total registers in the processor. However, that number is split among seven different processor modes. The seven processor modes are used to run user tasks, an operating system, and to efficiently handle exceptions such as interrupts. Some of the registers with in each mode are reserved for specific use by the core, while most are available for general use. The reserved registers that are used by the core for specific functions are r13 is commonly used as the stack pointer (SP), r14 as a link register (LR), r15as a program counter (PC), the Current Program Status Register (CPSR), and the Saved Program Status Register (SPSR).

The SPSR and the CPSR contain the status and control bits specific to the properties the processor core is operating under. These properties define the operating mode, ALU status flags, interrupt disable/enable flags and whether the core is operating in 32-bit ARM or 16-bit Thumb state.

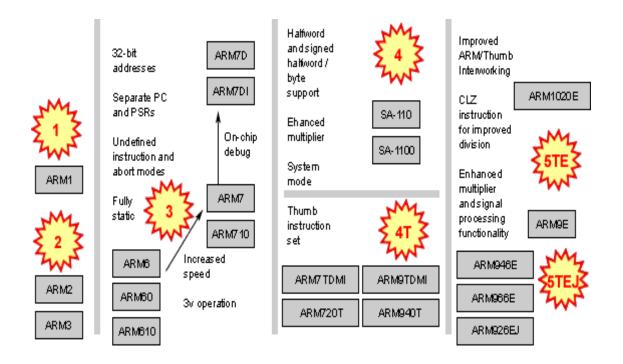

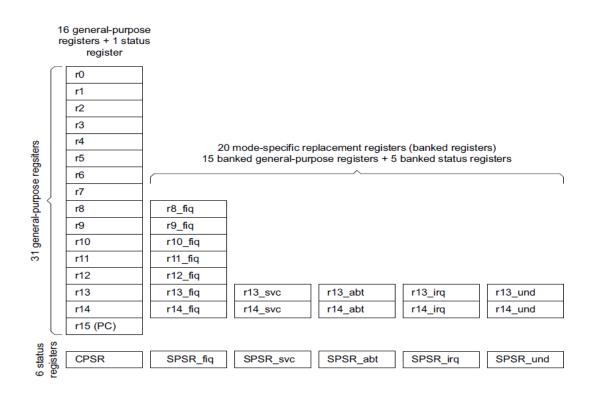

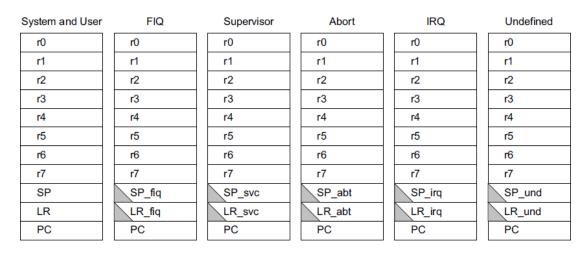

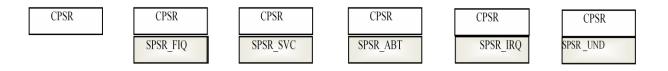

There are 37 total registers divided among seven different processor modes. Figure 09 shows thebank of registers visible in each mode .User mode, the only non-privileged mode, has the least number of total registers visible. It has noSPSR and limited access to the CPSR. FIQ and IRQ are the two interrupt modes of the CPU

Note: System mode uses the User mode register set

#### Figure 1.2 Different modes of ARM

There are 37 total registers divided among seven different processor modes. Figure 02 shows the bank of registers visible in each mode. User mode, the only non-privileged mode, has the least number of total registers visible. It has no SPSR and limited

access to the CPSR. FIQ and IRQ are the two interrupt modes of the CPU.Supervisor mode is the default mode of the processor on start up or reset. Undefined mode traps unknown or illegal instructions when they are passed through the pipeline. Abort mode traps illegal memory accesses as a result of fetching instructions or accessing data.

Finally, system mode, which uses the user mode bank of registers, was introduced to provide an additional privileged mode when dealing with nested interrupts.

Each additional mode offers unique registers that are available for use by exception handling routines. These additional registers are the minimum number of registers required to preserve the state of the processor, save the location in code, and switch between modes.

FIQ mode, however, has an additional five banked registers to provide more flexibility and higher performance when handling critical interrupts.

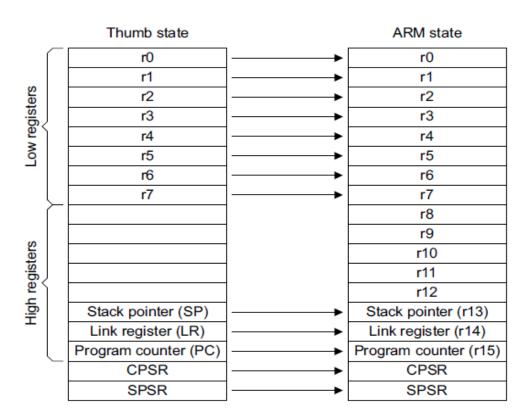

When the ARM core is in Thumb state, the registers banks are split into low and high register domains. The majority of instructions in Thumb state have a 3-bit register specifier. As a result, these instructions can only access the low registers in Thumb, R0 through R7. The high registers,

R8through R15, have more restricted use. Only a few instructions have access to these registers. **TDMI**

stands for:

• Thumb, which is a 16-bit instruction set extension to the 32-bit ARM architecture, referred as states of the processor.

• "D" and "I" together comprise the on-chip debug facilities offered on all ARM cores. These stand for the Debug signals and Embedded ICE logic, respectively.

• The M signifies the support for 64-bit results and an enhanced multiplier, resulting inhigher performance. This multiplier is now standard on all ARMv4 architectures and\above.

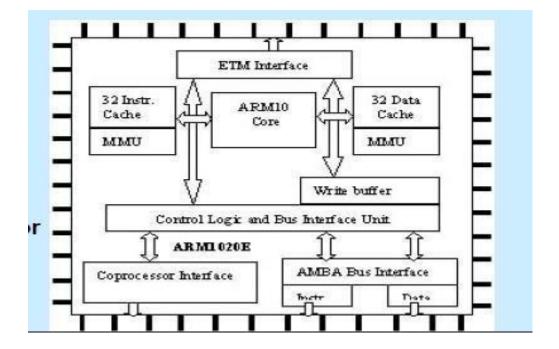

#### 5. Thumb 16-bit Instructions

With growing code and data size, memory contributes to the system cost. The need to reduce memorycost leads to smaller code size and the use of narrower memory. Therefore ARM developed a modified instruction set to give market-leading code density for compiled standard C language.

There is also the problem of performance loss due to using a narrow memory path, such as a 16-bitmemory path with a 32-bit processor.

The processor must take two memory access cycles to fetch an instruction or read and write data. To address this issue, ARM introduced another set of reduced 16-bit instructions labeled Thumb, based on the standard ARM 32-bit instruction set.

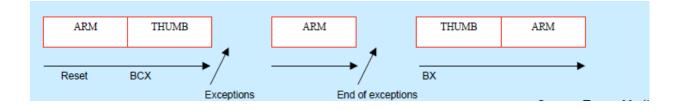

For Thumb to be used, the processor must go through a change of state from ARM to Thumb in order to begin executing 16-bit code. This is because the default state of the core is ARM. Therefore, every application must have code at boot up that is written in ARM. If the application code is to be compiled entirely for Thumb, then the segment of ARM boot code must change the state of the processor. Once this is done, 16-bit instructions are fetched seamlessly into the pipeline without any result.

It is important to note that the architecture remains the same. The instruction set is actually a reduced set of the ARM instruction set and only the instructions are 16-bit; everything else in the core still operates as 32-bit. An application code compiled in Thumb is 30% smaller on average than the same code compiled in ARM and normally 30% faster when using narrow 16-bit memory systems.

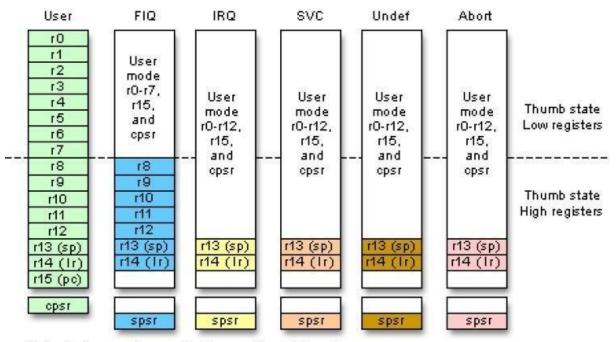

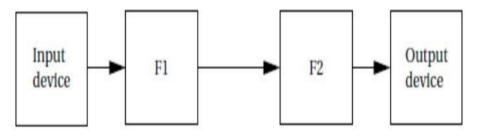

Figure 1.3 Register Bank

Figure 1.3 shows the register bank in the center of the diagram, plus the required address bus and data bus. The multiplier, in-line barrel shifter, and ALU are also shown. In addition, the diagram illustrates the in-line decompression process of Thumb instructions while in the decode stage of the pipeline. This process creates a 32-bit ARM equivalent instruction from the 16-bit Thumb instruction, decodes the instruction, and passes it on to the execute stage.

## 6.ARM design philosophy

Small processor for lower power consumption (for embedded system)

• High code density for limited memory and Physical size restrictions

• The ability to use slow and low-cost memory

• Reduced die size for reducing manufacture cost and accommodating more peripherals

#### 6.1 Registers

ARM has 37 registers all of which are 32-bits long. 1 dedicated program counter  $\Box$  1 dedicated current program status register  $\Box$  5 dedicated saved program status registers  $\Box$  30 general purpose registers  $\Box$  The current processor mode governs which of several banks is  $\Box$  accessible. Each mode can access a particular set of r0-r12 registers  $\Box$  a particular r13 (the stack pointer, sp) and r14 (the link register, lr)  $\Box$  the program counter, r15 (pc)  $\Box$  the current program status register, cpsr  $\Box$  Privileged modes (except System) can also access a particular spsr (saved program status reg

The ARM1136JF-S processor has a total of 37 registers:

• 31 general-purpose 32-bit registers

• six 32-bit status registers. These registers are not all accessible at the same time. The processor state and operating mode determine which registers are available to the programmer

The ARM state register set In ARM state, 16 general registers and one or two status registers are accessible at any time. In privileged modes, mode-specific banked registers become available.

The ARM state register set contains 16 directly-accessible registers, r0-r15. Another register, the Current Program Status Register (CPSR), contains condition code flags, status bits, and current mode bits. Registers r0-r13 are general-purpose registers used to hold either data or address values. Registers r14, r15, and the SPSR have the following special functions

Link Register Register r14 is used as the subroutine Link Register (LR). Register r14 receives the return address when a Branch with Link (BL or BLX) instruction is executed. You can treat r14 as a general-purpose register at all other times. The corresponding banked registers r14\_svc, r14\_irq, r14\_fiq, r14\_abt, and r14\_und are similarly used to hold the return values when interrupts and exceptions arise, or when BL or BLX instructions are executed within interrupt or exception routines.

Program Counter Register r15 holds the PC:

- in ARM state this is word-aligned

- in Thumb state this is halfword-aligned

- in Java state this is byte-aligned. Saved Program Status Register

In privileged modes, another register, the Saved Program Status Register (SPSR), is accessible. This contains the condition code flags, status bits, and current mode bits saved as a result of the exception that caused entry to the current mode.

Banked registers have a mode identifier that indicates which mode they relate to. These mode identifiers are listed in Table **Register mode identifiers**

| Mode           | Mode identifier  |

|----------------|------------------|

| User           | usr <sup>a</sup> |

| Fast interrupt | fiq              |

| Interrupt      | irq              |

| Supervisor     | svc              |

| Abort          | abt              |

| System         | usr <sup>a</sup> |

| Undefined      | und              |

|                |                  |

a. The usr identifier is usually omitted from register names. It is only used in descriptions where the User or System mode register is specifically accessed from another operating mode.

FIQ mode has seven banked registers mapped to r8-r14 ( $r8_fiq-r14_fiq$ ). As a result many FIQ handlers do not have to save any

registers. The Supervisor, Abort, IRQ, and Undefined modes each have alternative mode-specific registers mapped to r13 and r14, permitting a private stack pointer and link register foreach mode

| System and User | FIQ      | Supervisor | Abort    | IRQ        | Undefined  |

|-----------------|----------|------------|----------|------------|------------|

| r0              | r0       | r0         | r0       | r0         | r0         |

| r1              | r1       | r1         | r1       | r1         | r1         |

| r2              | r2       | r2         | r2       | r2         | r2         |

| r3              | r3       | r3         | r3       | r3         | r3         |

| r4              | r4       | r4         | r4       | r4         | r4         |

| r5              | r5       | <b>r</b> 5 | r5       | r5         | <b>r</b> 5 |

| r6              | r6       | r6         | r6       | r6         | r6         |

| r7              | r7       | r7         | r7       | r7         | r7         |

| r8              | r8_fiq   | r8         | r8       | r8         | r8         |

| r9              | r9_fiq   | <b>r</b> 9 | r9       | <b>r</b> 9 | <b>r</b> 9 |

| r10             | r10_fiq  | r10        | r10      | r10        | r10        |

| r11             | r11_fiq  | r11        | r11      | r11        | r11        |

| r12             | r12_fiq  | r12        | r12      | r12        | r12        |

| r13             | r13_fiq  | r13_svc    | r13_abt  | r13_irq    | r13_und    |

| r14             | r14_fiq  | r14_svc    | r14_abt  | r14_irq    | r14_und    |

| r15             | r15 (PC) | r15 (PC)   | r15 (PC) | r15 (PC)   | r15 (PC)   |

#### ARM state general registers and program counter

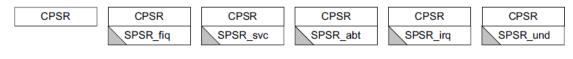

#### ARM state program status registers

= banked register

Figure 1.4 register set showing banked registers

Figure 1.5 ARM register

## 7. Thumb state register set

The Thumb state register set is a subset of the ARM state set. The programmer has direct access to:

- Eight general registers, r0-r7

- The PC

- A stack pointer, SP (ARM r13)

- An LR (ARM r14)

- The CPSR.

There are banked SPs, LRs, and SPSRs for each privileged mode.

#### Thumb state general registers and program counter

Thumb state program status registers

= banked register

#### 7.1 Accessing high registers in Thumb state

In Thumb state, the high registers, r8–r15, are not part of the standard register set. You can use special variants of the MOV instruction to transfer a value from a low register, in the range r0–r7, to a high register, and from a high register to a low register. The CMP instruction enables you to compare high register values with low register values. The ADD instruction enables you to add high register values to low register values.

## 7.2 ARM state and Thumb state registers relationship

Figure 1. 2-1.6 shows the relationships between the Thumb state and ARM state registers

Figure 2-6 ARM state and Thumb state registers relationship

Registers r0-r7 are known as the low registers. Registers r8-r15 are

known as the high registers.

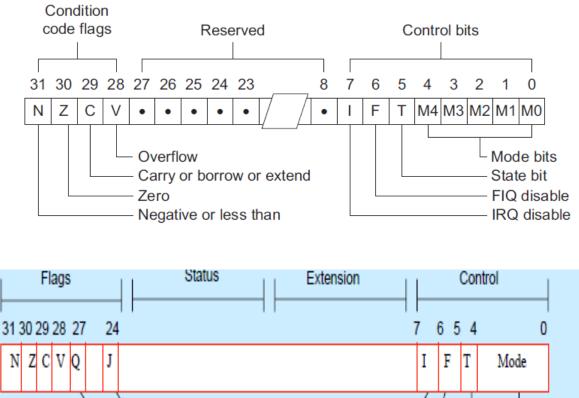

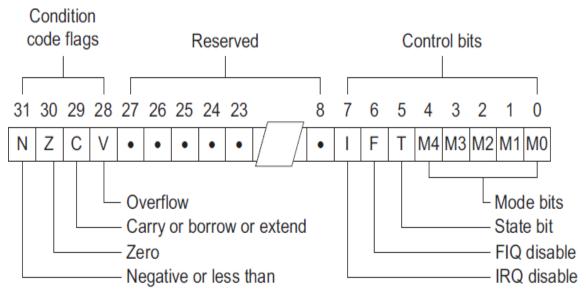

7.3 The program status registers

program status registers:

- hold the condition code flags

- control the enabling and disabling of interrupts

- set the processor operating mode.

The arrangement of bits is shown in Figure

N=Negative, Z=Zero, C=Carry, V= oVerflow

Figure 1.7 program status registers

#### 7.4 The condition code flags

The N, Z, C, and V bits are the condition code flags, You can set these bits by arithmeticand logical operations. The flags can also be set by MSR and LDM instructions.

TheARM7TDMI-S tests these flags to determine whether to execute an instruction.

All instructions can execute conditionally in ARM state. In Thumb state, only the Branch instruction can be executed conditionally

#### 7.5 The control bits

The bottom eight bits of a PSR are known collectively as the control bits. They are the:

- Interrupt disable bits

- T bit

- Mode bits.

The control bits change when an exception occurs. When the processor is operating in a privileged mode, software can manipulate these bits.

#### 7.6 Interrupt disable bits

The I and F bits are the interrupt disable bits:

- when the I bit is set, IRQ interrupts are disabled

- when the F bit is set, FIQ interrupts are disabled.

- 7.7 T bit

The T bit reflects the operating state:

- when the T bit is set, the processor is executing in Thumb state

- when the T bit is clear, the processor executing in ARM state. The operating state is reflected by the **CPTBIT** external signal.

#### 7.8 Mode bits

The M4, M3, M2, M1, and M0 bits (M[4:0]) are the mode bits. These bits determine the processor operating mode . Not all combinations of the mode bits define a valid processor mode, so take care to use only the bit combinations shown

#### 7.9 Reserved bits

The remaining bits in the PSRs are unused but are reserved. When changing a PSR flag or control bits make sure that these reserved bits are not altered. Also, make sure that your program does not rely on reserved bits containing specific values because future processors might have these bits set to one or zero

The ARM7TDMI-S is a member of the ARM family of general- purpose 32-bit microprocessors. The ARM family offers high performance for very low power consumption and gate count. The ARM architecture is based on Reduced Instruction Set Computer (RISC) principles. The RISC instruction set, and related decode mechanism are much simpler than those of Complex Instruction Set Computer (CISC) designs. This simplicity gives: • a high

Instruction throughput

- an excellent real-time interrupt response

- a small, cost-effective, processor macrocell.

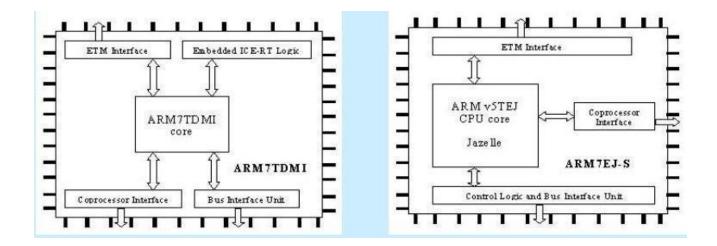

## 8. The instruction pipeline

The ARM7TDMI-S uses a pipeline to increase the speed of the flow of instructions to the processor. This allows several operations to take place simultaneously, and the processing, and memory systems to operate continuously.

A three-stage pipeline is used, so instructions are executed in three stages:

- Fetch

- Decode

- Execute.

The three-stage pipeline is shown in Figure .

| ARM    | Thumb  |         |                                                                                                                                                         |

|--------|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC     | PC     | Fetch   | The instruction is fetched from memory                                                                                                                  |

| PC-4   | PC - 2 | Decode  | The registers used in the instruction are decoded                                                                                                       |

| PC - 8 | PC - 4 | Execute | The register(s) is (are) read from register bank<br>The shift and ALU operations are performed<br>The register(s) are written back to the register bank |

**8.1The Program Counter** (PC) points to the instruction being fetched rather than to the instruction being executed.

During normal operation, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory

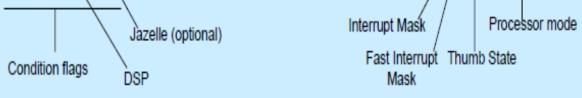

## 9. The ARM Processor Families (I)

The ARM7 Family

- □ 32-bit RISC Processor. Support three

- stage pipeline

- Uses Von Neumann Architecture.

Figure 1.8 ARM7TDMI

Figure 1.9 ARM7EJ-S

|            | Cache<br>size(Inst/<br>Data | Tightly<br>Coupled<br>Memory | Memory<br>Mgmt | Thumb | DSP | Jazelle |

|------------|-----------------------------|------------------------------|----------------|-------|-----|---------|

| ARM720T    | 8k unified                  | -                            | MMU            | Yes   | No  | No      |

| ARM7EJ-S   | -                           | -                            | -              | Yes   | Yes | Yes     |

| ARM7TDMI   | -                           | -                            | -              | Yes   | No  | No      |

| ARM7TDMI-S | -                           | -                            | -              | Yes   | No  | No      |

Widely used in many applications such as palmtop computers, portable instruments, smart card.

## 9.1 The ARM Processor Families (II)

The ARM9 Family

- □ 32-bit RISC Processor with ARM and Thumb instruction sets Supports five-stage pipeline

- Uses harvard architecture

Uses Harvard architecture

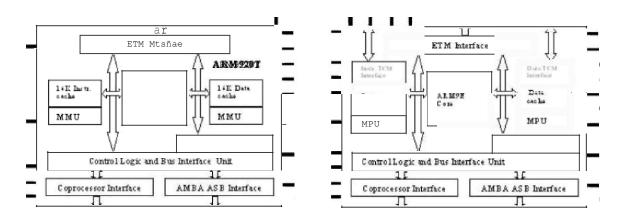

Figure 1.10 ARM920T Processor

Characteristics of ARM9 Thumb Family

|         | Cache<br>size(Inst/Data) | Tightly<br>Coupled<br>Wemoy | Memory Mgmt | Thumb | DSP | Jazelle |

|---------|--------------------------|-----------------------------|-------------|-------|-----|---------|

| ARMD20T | 6hl6k                    |                             | \1\1U       | Yes   | No  | No      |

| ARMD22T | 8W8f                     |                             | \1\1U       | Yes   | No  | No      |

Characteristics of ARM9E Family

|                  | Cache<br>size(Inst/<br>Data) | Tightly<br>Couple<br>d<br>Memor<br>y | Memor<br>y<br>Mgmt | Thumb | DSP | Jazelle |

|------------------|------------------------------|--------------------------------------|--------------------|-------|-----|---------|

| ARI\1926EJ<br>-S | Variable                     | Yes                                  | MMU                | Yes   | Yes | Yes     |

| ARL1946E-<br>S   | Variable                     | Yes                                  | MPU                | Yes   | Yes | No      |

| ARL1966E-<br>S   |                              | Yes                                  |                    | Yes   | Yes | No      |

| ARL1968E—<br>S   | N.!a                         | Yes                                  | DMA                | Yes   | Yes | No      |

| ARL1996H-<br>S   |                              |                                      | MPU                | Yes   | Yes | No      |

Widely used in mobile phones, PDAs, digital cameras, automotive systems, industrial control systems.

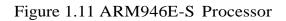

## 9.2 ARM Processor Families (III)

The ARM10 Family

☐ 32-bit RISC processor with ARM, Thumb and DSP instruction sets.

□ Supports six-stage Pipelines Uses

Harvard Architecture

Figure 1.11 ARM1020E Processor

# Characteristics of ARM10 family

|             | Cache<br>size(Inst<br>/Data) | Tightly<br>Coupled<br>Memory | Memory<br>Mgmt | Thumb | DSP | Jazelle |

|-------------|------------------------------|------------------------------|----------------|-------|-----|---------|

| ARM1020E    | 32k/32k                      | -                            | MMU            | Yes   | Yes | No      |

| ARM1022E    | 16k/16k                      | -                            | MMU            | Yes   | Yes | No      |

| ARM1026EJ-S | Variable                     | Yes                          | MMU or<br>MPU  | Yes   | Yes | Yes     |

Widely used in videophone, PDAs, set-top boxes, game console, digital video cameras, automotive and industrial control systems.

## 9.4 ARM PROCESSOR FAMILIES (IV)

The ARM11 Family

- $\square$  32-bit RISC processor with ARM, Thumb and DSP instruction sets.

- Uses Harvard Architecture.

- ☐ Supports eight-stage Pipelines except ARM1156T2 uses nine-stage pipeline.

- ☐ Widely used in automotive and industrial control systems, 3D graphics, security critical applications

|                | Cache<br>size(Inst<br>/Data) | Tightly<br>Coupled<br>Memory | Memory Mgmt   | Thumb | DSP | Jazelle |

|----------------|------------------------------|------------------------------|---------------|-------|-----|---------|

| ARM11 MPCore   | Variable                     | Yes                          | MMU+cache     | Yes   | Yes | Yes     |

| ARM1136J(F)-S  | Variable                     | Yes                          | MMU           | Yes   | Yes | Yes     |

| ARM1156T2(F)-S | Variable                     | Yes                          | MPU           | Yes   | Yes | No      |

| ARM1176JZ(F)-S | Varaible                     | Yes                          | MMU+TrustZone | Yes   | Yes | Yes     |

## 10. Characteristics of ARM11 family

#### **10.1ARM Pipelines**

Pipeline mechanism to increase execution speed  $\Box$

•The pipeline design of each processor family is different

## **10.2 ARM Processor Modes**

Unprivileged mode

User mode Privileged mode Abort mode

Fast Interrupt Request mode Interrupt

Request mode Supervisor mode

System mode

Undefined mode

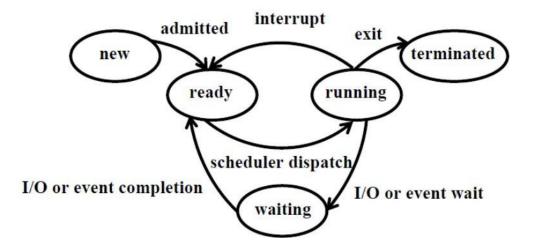

#### 10.3Exceptions

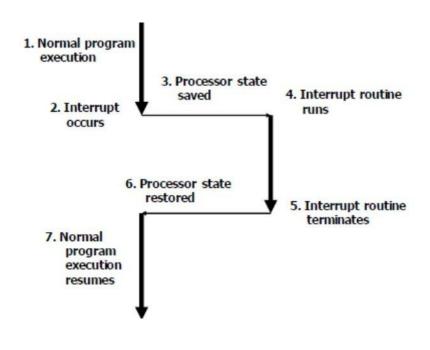

Exceptions are taken whenever the normal flow of a program must temporarily halt, for example, to service an interrupt from a peripheral. Before attempting to handle an exception, the processor preserves the critical parts of the current processor state so that the original program can resume when the handler routine has finished

#### **10.4 Exceptions and Interrupts**

The ARM processor can work in one of many operating modes. So far we have only considered user mode, which is the "normal" mode of operation.

The processor can also enter "privileged" operating modes which are used to handle exceptions and SWIs

The Current Processor Status Register CPSR has 5 bits [bit4:0] to indicate which mode the processor is in:-

| CPSR[4:0] | Mode   | Use                                       | Registers |

|-----------|--------|-------------------------------------------|-----------|

| 10000     | User   | Normal user code                          | user      |

| 10001     | FIQ    | Processing fast interrupts                | _fiq      |

| 10010     | IRQ    | Processing standard interrupts            | _irq      |

| 10011     | SVC    | Processing software interrupts (SWIs)     | _svc      |

| 10111     | Abort  | Processing memory faults                  | _abt      |

| 11011     | Undef  | Handling undefined instruction traps      | _und      |

| 11111     | System | Running privileged operating system tasks | user      |

#### 10.5 How are exceptions generated

By default, the processor is usually in user mode

- ☐ It enters one of the exception modes when unexpected events occur.

- $\square$  There are three different types of exceptions (some are called interrupts):-

- ➢ As a direct result of executing an instruction, such as: Software Interrupt

- □ Instruction (SWI)

- $\Box$  Undefined or illegal instruction

- $\square$  Memory error during fetching an instruction

- ➢ As a side-effect of an instruction, such as: Memory fault during

- data read/write from memory Arithmetic error (e.g. divide by zero)

- ➢ As a result of external hardware signals, such as: Reset

- Fast Interrupt (FIQ) Normal

- Interrupt (IRQ)

## **10.6 Shadow Registers**

As the processor enters an exception mode, some new registers are automatically switched in:-

For example, an external event (such as movement of the mouse) occurs that generates a Fast Interrupt (on the FIQ pin), the processor enters FIQ operating mode. It sees the same r0 -

r7 as before, but sees a new set of r8 - r14, and in addition, an extra register called the Saved Processor Status Register (SPSR) stores the value of the CPSR. By swapping to some new registers, it makes it easier for the programmer to preserve the state of the processor.

For example, during FIQ mode, r8 - r14 can be used freely. On returning back to user mode, the original values of r8 - r14 will be automatically restored.

#### 10.7 What happens when an exception occurs

ARM completes current instruction as best it can. It departs from current instruction sequence to handle the exception by performing the following steps:-

1. It changes the operating mode corresponding to the particular exception.

**2.** It saves the current PC in the r14 corresponding to the new mode. For example, if FIQ occurs, the PC value is stored in r14(FIQ).

**3.** It saves the old value of CPSR in the Saved Processor Status Register of the new mode.

4. It disables exceptions of lower priority (to be considered later).

**5.** It forces the PC to a new value corresponding to the exception. This is effectively a forced jump to the Exception Handler or Interrupt Service Routine.

#### 10.8 Where is the exception handler routine

Exceptions can be viewed as "forced" subroutine calls. When and if an exception occurs is not predictable (unless it is a SWI exception). A unique address is pre-defined for each exception handler (IRQ, FIQ, etc), and a branch is made to this address. The address to which the processor is forced to branch to is called the exception/interrupt vector.

#### **10.9 Exception vector addresses**

Each vector (except FIQ) is 4 bytes long (i.e. one instruction) You put a branch instruction at this address: B exception handler FIQ is special in two ways:-

**1.** You can put the actual FIQ handler (also called Fast Interrupt Service Routine) at 0x0000001C onwards, because FIQ vector occupies the highest address

2. FIQ has many more shadow registers. So you don't have to save as many registers on the stack as other exceptions -faster.

| Exception                                       | Mo de | Vector address |

|-------------------------------------------------|-------|----------------|

| Reset                                           | SVC   | 0x00000000     |

| Undefined instruction                           | UND   | 0x00000004     |

| Software interrupt (SWI)                        | SVC   | 0x0000008      |

| Prefetch abort (instruction fetch memory fault) | Abort | 0x0000000C     |

| Data abort (data access memory fault)           | Abort | 0x00000010     |

| IRQ (normal interrupt)                          | IRQ   | 0x00000018     |

| FIQ (fast interrupt)                            | FIQ   | 0x0000001C     |

#### **10.10Exception Return**

Once the exception has been handled (by the exception handler),

the user task is resumed.

The handler program (or Interrupt Service Routine) must restore the user state exactly as it was before the exception occurred:

1. Any modified user registers must be restored from the handlers stack

2. The CPSR must be restored from the appropriate SPSR

**3.** PC must be changed back to the instruction address in theuser instruction stream

Steps 1 and 3 are done by user, step 2 by the processor Restoring registers from the stack would be the same as in the case of subroutine Restoring PC value is more complicated. The exact way to do it

depends on which exception you are returning from.

#### **10.11 Exception Return**

Once the exception has been handled (by the exception handler), the user task is resumed. The handler program (or Interrupt Service Routine) must restore the user state exactly as it was before the exception occurred

- 1. Any modified user registers must be restored from the handler"s stack

- 2. The CPSR must be restored from the appropriate SPSR

PC must be changed back to the instruction address in the user instruction stream Steps 1 and 3 are done by user, step 2 by the processor

Restoring registers from the stack would be the same as in the case of subroutines Restoring PC value is more complicated. The exact way to do it depends on which exception you are returning from.

Remember that the return address was saved in r14 before entering the exception handler.

To return from a SWI or undefined instruction trap, use: MOVS pc, r14

To return from an IRQ, FIQ or prefetch abort, use: SUBS pc, r14, #4

To return from a data abort to retry the data access, use: SUBS pc, r14, #8 If the destination register is the PC, the "S' modifier does NOT mean "set the flags", but "restore the CPSR"

The differences between these three methods of return is due to the pipeline architecture of the ARM processor. The PC value stored in r14 can be one or two instructions ahead due to the instruction prefetch pipeline.

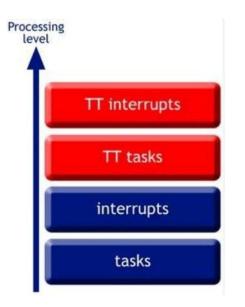

#### **10.12Exception Priorities**

Since exceptions can arise at the same time, a priority order has to be clearly defined. For the

ARM processor this is: Reset (highest priority)

Data abort (i.e. Memory fault in read/write data) Fast Interrupt

Request (FIQ)

Normal Interrupt Request (IRQ) Prefetch

abort

#### 10.13 Software Interrupt (SWI), undefined instruction

Consider the case of a FIQ and an IRQ occurring at the same time. The processor will process the FIQ handler first and "remember" that there is IRQ pending. On return from FIQ, the process will immediately go to the IRQ handler.

## **11. Interrupts**

The processor has two interrupt inputs, for normal interrupts (**nIRQ**) and fast interrupts (**nFIQ**). Each interrupt pin, when asserted and not masked, causes the processor to take the appropriate type of interrupt exception. The CPSR.F and CPSR.I bits control masking of fast and normal interrupts respectively.

A number of features exist to improve the interrupt latency, that is, the time taken between the assertion of the interrupt input and the execution of the interrupt handler. By default, the processor uses the *Low Interrupt Latency* (LIL) behaviors introduced in version 6

and later of the ARM architecture. The processor also has a port for connection of a *Vectored Interrupt Controller* (VIC), and supports *Non-Maskable Fast Interrupts* (NMFI).

The following subsections describe interrupts:

- Interrupt request

- Fast interrupt request

- Non-maskable fast interrupts

- Low interrupt latency

- Interrupt controller.

## **11.1 Interrupt request**

The IRQ exception is a normal interrupt caused by a LOW level on the **nIRQ** input. An IRQ has a lower priority than an FIQ, and is masked on entry to an FIQ sequence. You must ensure that the **nIRQ** input is held LOW until the processor acknowledges the interrupt request, either from the VIC interface or the software handler.

Irrespective of whether the exception is taken from ARM state or Thumb state, an IRQ handler returns from the interrupt by executing:

SUBS PC, R14\_irq, #4

You can disable IRQ exceptions within a Privileged mode by setting the CPSR.I bit to b1. See *Program status registers*. IRQ interrupts are automatically disabled when an IRQ occurs, by setting the CPSR.I bit. You can use nested interrupts but it is up to you to save any corruptible registers and to re-enable IRQs by clearing the CPSR.I bit.

#### **11.2 Fast interrupt request**

The *Fast Interrupt Request* (FIQ) reduces the execution time of the exception handler relative to a normal interrupt. FIQ mode has eight private registers to reduce, or even remove the requirement for register saving (minimizing the overhead of context switching).

An FIQ is externally generated by taking the nFIQ input signal LOW. You must ensure that the nFIQ input is held LOW until the processor acknowledges the interrupt request from the software handler.

Irrespective of whether exception entry is from ARM state or Thumb state, an FIQ handler returns from the interrupt by executing:

SUBS PC, R14\_fiq, #4

If Non-Maskable Fast Interrupts (NMFIs) are not enabled, you can mask FIQ exceptions by setting the CPSR.F bit to b1. For more information see:

- Program status registers

- Non-maskable fast interrupts.

FIQ and IRQ interrupts are automatically masked by setting the CPSR.F and CPSR.I bits when an FIQ occurs. You can use nested interrupts but it is up to you to save any corruptible registers and to re-enable interrupts.

# 11.3 Non-maskable fast interrupts

When NMFI behavior is enabled, FIQ interrupts cannot be masked by software. Enabling NMFI behavior ensures that when the FIQ mask, that is, the CPSR.F bit, is cleared by the reset handler, fast interrupts are always taken as quickly as possible, except during handling of a fast interrupt. This makes the fast interrupt suitable for signaling critical events. NMFI behavior is controlled by a configuration input signal CFGNMFI, that is asserted HIGH to enable NMFI operation. There is no software control of NMFI.

Software can detect whether NMFI operation is enabled by reading the NMFI bit of the SCTLR:

### $\mathbf{NMFI} == \mathbf{0}$

Software can mask FIQs by setting the CPSR.F bit to b1.

### **NMFI == 1**

Software cannot mask FIQs.

For more information see c1, System Control Register. When the NMFI bit in

the SCTLR is b1:

- an instruction writing b0 to the CPSR.F bit clears it to b0

- an instruction writing b1 to the CPSR.F bit leaves it unchanged

- the CPSR.F bit can be set to b1 only by an FIQ or reset exception entry.

### **11.4 Low interrupt latency**

*Low Interrupt Latency* (LIL) is a set of behaviors that reduce the interrupt latency for the processor, and is enabled by default. That is, the FI bit [21] in the SCTLR is Read-as-One.

LIL behavior enables accesses to Normal memory, including multiword accesses and external accesses, to be abandoned part-way through execution so that the processor can react to a pending interrupt faster than would otherwise be the case. When an instruction is abandoned in this way, the processor behaves as

if the instruction was not executed at all. If, after handling the interrupt, the interrupt handler returns to the program in the normal way using instruction SUBS pc, r14, #4, the abandoned instruction is re-executed. This means that some of the memory accesses generated by the instruction are performed twice.

Memory that is marked as Strongly-ordered or Device type is typically sensitive to the number of reads or writes performed. Because of this, instructions that access Strongly-ordered or Device memory are never abandoned when they have started accessing memory. These instructions always complete either all or none of their memory accesses. Therefore, to minimize the interrupt latency, you must avoid the use of multiword load/store instructions to memory locations that are marked as Strongly- ordered or Device.

### **11. Interrupt controller**

The processor includes a VIC port for connection of a *Vectored Interrupt Controller* (VIC). An interrupt controller is a peripheral that handles multiple interrupt sources. Features usually found in an interrupt controller are:

- Multiple interrupt request inputs, one for each interrupt source, and one or more amalgamated interrupt request outputs to the processor

- The ability to mask out particular interrupt requests

- Prioritization of interrupt sources for interrupt nesting.

In a system with an interrupt controller with these features, software is still required to:

- Determine from the interrupt controller which interrupt source is requesting service

- Determine where the service routine for that interrupt source is loaded

- Mask or clear that interrupt source, before re-enabling processor interrupts to permit another interrupt to betaken.

A VIC does all these in hardware to reduce the interrupt latency. It supplies the starting address of the service routine corresponding to the highest priority asserted interrupt source directly to the processor. When the processor has accepted this address, it masks the interrupt so that the processor can re-enable interrupts without clearing the source. The PL192 VIC is an AMBA compliant, SoC peripheral that is developed, tested, and licensed by ARM.

You can use the VIC port to connect a PL192 VIC to the processor. See the *ARM PrimeCell Vectored Interrupt Controller (PL192) Technical Reference Manual* for more information about the PL192 VIC. You can enable the VIC port by setting the VE bit in the SCTLR. When the VIC port is enabled and an IRQ occurs, the processor performs an handshake over the VIC interface to obtain the address of the handling routine for the IRQ.

### 11.6 Exception when processor in the Thumb mode

### Vector table

The vector table All ARM systems have a vector table. The vector table does not form part of the initialization sequence, but it must be present for any exception to be serviced. It must be placed at a specific address, usually 0x0.

### **Questions Bank:**

- 1. What are the main features of ARM architecture

- 2. Draw and explain the ARM family Architecture.

- 3.Compare ARM7, ARM9 and ARM11 series processors stating features

- 4. Explain the term Banked Register in ARM.

- 5. What is the significance of special purpose registers R13, R14 and R15.

- 6. Explain ARM7 Programmers model.

- 7. Explain terms: CPSR register and Processor modes.

- 8. What is the function of barrel shifter in ARM data flow model

- 9. Explain the architecture of ARM

- 10. Explain the three stage pipelining implemented in ARM processor

### **TEXT / REFERENCE BOOKS**

1. Andrew N.Sloss, Dominic Symes, Chris Wright, ARM Systems Developer's Guide: Designing & Optimizing System Software, Elsevier, 2004.

2. Jonathan W.Valvano, Embedded Microcomputer Systems: Real Time Interfacing, Cengage Learning, 2011

3. Wayne Wolf, Computers as Components: Principles of Embedded Computing System Design, Morgan Kaufman Publishers, 2008.

4. C.M.Krishna, Kang G.Shin, Real time systems, McGraw Hill, 3rd reprint, 2010.

5. Herma K., Real Time Systems: Design for Distributed Embedded Applications, Kluwer Academic Publishers, 1997.

6. William Hohl, ARM Assembly Language, Fundamentals and Techniques, Taylor & Francis, 2009.

# SCHOOL OF ELECTRICAL & ELECTRONICS ENGINEERING DEPARTMENT OF ELECTRONICS & INSTRUMENTATION

# **UNIT-II**

EMBEDDED SYSTEM DESIGN- SBMA5201

# 1. Arm Instruction Set

Data Processing Instructions, Addressing Modes, Branch, Load, Store Instructions, PSR Instructions, Conditional Instructions. Thumb Instruction Set: Register Usage, Other Branch Instructions, Data Processing Instructions, Single Register and Multi Register Load -Store Instructions, Stack, Software Interrupt Instructions

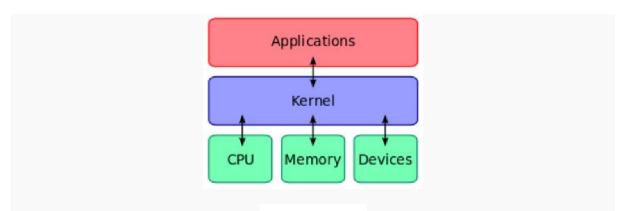

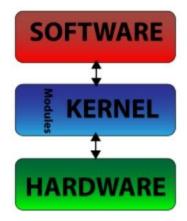

Figure 2.1 Arm Architecture

# 1.1.ARM has 37 registers all of which are 32-bits long.

- 1 dedicated program counter

- 1 dedicated current program status register

- 5 dedicated saved program status registers 30 general purpose registers

The current processor mode governs which of several banks is accessible. Each mode can access a particular set of r0-r12 registers a particular r13 (the stack pointer, sp) and r14 (the link register, lr) the program counter, r15 (pc) the current program status register, cpsr

## 1.2 Privileged modes (except System) can also access

a particular spsr (saved program status register

- ARM processor was designed by Advanced RISC Machine (ARM) Limited Company

- ARM processors are major used for low-power and low cost applications

- Mobile phones

- Communication modems

- Automotive engine management systems

- Hand-held digital systems

Different versions of ARM processors share the same basic machine instruction sets

# 2.ARM programmer model

• The state of an ARM system is determined by the content of visible registers and memory.

• A user-mode program can see 15 32-bit general purpose registers (R0-R14), program counter (PC) and CPSR.

• Instruction set defines the operations that can change the state.

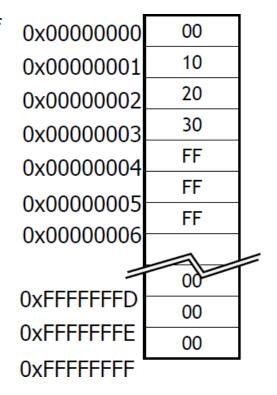

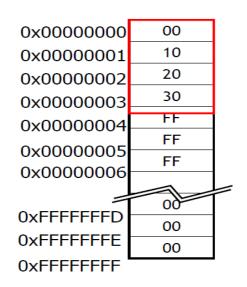

Memory system Byte ordering

- Memory is a linear array of bytes addressed from 0 to 2<sup>32</sup>-1

- Word, half-word, byte

- Little-endian

- Big Endian

- Least significant byte has highest address

Word address 0x00000000

Value: 00102030

Little Endian

Least significant byte has lowest address

Word address 0x0000000 Value: 30201000

Byte ordering

ARM programmer model

|   |                           |     |             |           |            |    | - |

|---|---------------------------|-----|-------------|-----------|------------|----|---|

|   |                           |     |             |           | 0x00000000 | 00 |   |

|   | 5.0                       | -   | 2.0         | 5.0       | 0x0000001  | 10 |   |

|   | RO                        | R1  | R2          | R3        | 0x00000002 | 20 |   |

|   | R4                        | R5  | R6          | R7        | 0x00000003 | 30 |   |

|   | R8                        | R9  | R10         | R11       | 0x00000004 | FF |   |

|   |                           |     | KIU         |           |            | FF |   |

|   | R12                       | R13 | R14         | PC        | 0x00000005 | FF |   |

|   |                           |     |             |           | 0x0000006  |    |   |

|   |                           |     |             |           |            | 0  | 1 |

| Г | 31 30 29 28 27 2<br>NZCVO | 26  | 8765<br>IF1 | 0xFFFFFFD | 00         |    |   |

|   |                           |     |             | 4 3 2 1 0 | 0xFFFFFFFE | 00 |   |

|   |                           |     |             |           |            |    | 1 |

0xFFFFFFF

ARM instructions are all 32-bit long (except for Thumb mode). There are 2<sup>32</sup> possible machine instructions. Fortunately, they are structured.

|                                                             | 31 30 39 38 | 21 | 1.2 | 6 2.I | 4 | (23 | 23  | 21  | 2.0 | 1.9 | 18.17 | 19 | 15 | 1  | 4. T | 3   | 12  | 11   | 10   | ×   |     | 7   | . 6  | 5    |      | 4    | R, | 1  | 1 |

|-------------------------------------------------------------|-------------|----|-----|-------|---|-----|-----|-----|-----|-----|-------|----|----|----|------|-----|-----|------|------|-----|-----|-----|------|------|------|------|----|----|---|

| Data processing immediate shift                             | cond [1]    | 0  | 0   | 0     |   | ope | ode | ÷   | s   |     | Rn    |    |    |    | Rd   |     |     | 5    | hin  | an  | nou | nt: | st   | iit. | 0    |      | R  | 10 |   |

| Miscellaneous instructions:<br>See Figure 3-3               | cond [1]    | ٥  | 0   | 0     | 1 | 0   | x   | ×   | 0   | x   | хх    | x  | x  |    |      | x   | x   | ×    | ĸ    | x   | ×   | x   | x    | ×    | 0    | x    | x  | x  | 1 |

| Data processing register shift [2]                          | cond [1]    | 0  | 0   | 0 0   |   | opt | bo  | 0   | s   |     | Rn    | 1  |    |    | Rd   | 6   |     | 1    | F    | ls. | Î   | 0   | st   | ift  | 1    |      | R  | m  |   |

| Miscellaneous instructions:<br>See Figure 3-3               | cond [1]    | 0  | 0   | 0     | 1 | 0   | х   | x   | 0   | ×   | хх    | x  | х  | )  | C)   | x   | x   | ×    | х    | х   | ×   | 0   | ×    | ×    | 1    | x    | x  | х  | 0 |

| Multiplies, extra load/stores:<br>See Figure 3-2            | cond [1]    | 0  | 0   | 0     | × | x   | X   | ×   | x   | ×   | хх    | x  | ж  | ્ર | 0    | ĸ   | x   | ×    | х    | х   | ×   | 1   | x    | ×    | 1    | x    | x  | x  |   |

| Bata processing immediate [2]                               | cond [1]    | 0  | C   | ) 1   | t | opt | bc  | 8   | s   |     | Rn    | 1  |    |    | Ri   | ğ   | 1   | 13   | rot  | ate |     | t   |      | in   | me   | dia  | te |    |   |

| Undefined instruction [3]                                   | cond (1)    | 0  | 0   | ) t   | 1 | 0   | x   | 0   | 0   | x   | хх    | x  | x  | 3  | e    | ĸ   | x   | x    | x    | x   | x   | x   | ×    | x    | x    | x    | x  | x  | - |

| Move immediate to status register                           | cond [1]    | 0  | 0   | 1     | 1 | 0   | R   | 1   | 0   |     | Mask  |    |    | ŝ  | B    | 2   |     | 3    | rot  | ate | s   | Γ   |      | in   | me   | dia  | ta | 5  |   |

| Load/store immediate offset                                 | cond [1]    | 0  | 1   | 0     | P | U   | 8   | w   | L   |     | Rn    |    |    | 1  | łd   |     |     |      |      |     |     | 87  | me   | dia  | te   |      |    |    |   |

| Load/store register offset                                  | cond [1]    | 0  | 1   | 1     | P | U   | в   | w   | L   |     | Rn    | 10 |    | 1  | Rd   |     |     | sl   | iit. | ап  | ou  | nt  | st   | 成    | 0    |      | R  | m  |   |

| Undefined instruction                                       | cand [1]    | 0  | 1   | 1     | × | ×   | ×   | ×   |     | ×   | х×    | ×  | ×  |    | 6    | ×   | ×   | ĸ    | ×    | ×   | ×   | ×   | ×    | ×    | 1    | ×    | ĸ  | ×  | 2 |

| Undefined instruction [4,7]                                 | 1 1 1 1     | 0  | ×   | . *   | × | ×   | ×   | x   | *   | x   | x x   | ×  | ×  |    |      | ×   | x   | ×    | ×    | ×   | ×   | x   | x    | ×    | ×    | ×    | ×  | ×  | * |

| Loadistore multiple                                         | cond [1]    | 1  | 0   | 0 0   | P | U   | s   | w   | L   |     | Rn    | 15 |    |    |      |     |     |      |      | ro  | gis | ter | list |      |      |      |    |    |   |

| Undefined instruction [4]                                   | 1 1 1 1     | 1  | Ç   | 0 0   | × | ×   | ×   | ×   | ×   | ×   | ×х    | x  | x  |    | 0    | ×   | х   | ж    | ×    | х   | ×   | х   | к    | ×    | х    | х    | ж  | x  | × |

| Branch and branch with link                                 | cond [1]    | 1  | 6   | 1     | L |     |     |     |     |     |       |    |    |    |      | 24- | bit | off  | set  |     |     |     |      |      |      |      |    |    |   |

| Branch and branch with link<br>and change to Thumb [4]      | 1 1 1 1     | 1  | c   | 1     | н |     |     | _   |     |     |       |    | _  |    |      | 24- | bit | offs | set  |     |     |     |      |      |      |      | _  |    |   |

| Coprocessor load/store and double<br>register transfers [6] | cond [5]    | 1  |     | 0     | P | U   | N   | w   | L   |     | Rn    |    |    | 0  | R    | đ   |     | G    | 0    | wn  | n:  |     |      | 8-   | bit) | offe | et | 8  |   |

| Coprocessor data processing                                 | cond [5]    | 1  |     | ţ     | 0 |     | pe  | ode | 1   |     | CRn   |    |    | 0  | R    | d   |     | q    | 2    | wn  |     | op  | 000  | le2  | 0    |      | a  | Rm |   |

| Coprocessor register transfers                              | cond [5]    | Ť  | ŝ   | ŧ     | 0 | op  | cor | ie1 | L   |     | CRn   | ſ  |    |    | Rd   | í.  |     | q    |      | nun | n   | op  | coc  | 62   | 1    |      | a  | Rm |   |

| Software interrupt                                          | cond [1]    | 1  | 1   | 1     | 1 |     |     |     |     |     |       |    |    |    | 8    | w   | nu  | mb   | er   |     |     |     |      |      |      |      | _  |    |   |

| Undefined instruction [4]                                   | 1 1 1 1     | 1  | 1   | 1     | 1 | ×   | ×   | x   | ж   | ×   | x x   | x  | x  | 5  |      | ĸ   | x   | ×    | x    | x   | ×   | x   | x    | ×    | x    | x    | ×  | ×  | × |

# **3.**Features of ARM instruction set

- Load-store architecture

- 3-address instructions

- Conditional execution of every instruction

- Possible to load/store multiple registers at once

- Possible to combine shift and ALU operations in a single instruction

# 4. Registers and Memory Access

- In the ARM architecture

- Memory is byte addressable

- 32-bit addresses

- 32-bit processor registers

- Two operand lengths are used in moving data between the memory and the processor registers

- o Bytes (8 bits) and words (32 bits)

- Word addresses must be aligned, i.e., they must be multiple of 4

- Both little-endian and big-endian memory addressing are supported

- When a byte is loaded from memory into a processor register or stored from a register into the memory

- It always located in the low-order byte position of the register

# **5.ARM Instruction Format**

- Each instruction is encoded into a 32-bit word

- Access to memory is provided only by Load and Store instructions

- The basic encoding format for the instructions, such as Load, Store, Move, Arithmetic, and Logic instructions, is shown below

| 31   | 28    | 27 | 20      | ) ( | 19 16 | 15 12 | 11 |            | 4 | 3  | 0 |

|------|-------|----|---------|-----|-------|-------|----|------------|---|----|---|

| Cond | ition |    | OP code |     | Rn    | Rd    |    | Other info |   | Rı | n |

An instruction specifies a conditional execution code (Condition), the OP code, two or three registers (Rn, Rd,and Rm), and some other information

### **Conditional Execution of Instructions**

A distinctive and somewhat unusual feature of ARM processors is that all instructions are conditionally executed

- Depending on a condition specified in the instruction

- The instruction is executed only if the current state of the processor condition code flag satisfies the condition specified in bits b31-b28 of the instruction

- Thus the instructions whose condition is not meet the process or condition code flag are not executed

$\blacktriangleright$  One of the conditions is used to indicate that the instruction is always executed

# 6.Instruction Set of Arm Processor

- ARM Instruction Set:

- standard 32-bit Instruction set

- Thumb Instruction Set: 16-bit instruction set

- Jazelle Instruction Set: 8-bit instruction set

ARM Instruction Set supports six different types of instructions Data Processing

Instructions

Branch Instructions Load/Store Instructions

Software Interrupt Instruction

Program Status Register Instructions Coprocessor Instructions

### **6.1 Data Processing Instructions**

The data processing instructions operate on data held in general purpose registers. Of the two source operands, one is always a register.

The other has two basic forms:

- An immediate value

- A register value optionally shifted.

If the operand is a shifted register the shift amount might have an immediate value or the value of another register.

Four types of shift can be specified. Most data processing instructions can perform a shift followed by a logical or arithmetic operation.

Multiply instructions come in two classes:

• normal - 32-bit result

• long - 32-bit result variants.

Both types of multiply instruction can optionally perform an accumulate operation.

Used to manipulate data in general-purpose registers, employ a 3-address format, support barrel shifter

### **6.2 Arithmetic Instructions**

ADD, ADC, SUB, SBC, RSB, RSC

Move Instructions MOV,

MVN

Bit-Wise Logical Instructions AND, EOR,

ORR, BIC

Comparison Instructions TST, TEQ,

CMP, CMN

Multiply Instructions: MUL,

MLA

### 6.3 Addressing modes Load /store instructions

have three primary addressing modes

- offset

- pre-indexed

- post-indexed.

offset :They are formed by adding or subtracting an immediate or register-based offset to or from a base register

Register-based offsets can also be scaled with shift operations.

• Preindex

--- Memory address is formed as for offset addressing

--- Memory address also written back to base register

--- So base register value incremented or decremented by offset value

• Postindex

--- Memory address is base register value

--- Offsetaddedorsubtracted Result written back to base register

• Base register acts as index register for pre index and post index addressing

Pre-indexed and post-indexed addressing modes update the base register with the base plus offset calculation.

- Offset either immediate value in instruction or another register

- If register scaled register addressing available

--- Offset register value scaled by shift operator

---- Instruction specifies shift size

As the PC is a general purpose register, a 32-bit value can be loaded directly into the PC to perform a jump to any address in the 4GB memory space.

# **Branch Instructions**

Change the flow of sequencial execution of instructions and force to modify the program counter

Branch (B) jumps in a range of +/-32 MB.

Branch with link(BL) suitable for subroutine call by storing the address of next instructions after BL into the link register and

restore the program counter from the link register while returning from subroutine.

Branch Exchange and Branch Exchange LinkLink for switching theprocessor state from Thumb to ARM and vice versa

### **6.4 Load/Store Instructions**

The second class of instruction is load and store instructions. These instructions come in two main types

- : load or store the value of a single register or register pair

- load and store multiple register values.

Load and store single register instructions can transfer a 32-bit word, a 16-bit half word and an eight-bit byte between memory and a register.

Byte and half word loads may be automatically zero extended or sign extended as they are loaded.

A preload ",hint" instruction is available to help minimize memory system latency.

Swap instructions perform an atomic load and store as synchronization primitive

Transfer data between memory and registers

# 6.5 Single Register Transfer Instructions

- Used to move a single data item inand out of register (signed, unsigned, 16-bit half words and 32-bit word)

- □ Supports register indirect, base-plus-offset and stack addressing mode LDR, STR, LDRB, STRB, LDRH, STRH, LDRSB

## 6.6 Multiple Register Transfer Instructions

Any subset or all the 16 registers loaded from or stored to memory but increase interrupt latency.

Addressing modes-IA, IB, DA, DB

Stack operations-FA, FD, EA, ED LDM, STM

Swap Instructions :swap the contect of memory with the content of registers.SWP, SWPB

### **Software Interrupt Instruction**

\* In effect, a SWI is a user-defined instruction.

- \* It causes an exception trap to the SWI hardware vector (thus causing a change to supervisor mode, plus the associated state saving), thus causing the SWI exception handler to be called.

- \* The handler can then examine the comment field of the instruction to decide what operation has been requested.

- \* By making use of the SWI mechansim, an operating system can implement a set of privileged operations which applications running in user mode can request.

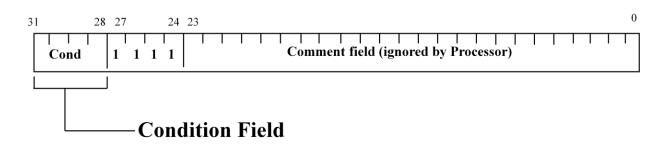

# Software Interrupt Instruction

| 1 1 0 1 1 1 1 1 | 8 – Bit Immediate |

|-----------------|-------------------|

|-----------------|-------------------|

- Address of next instruction is saved in r14\_svc

- CPSR is saved in r14\_svc

- Disables IRQ, Clears T bit, Enters Supervisor mode

- PC is forced to 0x08

- 8 bit immediate is zero extended to fill the 24-bit field in the ARM instruction.

Limits SWIs to first 256 of 16 million ARM SWIs

# 6.7 Program Status Register Instructions

- Used to transfer the content of program status registers to/from a general-purpose register

- .• MRS (copy program status register to a general purpose register), MSR(move a general-

purpose register to a program status register)

# 6. Program status registers

The ARM7TDMI-S contains a CPSR and five SPSRs for exception handlers to

use. The

program status registers:

- Hold the condition code flags

- Control the enabling and disabling of interrupts

- Set the processor operating mode.

The arrangement of bits is shown in Figure

### 7.1 condition code flags

The N, Z, C, and V bits are the condition code flags, You can set these bits by arithmetic and logical operations. The flags can also be set by MSR and LDM instructions. The ARM7TDMI-S tests these flags to determine whether to execute an instruction. All instructions can execute conditionally in ARM state. In Thumb state, only the Branch instruction can be executed conditionally

## 7.2 control bits

The bottom eight bits of a PSR are known collectively as the *control bits*. They are the:

- Interrupt disable bits

- T bit

- Mode bits.

The control bits change when an exception occurs. When the processor is operating in a privileged mode, software can manipulate these bits.

## 7.3 Interrupt disable bits

The I and F bits are the interrupt disable bits:

- when the I bit is set, IRQ interrupts are disabled

- when the F bit is set, FIQ interrupts are disabled.

### T bit

The T bit reflects the operating state:

• when the T bit is set, the processor is executing in Thumb state

• when the T bit is clear, the processor executing in ARM state. The operating state is reflected by the **CPTBIT** external signal.

### **Mode bits**

The M4, M3, M2, M1, and M0 bits (M[4:0]) are the mode bits. These bits determine the processor operating mode as listed in Table 2-2. Not all combinations of the mode bits define a valid processor mode, so take care to use only the bit combinations shown

### **Reserved bits**

The remaining bits in the PSRs are unused but are reserved. When changing a PSR flag or control bits make sure that these reserved bits are not altered. Also, make sure that your program does not rely on reserved bits containing specific values because future processors might have these bits set to one or zero **Coprocessor Instructions**

Used to extend the instruction set, to control on-chips functions (caches and memory management) and for additional computations.

•CDP(data processing), MRC/MCR (register transfer), LDC/STC (memory transfer).

# 7.4 Program status registers

The processor contains one CPSR and five SPSRs for exception handlers to use.

The program status registers:

- hold information about the most recently performed ALU operation

- control the enabling and disabling of interrupts

- set the processor operating mode

# 8.Addressing modes

Load and store instructions have three primary addressing modes

- offset

- pre-indexed

They are formed by adding or subtracting an immediate or register-based offset to or from a base register. Register-based offsets can also be scaled with shift operations. Pre-indexed and post-indexed addressing modes update the base register with the

<sup>•</sup> post-indexed.

base plus offset calculation. As the PC is a general purpose register, a 32-bit value can be loaded directly into the PC to perform a jump to any address in the 4GB memory space

### **8.1 Conditional instructions**

ARM and Thumb instructions can execute conditionally on the condition flags set by a previous instruction.

The conditional instruction can occur either:

- □ Immediately after the instruction that updated the flags.

- □ After any number of intervening instructions that have not updated the flags.

The instructions that you can make conditional depends on whether the processor is in ARM state or Thumb state.

To make an instruction conditional, you must add a condition code suffix to the instruction mnemonic. The condition code suffix enables the processor to test a condition based on the flags. If the condition test of a conditional instruction fails, the instruction:

- $\Box$  Does not execute.

- □ Does not write any value to its destination register.

- $\Box$  Does not affect any of the flags.

- $\Box$  Does not generate any exception.

Conditional execution in ARM state Almost all ARM instructions can be executed conditionally on the value of the ALU status flags in the APSR. You can either add a condition code suffix to the instruction or you can conditionally skip over the instruction using a conditional branch instruction. Using conditional branches instructions to control the flow of execution can be better when a series of instructions depend on the same condition.

#### 8.2 Conditional instructions to control execution

ere follows a list of available conditional codes: EQ : Equal

If the Z flag is set after a comparison.

#### NE : Not Equal

If the Z flag is clear after a comparison.

#### VS : Overflow Set

If the V flag is set after an arithmetical operation, the result of which will not fit into a 32bit destination register.

#### VC : Overflow Clear

If the V flag is clear, the reverse of VS. HI : Higher

### Than (unsigned)

If after a comparison the C flag is set AND the Z flag is clear.

### LS : Lower Than or Same (unsigned)

If after a comparison the C flag is clear **OR** the Z flag is set.

# PL: Plus

If the N flag is clear after an arithmetical operation. For the purposes of defining 'plus', zero is positive because it isn't negative...

# MI : Minus

If the N flag is set after an arithmetical operation.

CS : Carry Set

Set if the C flag is set after an arithmetical operation OR a shift operation, the result of which cannot be represented in 32bits. You can think of the C flag as the 33rd bit of the result.

### CC : Carry Clear

The reverse of CS.

### GE : Greater Than or Equal (signed) If after a

comparison...

the N flag is set **AND** the V flag is set or...

the N flag is clear **AND** the V flag is clear.

GT : Greater Than (signed) If after a

comparison...

the N flag is set AND the V flag is set or...

the N flag is clear **AND** the V flag is clear

### and...

the Z flag is clear.

LE : Less Than or Equal To (signed) If after a

comparison...

the N flag is set AND the V flag is clear or...

the N flag is clear AND the V flag is set

and...

the Z flag is set.

LT : Less Than (signed)

If after a comparison...

the N flag is set AND the V flag is clear or...

the N flag is clear **AND** the V flag is set.

### AL : Always

The default condition, so does not need to be explicitly stated.

NV : Never Not particularly useful, it states that the instruction should never be executed.

A kind of Poor Mans' NOP.

NV was included for completeness (as the reverse of AL), but you should not use it in your own code.

There is a final conditional code which works in the reverse way. S, when applied to an instruction, causes the status flags to

be updated. This does *not* happen automatically - except for those instructions whose purpose is to set the status. For example:

ADD R0, R0, R1

ADDS R0, R0, R1

### ADDEQS R0, R0, R1

The first example shows us a basic addition (adding the value of R1 to R0) which does not affect the status registers.

The second example shows us the same addition, only this time it will cause the status registers to be updated.

The last example shows us the addition again, updating the status registers. The difference here is that it is a conditional instruction. It will only be executed if the result of a previous operation was EQual (if the Z flag is set).

Here is an example of conditional execution at work. You want to compare register zero with the contents of something stored in register ten. If not equal to R10, then call a software interrupt, increment and branch back to do it again. Otherwise clear R10 and return to a calling piece of code (whose address is stored in R14)

An example of conditional execution

| .loop | ; Ma              | ark the loop start position  |

|-------|-------------------|------------------------------|

| CMP   | R0, R10           | ; Compare R0 with R10        |

| SWINE | &40017            | ; Not equal: Call SWI &40017 |

| ADDNE | R0, R0, #1        | ; Add 1 to R0                |

| BNE   | loop              | ; Branch to 'loop'           |

| MOV   | R10, #0           | ; Equal : Set R10 to zero    |

| LDMFD | R13!, {R0-R12,PC} | ; Return to caller Notes:    |

# 9.The 32 bit PSR

Processors after the ARM 3 provide a 32 bit addressing space by moving the PSR out of R15 and giving R15 a full 32 bits in which to store the address of the current position.

Currently, RISC OS works in 26 bit mode, except for a few special cases which is unlikely to be encountered.

The 32 bit mode is important because 26 bits (as in the old PSR) restricts the maximum amount of addressable memory per- application to 28Mb. That is why you can't drag the Next slot beyond 28Mb irrespective of how much memory you have installed.

The allocation of the bits within the CPSR (and the SPSR registers to which it is saved) is:

| 31 30 29 28 |   | 7 | 6 | - | 4    | 3  | 2  | 1  | 0 |

|-------------|---|---|---|---|------|----|----|----|---|

| NZCV        | Ι | F |   | M | 4 M3 | M2 | M1 | M0 |   |

| 0 | 0 | 0 | 0 | 0 | User26 mode |

|---|---|---|---|---|-------------|

| 0 | 0 | 0 | 0 | 1 | FIQ26 mode  |

| 0 | 0 | 0 | 1 | 0 | IRQ26 mode  |

| 0 | 0 | 0 | 1 | 1 | SVC26 mode  |

| 1 | 0 | 0 | 0 | 0 | User mode   |

| 1 | 0 | 0 | 0 | 1 | FIQ mode    |

| 1 | 0 | 0 | 1 | 0 | IRQ mode    |

| 1 | 0 | 0 | 1 | 1 | SVC mode    |

| 1 | 0 | 1 | 1 | 1 | ABT mode    |

| 1 | 1 | 0 | 1 | 1 | UND mode    |

Typically, the processor will be operating in User26, FIQ26, IRQ26 or SVC26 mode. It is possible to enter a 32 bit mode, but extreme care must be taken. RISC OS won't expect it, and will sulk greatly if it finds itself in it!

(except RISC OS 5 which works totally in 32bit mode - and you cannot enter 26bit as the processor doesn't have that anymore...)

You cannot use MOVS PC, R14 or LDMFD R13!, {*registers*, PC}^ in 32 bit code. Neither can you use ORRS PC, R14, #1<<28 to set the V flag.

All of this is now possible using MRS and MSR.

Copy a register into the PSR

| MSR                          | CPSR, R0         | ; Copy R0 into CPSR               |  |  |  |  |  |  |

|------------------------------|------------------|-----------------------------------|--|--|--|--|--|--|

| MSR                          | SPSR, R0         | ; Copy R0 into SPSR               |  |  |  |  |  |  |

| MSR                          | CPSR_flg, R0     | ; Copy flag bits of R0 into CPSR  |  |  |  |  |  |  |

| MSR<br>CPSR                  | CPSR_flg, #1<<28 | ; Copy flag bits (immediate) into |  |  |  |  |  |  |

| Copy the PSR into a register |                  |                                   |  |  |  |  |  |  |

| MRS | R0, CPSR | ; Copy CPSR into R0 |

|-----|----------|---------------------|

| MRS | R0, SPSR | ; Copy SPSR into R0 |

You have two PSRs - CPSR which is the Current Program Status Register and SPSR which is the Saved Program Status Register Each privileged mode has its own PSR, so the total available selection of PSR is:

- CPSR\_all current

- SPSR\_svc saved, SVC(32) mode

- SPSR\_irq saved, IRQ(32) mode

- SPSR\_abt saved, ABT(32) mode

- SPSR\_und saved, UND(32) mode

- SPSR\_fiq saved, FIQ(32) mode

It appears as if you cannot explicitly specify to save the current PSR in, say, SPSR\_fiq. Instead, you should change to FIQ mode and then save to SPSR. In other words, you can only alter the SPSR of the mode you are in.

Using the \_flg suffix allows you to alter the flag bits without affecting the control bits.

In user(32) mode, the control bits of CPSR are protected, you can only alter the condition flags. In other modes, the entire CPSR is available. You should not specify R15 as a source or destination register. And finally, you must not attempt to access the SPSR in user(32) mode as it doesn't exist!

To set the V flag:

MSR CPSR\_flg, #&1000000

This sets the V flag and doesn't affect the control bits.

Here, for your delectation, is a way to set the V flag on any ARM processor:

CMP

R0, #1<<31</th>

CMNVC

R0, #1<<31</th>

Clever, huh?

Clever, huh?

To change mode:

| MRS     | R0, CPSR_all           | ; Copy the PSR BIC R0,          |

|---------|------------------------|---------------------------------|

| R0, #&1 | F; Clear the mode bits |                                 |

| ORR     | R0, R0, #new_mode      | ; Set bits for new mode         |

| MSR     | CPSR_all, R0           | ; write PSR back, changing mode |

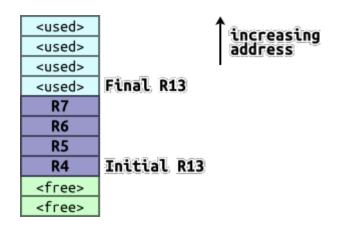

## STACK

The ARM architecture offers extensive support for memory stack by allowing programmers to chose one of four stack format/orientation.

- Empty or Full:

- Empty: Stack Pointer points to the next free space on stack

- Full: Stack Pointer points to the last item on the stack

- Ascending or Descending:

- Ascending: Grows from low memory to high memory

- Descending: Grows from high memory to low memory

- I386, Sparc and PowerPC all use a "Full, Descending" stack format.

We need to store the processor state when making nested calls.

The multiple data transfer instructions provide a mechanism for storing state on the *stack* (pointed to by R13).

The STM and LDM instructions" modes have aliases for accessing stacks:

- FD = Full Descending

- STMFD/LDMFD = STMDB/LDMIA

- ED = Empty Descending

- STMED/LDMED = STMDA/LDMIB

- FA = Full Ascending

- STMFA/LDMFA = STMIB/LDMDA

- EA = Empty Ascending

- STMEA/LDMEA = STMIA/LDMDB Anything

but a full descending stack is rare!

|               | STMFD r13!, {r4-r7} – Push R4,R5,R6 and R7 onto thstack. |  |  |  |

|---------------|----------------------------------------------------------|--|--|--|

| <used></used> | <b>↑</b>                                                 |  |  |  |

| <used></used> | increasing<br>address                                    |  |  |  |

| <used></used> | 1 1                                                      |  |  |  |

| <used></used> | Initial R13                                              |  |  |  |

| R7            |                                                          |  |  |  |

| R6            |                                                          |  |  |  |

| NO NO         |                                                          |  |  |  |

| R5            |                                                          |  |  |  |

|               | Final R13                                                |  |  |  |

| R5            | Final R13                                                |  |  |  |

Figure : 2.2 Register File

LDMFD r13!, {r4-r7} – Pop R4,R5,R6 and R7 from the stack

Figure 2.3 Register file

# 9.Thumb Instruction Set

- ARM architecture versions v4T and above define a 16-bit instruction set called the Thumb instruction set. The functionality of the Thumb instruction set is a subset of the functionality of the 32-bit ARM instruction set.

- A processor that is executing Thumb instructions is operating in *Thumb state*. A processor that is executing ARM instructions is operating in *ARM state*.

- A processor in ARM state cannot execute Thumb instructions, and a processor in Thumb state cannot execute ARM instructions. You must ensure that the processor never

receives instructions of the wrong instruction set for the current state.

- Each instruction set includes instructions to change processor state.

- Note: ARM processors always start executing code in ARM state.

- Thumb is a 16-bit instruction set

- Optimized for code density from C code

- Improved performance form narrow memory

- Subset of the functionality of the ARM instruction set

- Core has two execution states ARM and Thumb

- Switch between them using **BX** instruction

- Thumb has characteristic features:

- Most Thumb instruction are executed unconditionally

- Many Thumb data process instruction use a 2-address format

- Thumb instruction formats are less regular than ARM instruction formats, as a result of the dense encoding.

- The processor in Thumb mode uses same eight general- purpose integer registers that are available ARM

mode.Some Thumb instructions also access the PC(ARM register 15),the Link Register(ARM register 14) and Stack Pointer(ARM register 13).

- When R15 is read, bit[0] is zero and bits[31:1]contain the PC. when R15 is written ,bit[0] is IGNORED and bits[31:1] are written to the PC.

- Thumb does not provide direct access to the CPSR or any SPSR.

- Thumb execution is flagged by the T bit(bit[5]) in the CPSR. T==0 32-bit instructions are fetched(ARM instruction)

T==1 16-bit instructions are fetched(Thumb instruction)

# 9.1 Thumb applications

In a typical embedded system:

- use ARM code in 32-bit on-chip memory for small speed- critical routines

- use Thumb code in 16-bit off-chip memory for large non-critical control routines

<u>Note:</u>Switching between ARM and Thumb States of Execution Using BX Instruction

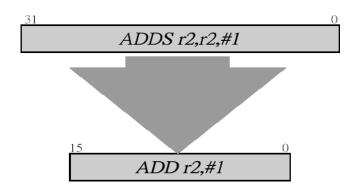

**Figure 2.5 Thumb Instructions**

For Most Instruction Generated by the Compiler

- Condition Execution is not used.

- Source and Destination Registers are identical

- Only low registers used

- Constants are limited size

- Inline barrel shifter not used

# **Data Types**

Byte (8-bit): placed on any byte boundary.

Half-word (16-bit): aligned to two-byte boundaries. Word (32-bit):

aligned to four- byte boundaries

# **Thumb Programmers Model**

- •Registers r0 to r7 are accessible (Lo)

- Few instructions require r8 to r15 to be specified

- r13 is used as the stack pointer

- r14 is used as the link register

- r15 is used as the program counter

# 9.2 THUMB Register Organization

# Thumb General registers and Program Counter