### SCHOOL OF BIO AND CHEMICAL ENGINEERING

### DEPARTMENT OF BIOMEDICAL ENGINEERING

UNIT – I –BIOSIGNAL CONDITIONING– SBMA1504

# 1. Introduction to OPAMP

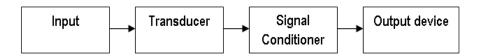

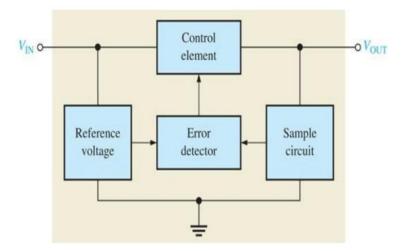

Signal conditioning is the manipulation of an analog signal in such a way that it meets the requirements of the next stage for further processing.

• Signal conditioning is stage of instrumentation system used for modifying the transducer signal into a usable format for the final.

Fig: 1.1 Signal Conditioning Process

# **Need of Signal Conditioner**

- Drive the output device connected at the output of system

- It is required to perform following operations.

- 1. Amplification 2. Modulation/Demodulation 3. Attenuation 4. Sampling

- 5. Integration 6. Differentiation 7. Addition/ Subtraction

- An integrated circuit (IC) is a miniature, low cost electronic circuit consisting of active and passive components fabricated together on a single crystal of silicon.

- The active components are transistors and diodes and passive components are resistors and capacitors.

- OP-AMP is basically a multistage amplifier which uses a number of amplifier stages interconnected to each other.

- The integrated op amp offers all the advantage of monolithic integrated circuit such as small size, high reliability, reduced cost, less power consumption.

- It is a versatile device that can be used to amplify AC as well as DC input signals & designed for computing mathematical functions such as addition, subtraction ,multiplication, integration & differentiation

# **1.1 Integrated Circuits**

An integrated circuit (IC) is a miniature, low cost electronic circuit consisting of active and passive components fabricated together on a single crystal of silicon. The active components are transistors and diodes and passive components are resistors and capacitors.

### Advantages of integrated circuits

- Miniaturization and hence increased equipment density.

- Cost reduction due to batch processing.

- Increased system reliability due to the elimination of soldered joints.

- Improved functional performance.

- Matched devices.

- Increased operating speeds.

- Reduction in power consumption

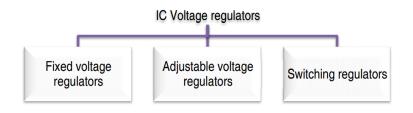

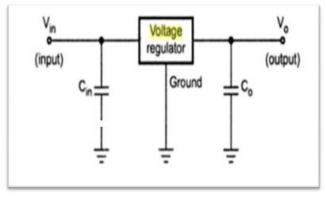

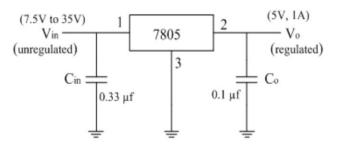

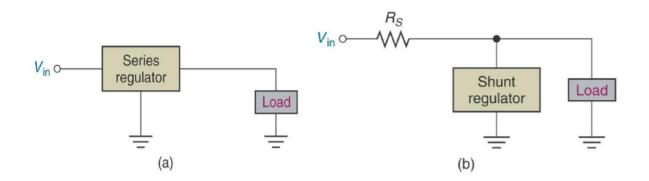

#### Classification

Integrated circuits can be classified into analog, digital and mixed signal (both analog and digital on the same chip). Based upon above requirement two different IC technologies namely Monolithic Technology and Hybrid Technology have been developed. In monolithic IC, all circuit components, both active and passive elements and their interconnections are manufactured into or on top of a single chip of silicon. In hybrid circuits, separate component parts are attached to a ceramic substrate and interconnected by means of either metallization pattern or wire bounds.

Digital integrated circuits can contain anything from one to millions of logic gates, flip-flops, multiplexers, and other circuits in a few square millimetres. The small size of these circuits allows high speed, low power dissipation, and reduced manufacturing cost compared with board-level integration. These digital ICs, typically microprocessors, DSPs, and micro controllers work using binary mathematics to process "one" and "zero" signals.

Analog ICs, such as sensors, power management circuits, and operational amplifiers, work by processing continuous signals. They perform functions like amplification, active filtering, demodulation, mixing, etc. Analog ICs ease the burden on circuit designers by having expertly designed analog circuits available instead of designing a difficult analog circuit from scratch.

ICs can also combine analog and digital circuits on a single chip to create functions such as A/D converters and D/A converters. Such circuits offer smaller size and lower cost, but must carefully account for signal interference

# **1.2 Introduction to Operational Amplifier OP AMP**

- An integrated circuit (IC) is a miniature, low cost electronic circuit consisting of active and passive components fabricated together on a single crystal of silicon.

- The active components are transistors and diodes and passive components are resistors and capacitors.

- OP-AMP is basically a multistage amplifier which uses a number of amplifier stages

interconnected to each other.

- The integrated op amp offers all the advantage of monolithic integrated circuit such as small size, high reliability, reduced cost, less power consumption.

- It is a versatile device that can be used to amplify AC as well as DC input signals & designed for computing mathematical functions such as addition, subtraction, multiplication, integration & differentiation

- The term "operational amplifier" denotes a special type of amplifier that, by proper selection of its external components, could be configured for a variety of operations.

## HISTORY

- First developed by John R. Ragazzine in 1947 with vacuum tube.

- In 1960 at FAIRCHILD SEMICONDUCTOR CORPORATION, Robert J. Widlar fabricated op amp with the help of IC fabrication technology.

- In 1968 FAIRCHILD introduces the op-amp that was to become the industry standard.

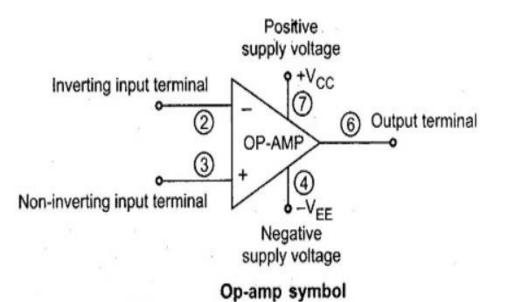

### What is OP-AMP?

- An operational amplifier (op-amp) is a DC-coupled high-gain electronic voltage amplifier. Direct-coupled high gain amplifier usually consisting of one or more differential amplifiers

- Output stage is generally a push-pull or push-pull complementary-symmetry pair.

- Op amps are differential amplifiers, and their output voltage is proportional to the difference of the two input voltages.

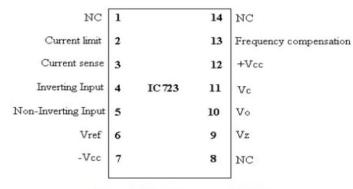

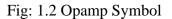

**Pin Diagram**

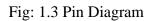

#### **Block Diagram of OP-AMP**

Fig: 1.4 Block Diagram of OP-AMP

The input stage is a differential amplifier. The differential amplifier used as an input stage provides differential inputs and a frequency response down to DC. Special techniques are used to provide the high input impedance necessary for the operational amplifier. The second stage is a high-gain voltage amplifier. This stage may be made from several TRANSISTORs to provide high gain. A typical operational amplifier could have a voltage gain of 200,000. Most of this gain comes from the voltage amplifier stage. The final stage of the OP AMP is an output amplifier. The output amplifier provides low output impedance. The actual circuit used could be an emitter follower. The output stage should allow the operational amplifier to deliver several mill amperes to a load.

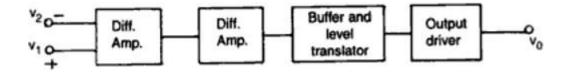

### **1.3 Ideal op-amp characteristics**

- $\cdot$  Infinite voltage gain A.

- Infinite input resistance Ri, so that almost any signal source can drive it and there is no loading of the proceeding stage.

- Zero output resistance Ro, so that the output can drive an infinite number of other devices.

- $\cdot$  Zero output voltage, when input voltage is zero.

- · Infinite bandwidth, so that any frequency signals from o to  $\infty$  HZ can be amplified without attenuation.

- Infinite common mode rejection ratio, so that the output common mode noise voltage is zero.

- Infinite slew rate, so that output voltage changes occur simultaneously with input voltage changes.

# **1.4 OP-AMP characteristics**

The OP-AMP characteristics (parameters) are important in practice because, we can use them to compare the performance of various op amp ICs and select the best suitable from them for the required application.

OP-AMP characteristics are classified into two categories namely AC characteristic and DC characteristic.

**Open loop voltage gain** - It is the differential gain of an OP-AMP in the open loop mode of operation.

**Input resistance** - It is defined as the equivalent resistance which can be measured at either at inverting or non- inverting terminal with the other terminal connected to ground.

**Output resistance** - It is the resistance measured by looking into the output terminal of OP-AMP, with the input source short circuited.

Bandwidth - It is the range over which all signal frequencies are amplified almost equal.

Common mode rejection ratio - It is defined as the ratio of differential gain to common mode gain.

Slew rate - It is defined as the maximum rate of change of output voltage per unit time.

**Power supply rejection ratio** - It is the change in an OP-AMPs input offset voltage caused by variation in the supply voltage.

**Input offset voltage** - Ideally, for a zero input voltage output should be zero. But practically it is not so. This is due to unavoidable unbalances inside the OP- AMP.

**Input bias current** - It is the average of the currents flowing into the two input terminal of the OP-AMP.

**Input offset current** - It is the algebraic difference between the currents flowing into the inverting and non-inverting terminal of OP-AMP.

Fig: 1.5 a) Ideal opamp, b) Equivalent circuit of opamp c) open loop circuit

## 1.5 Open Loop circuit

The magnitude of  $A_{OL}$  is typically very large—100,000 or more for integrated circuit opamps—and therefore even a quite small difference between V<sub>+</sub> and V<sub>-</sub> drives the amplifier output nearly to the supply voltage. Situations in which the output voltage is equal to or greater than the supply voltage are referred to as saturation of the amplifier. The magnitude of  $A_{OL}$  is not well controlled by the manufacturing process, and so it is impractical to use an open loop amplifier as a stand-alone differential amplifier.

Without negative feedback, and perhaps with positive feedback for regeneration, an opamp acts as a comparator. If the inverting input is held at ground (0 V) directly or by a resistor  $R_g$ , and the input voltage  $V_{in}$  applied to the non-inverting input is positive, the output will be maximum positive; if  $V_{in}$  is negative, the output will be maximum negative. Since there is no feedback from the output to either input, this is an open loop circuit acting as a comparator.

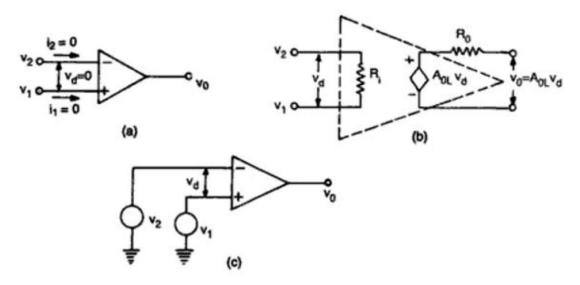

### **1.6 Close loop configuration**

- In close loop configuration, a feedback is introduced i.e. a part of output is fed back to the input.

- The feedback can be of the following two types:

- 1. Positive feedback/regenerative feedback

- 2. Negative feedback/degenerative feedback

Fig: 1.6 Opamp with negative feedback

### **Positive feedback**

- If the feedback signal and the input signal are in phase with each other then it is called as the positive feedback.

- It is used in application such as oscillators and schmitt trigger or regenerative comparators.

## **Negative feedback**

- If the signal fed back to the input and the original input signal are 180° out of phase, then it is called as the negative feedback

- In application of op amp as an amplifier, the negative feedback is used.

## Advantages of negative feedback

- It stabilizes gain

- Reduces the distortion

- Increases the bandwidth

- Reduces the effect of variations in temperature and supply voltage on the output of op amp

- The only disadvantage of negative feedback is low gain

# **1.7 Inverting Amplifier**

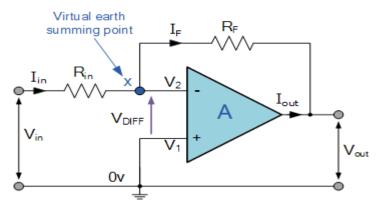

Fig: 1.7 Inverting Amplifier

In this **Inverting Amplifier** circuit the operational amplifier is connected with feedback to produce a closed loop operation. When dealing with operational amplifiers there are two very important rules to remember about inverting amplifiers, these are: "No current flows into the input terminal" and that "V1 always equals V2". However, in real world op-amp circuits both of these rules are slightly broken. This is because the junction of the input and feedback signal (X) is at the same potential as the positive (+) input which is at zero volts or ground then, the junction is a **"Virtual Earth"**. Because of this virtual earth node the input resistance of the amplifier is equal to the value of the input resistor, Rin and the closed loop gain of the inverting amplifier can be set by the ratio of the two external resistors.

- No Current Flows into the Input Terminals

- The Differential Input Voltage is Zero as V1 = V2 = 0 (Virtual Earth)

Then by using these two rules we can derive the equation for calculating the closed-loop gain of an inverting amplifier, using first principles.

Current ( i ) flows through the resistor network as shown.

| Vout | _ | Rf  |

|------|---|-----|

| Vin  | _ | Rin |

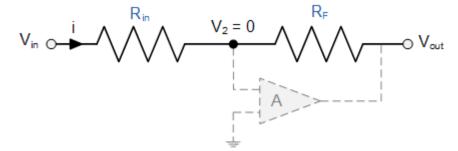

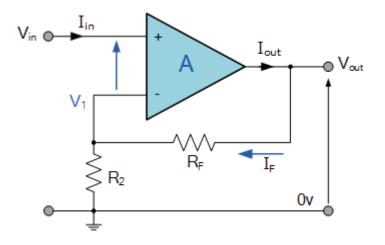

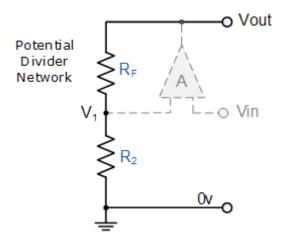

### **1.8 Non-Inverting Amplifier**

Fig: 1.8 Non-Inverting Amplifier

In this configuration, the input voltage signal, ( $V_{IN}$ ) is applied directly to the non-inverting (+) input terminal which means that the output gain of the amplifier becomes "Positive" in value in contrast to the "Inverting Amplifier" circuit we saw in the last tutorial whose output gain is negative in value. The result of this is that the output signal is "in-phase" with the input signal.

Feedback control of the non-inverting operational amplifier is achieved by applying a small part of the output voltage signal back to the inverting (–) input terminal via a Rf - R2 voltage divider network, again producing negative feedback. This closed-loop configuration produces a non-inverting amplifier circuit with very good stability, a very high input impedance, Rin approaching infinity, as no current flows into the positive input terminal, (ideal conditions) and a low output impedance.

Fig:1.9 Equivalent Potential Divider Network

Then using the formula to calculate the output voltage of a potential divider network, we can calculate the closed-loop voltage gain ( $A_V$ ) of the **Non-inverting Amplifier** as follows:

$$\mathbf{V}_1 = \frac{\mathbf{R}_2}{\mathbf{R}_2 + \mathbf{R}_F} \times \mathbf{V}_{\mathbf{OUT}}$$

Ideal Summing Point:  $V_1 = V_{IN}$

Voltage Gain,  $A_{(V)}$  is equal to:  $\frac{V_{OUT}}{V_{IN}}$

Then,

$$A_{(V)} = \frac{V_{OUT}}{V_{IN}} = \frac{R_2 + R_F}{R_2}$$

Transpose to give:  $A_{(V)} = \frac{V_{OUT}}{V_{IN}} = 1 + \frac{R_F}{R_2}$

# **1.9 Voltage follower**

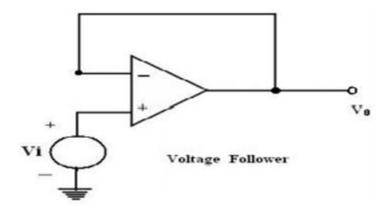

Fig: 1.9 b Voltage Follower

If  $R_{1=\infty}$  and  $R_{f=0}$  in the non inverting amplifier configuration. The amplifier act as a unitygain amplifier or voltage follower.

The circuit consists of an op -amp and a wire connecting the output voltage to the input, i.e. the output voltage is equal to the input voltage, both in magnitude and phase.  $V_0 = V_i$ . Since the output voltage of the circuit follows the input voltage, the circuit is called voltage follower. It offers very high input impedance of the order of M $\Omega$  and very low output impedance.

Therefore, this circuit draws negligible current from the source. Thus, the voltage follower can be used as a buffer between a high impedance source and a low impedance load for impedance matching applications.

#### 1.10 Summing Amplifier

Op-amp may be used to design a circuit whose output is the sum of several input signals. Such a circuit is called a summing amplifier or a summer or adder.

#### **Inverting Summing Amplifier**

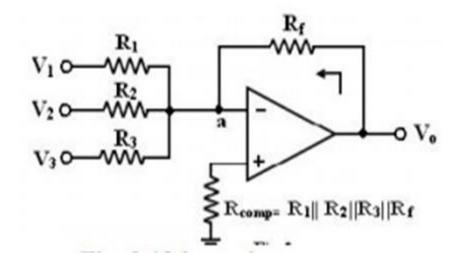

Fig: 1.10 Inverting Summing Amplifier

A typical summing amplifier with three input voltages  $V_1$ ,  $V_2$  and  $V_3$  three input resistors  $R_1$ ,  $R_2$ ,  $R_3$  and a feedback resistor  $R_f$  is shown in figure 2. The following analysis is carried out assuming that the op-amp is an ideal one, AOL=  $\infty$ . Since the input bias current is assumed to be zero, there is no voltage drop across the resistor Rcomp and hence the non-inverting input terminal is at ground potential.

$I \;=\; V_1/R1 \,+\, V_2/R2 \ldots \, . + \, Vn/Rn$

$Vo = -R_{f} I = R_{f} / R (V_{1} + V_{2} + .... V_{n}).$

To find Rcomp, make all inputs  $V1 = V_2 = V_3 = 0$ .

So the effective input resistance  $R_i = R_1 \parallel R_2 \parallel R_3$ .

Therefore,  $\text{Rcomp} = \text{R}_i \parallel \text{R}_f = \text{R}_1 \parallel \text{R}_2 \parallel \text{R}_3 \parallel \text{R}, \text{f}$ .

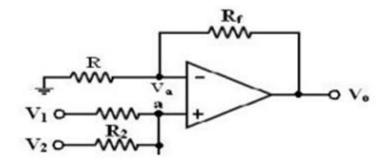

**Non-Inverting Summing Amplifier**

Fig: 1.11 Non-Inverting Summing Amplifier

A summer that gives a non-inverted sum is the non-inverting summing amplifier of figure. Let the voltage at the (-) input terminal be Va. which is a non-inverting weighted sum of inputs.

Let

$$R_1 = R_2 = R_3 = R = R_f/2$$

$V_o = V_1 + V_2 + V_3$

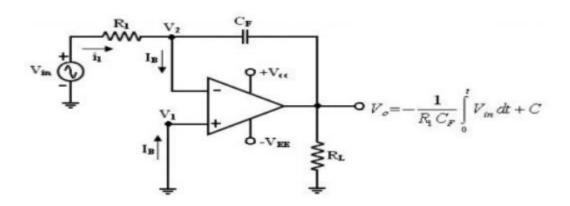

# **1.11 Integrator**

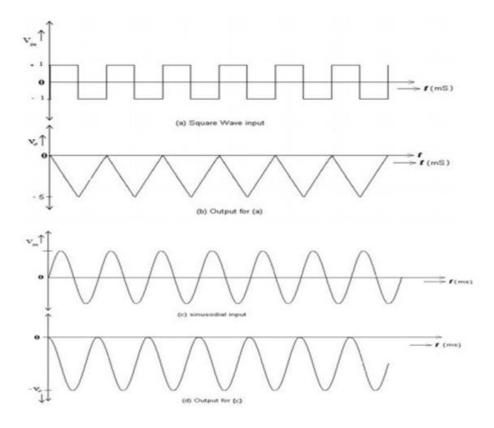

A circuit in which the output voltage waveform is the integral of the input voltage waveform is the integrator or Integration Amplifier. Such a circuit is obtained by using a basic inverting amplifier configuration if the feedback resistor  $R_F$  is replaced by a capacitor  $C_F$ . The expression for the output voltage V0 can be obtained by KVL eqn. at node V<sub>2</sub>.

Fig: 1.12 Integrator

$$I_1 = I_B + i_f$$

Since  $I_B$  is negligible small,  $i_1=i_F$

Relation between current through and voltage across the capacitor is

$$i_{C(t)} = C dv_c(t)/dt$$

V<sub>1=</sub>0 because A is very large,

The output voltage can be obtained by integrating both sides with respect to time

$$V_0(jw) = [1 / jwR_1C_f] V_i(jw)$$

Indicates that the output is directly proportional to the negative integral of the input volts and inversely proportional to the time constant  $R_1C_F$ .

Ex: If the input is sine wave -> output is cosine wave.

If the input is square wave -> output is triangular wave.

These waveform with assumption of  $R_1C_f = 1$ , Vout =0V (i.e) C =0.

When  $V_{in} = 0$  the integrator works as an open loop amplifier because the capacitor  $C_F$  acts an open circuit to the input offset voltage  $V_{io}$ .

The Input offset voltage  $V_{io}$  and the part of the input is charging capacitor  $C_F$  produce the error voltage at the output of the integrator.

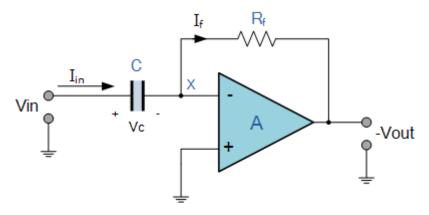

### **1.12 Differentiator**

The basic operational amplifier differentiator circuit produces an output signal which is the first derivative of the input signal.

Here, the position of the capacitor and resistor have been reversed and now the reactance,  $X_C$  is connected to the input terminal of the inverting amplifier while the resistor, Rf forms the negative feedback element across the operational amplifier as normal.

This operational amplifier circuit performs the mathematical operation of **Differentiation** that is it "*produces a voltage output which is directly proportional to the input voltage's rateof-change with respect to time*". In other words the faster or larger the change to the input voltage signal, the greater the input current, the greater will be the output voltage change in response, becoming more of a "spike" in shape.

Fig: 1.13 Differentiator

Since the node voltage of the operational amplifier at its inverting input terminal is zero, the current, i flowing through the capacitor will be given as:

$$I_{IN} = I_F$$

and  $I_F = -\frac{V_{OUT}}{R_F}$

The charge on the capacitor equals Capacitance times Voltage across the capacitor

$$Q = C \times V_{IN}$$

Thus the rate of change of this charge is:

$$\frac{\mathrm{dQ}}{\mathrm{dt}} = \mathrm{C} \, \frac{\mathrm{dV}_{\mathrm{IN}}}{\mathrm{dt}}$$

but dQ/dt is the capacitor current, *i*

$$I_{IIN} = C \frac{dV_{IIN}}{dt} = I_F$$

$$\therefore -\frac{V_{OUT}}{R_F} = C \frac{dV_{IIN}}{dt}$$

from which we have an ideal voltage output for the op-amp differentiator is given as:

$$V_{OUT} = -R_F C \frac{dV_{IN}}{dt}$$

a - 1 - 1

Therefore, the output voltage Vout is a constant  $-Rf^*C$  times the derivative of the input voltage Vin with respect to time. The minus sign (–) indicates a 180° phase shift because the input signal is connected to the inverting input terminal of the operational amplifier.

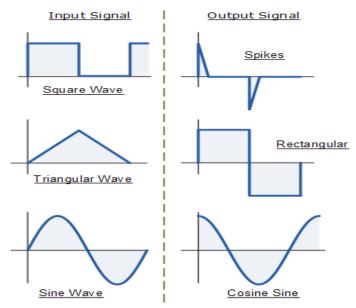

#### **Op-amp Differentiator Waveforms**

If we apply a constantly changing signal such as a Square-wave, Triangular or Sine-wave type signal to the input of a differentiator amplifier circuit the resultant output signal will be changed and whose final shape is dependent upon the RC time constant of the Resistor/Capacitor combination.

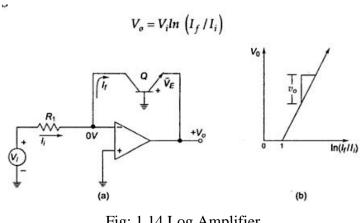

# 1.13 Log Amplifier

Fig: 1.14 Log Amplifier

There are several applications of log and antilog amplifiers. Antilog computation may require functions such as  $\ln x$ ,  $\log x$  or  $\sinh x$ .

Uses:

Direct dB display on a digital Voltmeter and Spectrum analyzer.

Log-amp can also be used to compress the dynamic range of a signal.

A grounded base transistor is placed in the feedback path. Since the collector is placed in the feedback path. Since the collector is held at virtual ground and the base is also grounded, the transistor's= voltage [-current-1] relationship becomes that of a diode and is given by,

$$I_E = I_s [e^{qV_{BE} \over kT} - 1]$$

and since  $I_c = I_E$  for a grounded base transistor  $I_C = I_s e^{kT}$

Is-emitter saturation current  $\approx 10^{-13}$ A

k=Boltzmann's constant

T=absolute temperature (in<sup>o</sup>K)

$$V_o = -\frac{kT}{q} ln\left(\frac{V_i}{R_1 I_S}\right) = -\frac{kT}{q} ln\left(\frac{V_i}{V_R}\right)$$

where  $V_{ref} = R_1 I_s$

The output voltage is thus proportional to the logarithm of input voltage.

Although the circuit gives natural log (ln), one can find log10, by proper scaling

### 1.14 Antilog Amplifier

A circuit to convert logarithmically encoded signal to real signals. Transistor in inverting input converts input voltage into logarithmically varying currents.

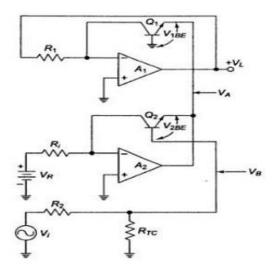

The circuit is shown in figure below. The input Vi for the antilog-amp is fed into the temperature compensating voltage divider  $R_2$  and  $R_{TC}$  and then to the base of  $Q_2$ . The output of A2 is fed back to  $R_1$  at the inverting input of op amp A<sub>1</sub>. The non-inverting inputs are grounded.

#### Fig 2.32 Antilog amplifier

$V_{1BE} = \frac{kT}{q} \ln[\frac{V_L}{R_1 I_s}] \text{ and } V_{2BE} = \frac{kT}{q} \ln[\frac{V_B}{R_1 I_s}] \text{ and } V_A = -V_{1BE} \text{ and } V_B = R_{TC}/(R_2 + R_{TC}) V_i$   $V_{Q2E} = V_B + V_{2BE} = R_{TC}/(R_2 + R_{TC}) V_i - \frac{kT}{q} \ln[\frac{V_B}{R_1 I_s}]$   $V_{Q2E} = V_A$

Therefore,

$$-\frac{kT}{q}ln\left(\frac{V_L}{R_1I_s}\right) = \frac{R_{TC}}{R_2 + R_{TC}}V_i + \frac{kT}{q}ln\left(\frac{V_R}{R_1I_s}\right)$$

Rearranging, we get

$$\frac{R_{TC}}{R_2 + R_{TC}} V_i = -\frac{kT}{q} ln \left(\frac{V_L}{R_1 I_S}\right) - \frac{kT}{q} ln \left(\frac{V_R}{R_1 I_S}\right)$$

$$= -\frac{kT}{q} ln \left(\frac{V_L}{V_R}\right)$$

We know that  $\log_{10} x = 0.4343 \ln x$ .

Therefore,

$$-0.4343 \left(\frac{q}{kT}\right) \left(\frac{R_{TC}}{R_2 + R_{TC}}\right) V_i = 0.4343 \ln \left(\frac{V_L}{V_R}\right)$$

$$-0.4343 \left(\frac{q}{kT}\right) \left(\frac{R_{TC}}{R_2 + R_{TC}}\right) V_i = \log_{10} \left(\frac{V_L}{V_R}\right)$$

$$-KV_i = \log \left(\frac{V_L}{V_R}\right)$$

$$K = 0.4343 \left(\frac{q}{kT}\right) \left(\frac{R_{TC}}{R_2 + R_{TC}}\right)$$

$$V_L = V_R 10^{-KV_i}$$

The output  $V_0$  of the antilog- amp is fed back to the inverting input of  $A_1$  through the resistor  $R_1$ . Hence an increase of input by one volt causes the output to decrease by a decade.

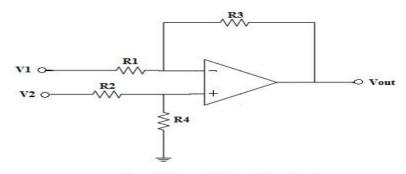

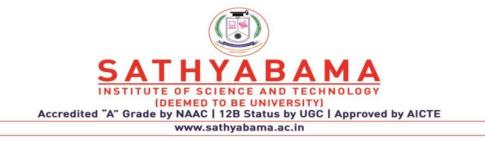

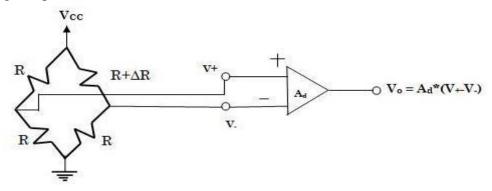

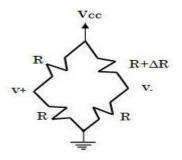

## **1.15 Differential Amplifier**

A difference amplifier or differential amplifier amplifies the difference between the two input signals. An operational amplifier is a difference amplifier; it has an inverting input and a non-inverting input. But the open loop voltage gain of an operational amplifier is too high (ideally infinite), to be used without a feedback connection. So, a practical difference amplifier uses a negative feedback connection to control the voltage gain of the amplifier.

Fig.- Differential Amplifier Circuit

The difference amplifier shown in the above circuit is a combination of both inverting and non-inverting amplifiers. If the non-inverting terminal is connected to ground, the circuit operates as an inverting amplifier and the input signal V<sub>1</sub> is amplified by  $-(R_3/R_1)$ .

Similarly, if the inverting input terminal is connected to ground, the circuit behaves as a non-inverting amplifier. With the inverting input terminal grounded,  $R_3$  and  $R_1$  function as the feedback components of a non-inverting amplifier. Input  $V_2$  is potentially divided across resistors  $R_2$  and  $R_4$  to give  $V_{R4}$ , and then  $V_{R4}$  is amplified by  $(R_3 + R_1) / R_1$ .

With  $V_2 = 0$ ,

$V_{O1} = -(R_3 / R_1) * V_1$

With  $V_1 = 0$ ,

$$V_{R4} = \{R_4 / (R_2 + R_4)\} * V_2$$

and

$$V_{O2} = \{(R_1 + R_3)/R_1\} * V_{R4}$$

Therefore,

$$V_{O2} = \{ (R_1 + R_3) / R_1 \} * \{ R_4 / (R_2 + R_4) \} * V_2$$

If the input resistances are chosen such that,  $R_2 = R_1$  and  $R_4 = R_3$ , then

$$V_{O2} = \{R_3 / R_1\} * V_2$$

Now, according to superposition principle if both the input signals  $V_1$  and  $V_2$  are present, then the output voltage is

$$V_{O} = V_{O1} + V_{O2}$$

$$= \{-(R_3 / R_1) * V_1\} + \{R_3 / R_1\} * V_2$$

Which results in,

$$V_0 = (R_3 / R_1) * \{V_2 - V_1\}$$

When the resistors  $R_3$  and  $R_1$  are of the same value, the output is the direct difference of the input voltages applied. By selecting  $R_3$  greater than  $R_1$ , the output can be made an amplified version of the difference of the input voltages.

#### **Differential Gain**

The differential gain of a difference amplifier is defined as the gain obtained at the output signal with respect to the difference in the input signals applied.

The output voltage of a difference amplifier is given as,

$$\mathbf{V}_{\mathrm{O}} = \mathbf{A}_{\mathrm{D}} \left( \mathbf{V}_{1} - \mathbf{V}_{2} \right)$$

where,  $A_D = -(R_3 / R_1)$  is the differential gain of the amplifier.

#### **Common Mode Input**

A difference amplifier amplifies the difference between the two input voltages. Ideally, a common mode input  $V_{cm}$  would make the inputs  $(V_1 + V_{cm})$  and  $(V_2 + V_{cm})$ , which will result in  $V_{cm}$  being cancelled out when the difference of the two input voltages is amplified.

Since the output of a practical difference amplifier depends upon the ratio of the input resistances, if these resistor ratios are not exactly equal, then one input voltage is amplified by a greater amount than the other input.

Consequently, the common mode voltage  $V_{cm}$  will not be completely cancelled. Because it is practically impossible to match resistor ratios perfectly, there is likely to be some common mode output voltage.

With the common mode input voltage present, the output voltage of the differential amplifier is given as,

$$\mathbf{V}_{\mathrm{O}} = \mathbf{A}_{\mathrm{d}}\mathbf{V}_{\mathrm{d}} + \mathbf{A}_{\mathrm{c}}\mathbf{V}_{\mathrm{c}}$$

Where Vd = the difference voltage  $V_1$ - $V_2$

$Vc = the common mode voltage (V_1+V_2)/2$

#### Common Mode Rejection Ratio (CMRR)

The ability of a differential amplifier to reject common mode input signals is expressed in terms of common mode rejection ratio (CMRR). The common mode rejection ratio of a differential amplifier is mathematically given as the ratio of differential voltage gain of the differential amplifier to its common mode gain.

$$CMRR = |A_d / A_c|$$

Ideally, the common mode voltage gain of a differential amplifier is zero. Hence the CMRR is ideally infinite.

#### **Characteristics of a Differential Amplifier**

- High Differential Voltage Gain

- Low Common Mode Gain

- High Input Impedance

- Low Output Impedance

- High CMRR

- Large Bandwidth

- Low offset voltages and currents

### SCHOOL OF BIO AND CHEMICAL ENGINEERING

DEPARTMENT OF BIOMEDICAL ENGINEERING

UNIT – II –BIOSIGNAL CONDITIONING– SBMA1504

# **UNIT 2 APPLICATION OF OPAMPS**

# 2.1 Comparator

The change in the output state takes place with an increment in input  $V_i$ , of only 2 mV. This is the uncertainty region where output cannot be directly defined.

There are basically two types of comparators

- Non inverting comparator

- Inverting comparator

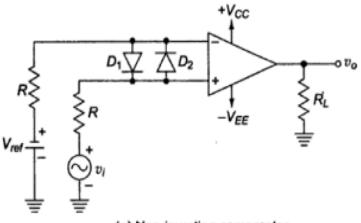

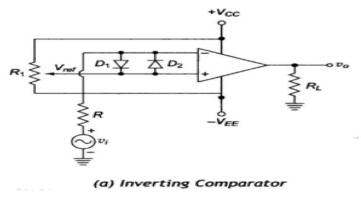

#### Non inverting comparator

• A Fixed reference voltage Vref is applied to (-) input and a time varying signal V<sub>i</sub> is applied to (+) input.

The output voltage

- Vo is at Vsat for  $V_i < Vref$ .

- Vo is at +Vsat for Vi > Vref.

- The diodes D1 and D2 are connected to protect the op-amp from excessive input voltages of Vref as shown in Fig.a.

#### (a) Non-inverting comparator

Fig: 2.1 Non-inverting Comparator

- The output waveform for a sinusoidal input signal applied to the (+) input is shown in Fig.

- Fig. for positive and negative Vref respectively

- In a practical circuit (Fig. d),

Vref is obtained by using a 10 k $\Omega$  potentiometer which forms a voltage divider with the supply voltages V+ and V- with the wiper connected to (-) input terminal.

Thus a Vref of desired amplitude and polarity is obtained by simply adjusting the 10 k $\Omega$  potentiometer.

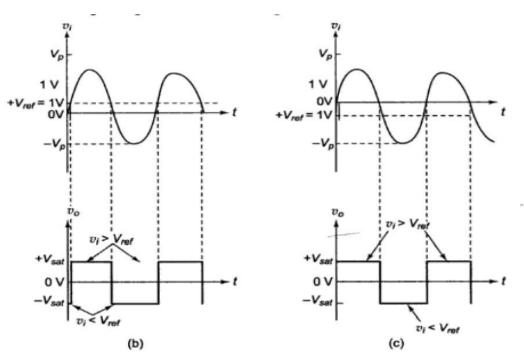

(b) Input and Output wave-forms when  $V_{ref}$  is +ve (c) Input and Output wave-forms when  $V_{ref}$  is -ve

Fig: 2.2 Non-inverting Comparator Waveforms

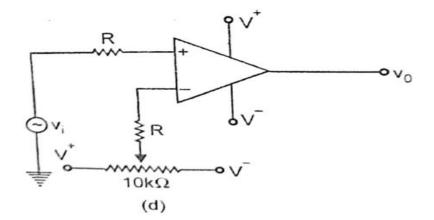

#### **Inverting comparator**

• In inverting comparator, reference voltage Vref is applied to the (+) input and V<sub>i</sub> is applied to input.

Fig: 2.3 Inverting Comparator

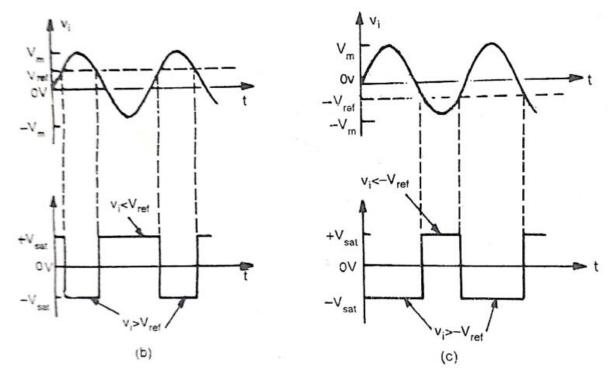

For a sinusoidal input signal, the output waveform is shown in Fig. (b) and (c) for Vref positive and negative respectively.

The output voltage

Vo is at +Vsat for  $V_i$  <Vref.

Vo is at - Vsat for Vi > Vref.

Fig: 2.4 Inverting Comparator Waveforms

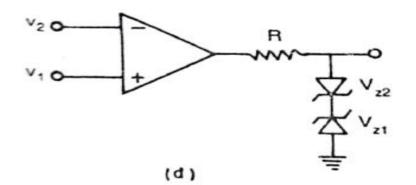

• Output voltage levels independent of power supply voltages can also be obtained by using a resistor R and two back to back zener diodes at the output of op-amp as shown in Fig.(d).

- The value of resistance R is chosen so the zener diodes operate at the recommended current.

- It can be seen that the limiting voltages of Vo, are  $(V_{Z1} + V_D)$  and  $(V_{Z1} + V_D)$  where  $V_D$  (- 0.7 V) is the diode forward voltage.

Fig: 2.5 Inverting Comparator

# **2.2 Zero Crossing Detectors**

#### Some important applications of comparator

- Zero crossing

- Window detector

- Time marker generator

- Phase meter

- •

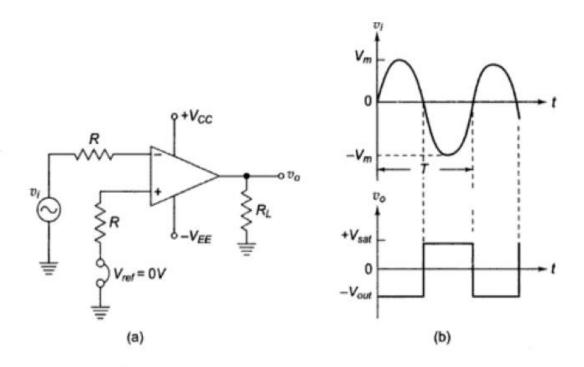

The basic comparators of can be used as a zero crossing detector provided that Vref in set to zero. An inverting zero- crossing detector is shown in Fig. (a) .The output waveform for a sinusoidal input signal is shown in Fig.(b). The circuit in also called a sine to square wave generator.

The output voltage

Vo is at +Vsat for  $V_i$  positive

Vo is at - Vsat for Vi negative

(a) Zero crossing detector and (b) Input and output waveforms

Fig: 2.6 Zero Crossing detector

# 2.3 Regenerative Comparator (Schmitt Trigger)

- If positive feedback is added to the comparator circuit, gain can be increased greatly.

- Consequently, the transfer curve of comparator becomes more close to ideal curve.

- Theoretically, if the loop gain  $-\beta A_{0L}$  is adjusted to unity, then the gain with feedback  $A_{Vf}$  becomes infinite. This results in an abrupt (zero rise time) transition between the extreme values of output voltage.

- In practical circuits, however, it may not be possible to maintain loop-gain exactly equal to unity for Long time because of supply voltage and temperature variations.

- So a value greater than unity is chosen. This also gives an output waveform virtually discontinuous at the comparison voltage. This circuit, however now exhibits a phenomenon called hysteresis or backlash.

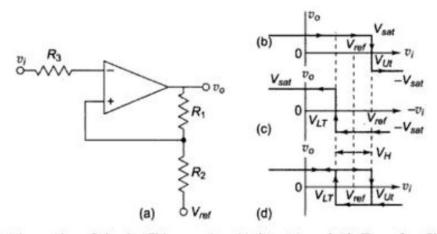

(a) Inverting Schmitt Trigger circuit (b), (c) and (d) Transfer Characteristics of Schmitt Trigger

#### Fig: 2.7 Schmitt Tigger

- Fig. (a) shows such a regenerative comparator. The circuit is also known as **Schmitt Trigger.**

- The input voltage is applied to the (-) input terminal and feedback voltage to the (+) input terminal.

- The input voltage  $V_i$  triggers the output  $V_o$  every time it exceeds certain voltage level.

- These voltage levels are called upper threshold voltage ( $V_{UT}$ ) and lower threshold voltage ( $V_{LT}$ ).

- The hysteresis width is the difference between these two threshold voltages ie.  $V_{UT}$   $V_{LT}$  .

- These threshold voltages are calculated as follows:

- Suppose the output  $V_o = + V_{sat}$  The voltage at (+) input terminal will be

$$V_{ref} + \frac{R_2}{R_1 + R_2} (V_{sat} - V_{ref}) = V_{UT}$$

- This voltage is called upper threshold voltage ( $V_{UT}$ ). As long as  $V_i$  is less than  $V_{UT}$ , the output Vo, remains constant at +  $V_{sat}$

- When  $V_i$  is just greater than  $V_{UT}$ , the output Vo regenerative switches to  $V_{sat}$  and remains at this level as long as  $V_i > V_{UT}$  Or as shown in Fig.(b).

- For ,  $Vo = -V_{sat}$  , the voltage at the (+) input terminal is,

$$V_{ref} - \frac{R_2}{R_1 + R_2} (V_{sat} + V_{ref}) = V_{LT}$$

- This voltage is referred to as lower threshold voltage V<sub>LT</sub>.

- The input voltage  $V_i$  must become lesser than  $V_{LT}$  in order to cause Vo to switch from  $V_{sat}$  to +  $V_{sat}$ .

- A regenerative transition takes place as shown in Fig.(c) and the output Vo returns from - V<sub>sat</sub> to + V<sub>sat</sub> almost instantaneously. The complete transfer characteristics are shown in Fig (d).

- Note that  $V_{LT} < V_{UT}$  and the difference between these two voltages is the hysteresis width  $V_H$  and can be written as

$$V_{H} = V_{UT} - V_{LT} = \frac{2R_{2}V_{sat}}{R_{1} + R_{2}}$$

- Because of the hysteresis, the circuit triggers at a higher voltage for increasing signals than for decreasing ones.

- Further, note that if peak-to-peak input signal  $V_i$  were smaller than  $V_H$  then the Schmitt trigger circuit, having responded at a threshold voltage by a transition in one direction would never reset itself, i.e, once the output has jumped to say. +Vsat it would remain at this level and never return to -V<sub>sat</sub>.

- It may be seen from Eq.  $V_H$  that hysteresis width  $V_H$  is independent of Vref.

- When Vref = 0V Then,

$$V_{UT} = -V_{LT} = \frac{R_2}{R_1 + R_2} V_{sat}$$

- A non inverting Schmitt trigger is obtained if Vi and Vref are interchanged in Fig. a.

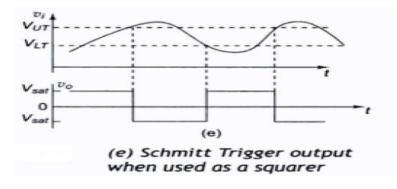

- The most important application of Schmitt trigger circuit is to convert a very slowly varying input voltage into a square wave output as shown in Fig. (e).

Fig: 2.8 Schmitt Tigger output

# **2.4 Peak Detectors**

- A peak detector is a circuit that produces an output voltage equal to the positive or negative peak value of the input voltage.

- A positive peak detector detects the positive peak magnitude of the input and a negative peak detector identifies the negative peak magnitude of the input.

The basic blocks required for the peak detector circuit are:

- an analog memory such as a capacitor to store the charge proportional to the peak value

- a unidirectional switch such as a diode to charge the capacitor when a new peak arrives at the input

- a device such as a voltage follower circuit for making the capacitor charge to the input voltage and a switch to periodically reinitialize the output to zero

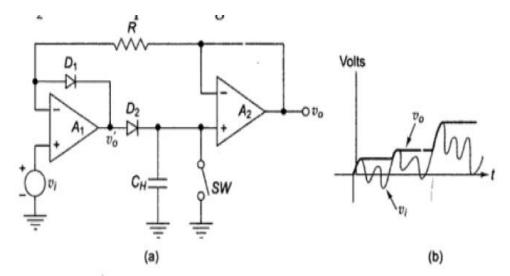

(a) Peak detector circuits and (b) Input and output waveforms

Fig: 2.9 Peak detectors

Figure (b) shows the voltage waveforms for the positive peak detector for a certain input signal  $v_i$ . The circuit can be reset at any time by closing the switch *SW*. The switch *SW* can be a low leakage MOSFET. Negative peak detectors can be obtained by reversing the diode connections.

- Figure (a) shows the circuit of a positive peak detector.

- The capacitor C<sub>H</sub>, diode D<sub>2</sub>, op-amp A<sub>1</sub>, and switch SW perform the four functions listed above in order.

- The op-amp  $A_2$ , acts as a buffer. This prevents discharging of the capacitor  $C_H$ .

- The diode D2 is preferred to be of very low leakage current.

- The diode D<sub>1</sub>, and resistance R avoids saturation of op-amp when a peak is detected.

- When the input signals  $V_i > 0$ , the output V'<sub>0</sub> of op amp A<sub>1</sub> is positive.

- The diode  $D_2$  is hence forward-biased and diode  $D_1$  is reverse-biased. The capacitance  $C_H$  then gets charged.

- The feedback path provided by diode  $D_{2}$ , op-amp  $A_2$  and resistor R maintain the virtual short between the input terminals of  $A_1$ .

- In other words, the voltages at the inverting and non-inverting terminals of A<sub>1</sub> are equal.

- Then, the voltage V<sub>i</sub>, during this phase is  $v_i = v_0 + V_{D2(ON)}$ .

- The output  $V_0$  tracks  $V_i$ , and this phase is called the track mode.

- The op-amp  $A_1$  sources current to charge  $C_H$  through diode  $D_2$ .

- When  $V_i$ , begins to decrease,  $D_2$ , becomes reverse-biased and  $D_1$ , becomes forward-biased and conducts.

- The output of V'<sub>0</sub> of op amp A<sub>1</sub> is now  $v_o = v_i V_{D1(ON)}$

- The feedback path from Vo, to  $V_i$  through diode  $D_2$  and R is now open. During this phase, the capacitor voltage remains constant. Hence it is called the hold mode, and the output of op-amp A<sub>2</sub>, retains the peak voltage.

## **2.5 Precision Rectifier**

- The ordinary diodes cannot rectify voltages below the cut-in -voltage of the diode.

- A circuit which can act as an ideal diode or precision signal processing rectifier circuit for rectifying voltages which are below the level of cut-in voltage of the diode can be designed by placing the diode in the feedback loop of an op-amp.

### **Precision Diodes**

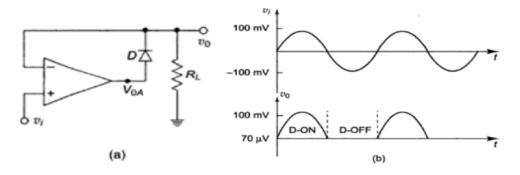

- It is a single diode arrangement and functions as a non-inverting precision half– wave rectifier circuit.

- If Vi in the circuit of figure is positive, the op-amp output  $V_0$  also becomes positive. Then the closed loop condition is achieved for the op-amp and the output voltage  $V_0 = V_1$ .

- When Vi < 0, the voltage  $V_0$  becomes negative and the diode is reverse biased. The loop is then broken and the output  $V_0 = 0$ .

(a) Precision diode and (b) Input and output waveforms

#### Fig: 2.10 Precision Diode

- Consider the open loop gain AOL of the op-amp is approximately  $10^4$  and the cut-in voltage V $\gamma$  for silicon diode is  $\approx 0.7$ V.

- When the input voltage Vi > V $\gamma$  / AOL, the output of the op-amp V<sub>O</sub> exceeds V $\gamma$  and the diode D conducts.

- Then the circuit acts like a voltage follower for input voltage level  $V_i > V_{\gamma} / AOL$ , (i.e. when  $V_i > 0.7/10^4 = 70 \mu V$ ),

- The output voltage  $V_0$  follows the input voltage during the positive half cycle for input voltages higher than  $70\mu V$  as shown in figure.

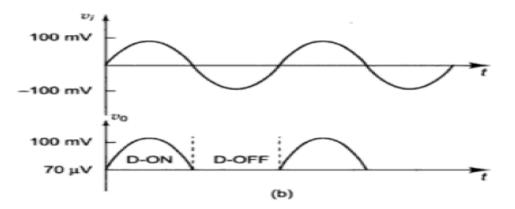

Fig: 2.11 Precision Diode Waveform

- When Vi is negative or less than  $V_{\gamma}$  /  $A_{OL}$ , the output of op-amp  $V_{OA}$  becomes negative, and the diode becomes reverse biased.

- The loop is then broken, and the op-amp swings down to negative saturation.

- However, the output terminal is now isolated from both the input signal and the output of the op-amp terminal thus  $V_0 = 0$ .

- No current is then delivered to the load RL except for the small bias current of the opamp and the reverse saturation current of the diode.

- This circuit is an example of a non-linear circuit, in which linear operation is achieved over the remaining region ( $V_i < 0$ ).

- Since the output swings to negative saturation level when  $V_i < 0$ , the circuit is basically of saturating form. Thus the frequency response is also limited.

Applications: The precision diodes are used in

Half wave rectifier, Full-wave rectifier,

Peak value detector, Clipper and clamper circuits.

#### **Disadvantage:**

• It can be observed that the precision diode as shown in figure operated in the first quadrant with Vi > 0 and  $V_0 > 0$ . The operation in third quadrant can be achieved by connecting the diode in reverse direction.

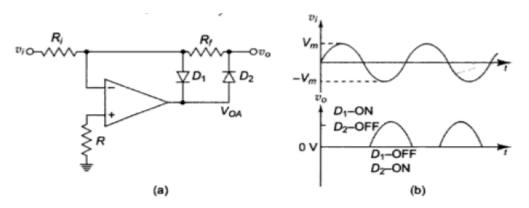

# 2.6 Half – wave Rectifier

- A non-saturating half wave precision rectifier circuit is shown in figure.

- When  $V_i > 0V$ , the voltage at the inverting input becomes positive, forcing the output  $V_{OA}$  to go negative.

- This results in forward biasing the diode  $D_1$  and the op-amp output drops only by  $\approx$  0.7V below the inverting input voltage. Diode  $D_2$  becomes reverse biased.

- The output voltage  $V_0$  is zero when the input is positive.

- When  $V_i < 0$ , the op-amp output  $V_{OA}$  becomes positive, forward biasing the diode  $D_2$  and reverse biasing the diode  $D_1$ .

- The circuit then acts like an inverting amplifier circuit with a non-linear diode in the forward path.

- The gain of the circuit is unity when  $R_f = R_i$ .

Fig: 2.12 Half wave Rectifier

The circuit operation can mathematically be expressed as

and  $v_o = 0$  when  $v_i > 0$  $v_o = -\frac{R_f}{R_i} v_i$  for  $v_i < 0$

The voltage V<sub>OA</sub> at the op-amp output is

and

$$V_{OA} \equiv -0.7 \text{ for } v_i > 0V$$

$$V_{OA} \equiv \frac{R_f}{R_i} v_i + 0.7 V \text{ for } v_i < 0V.$$

The op-amp is a high speed and this accommodates the abrupt changes in the value of V<sub>OA</sub> when V<sub>i</sub> changes sign and improves the frequency response characteristics of the circuit.

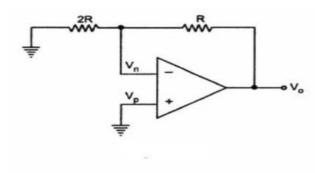

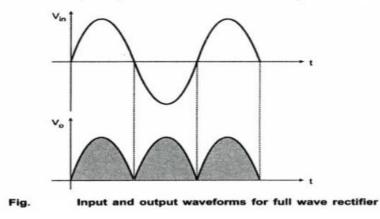

### 2.7 Full wave Rectifier

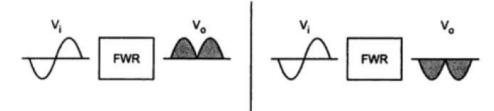

The fullwave rectifier circuits accept an ac signal at the input, inverts either the negative or the positive half, and delivers both the inverted and noninverted halves at the output, as shown in the Fig.

Fig. Positive and negative full wave rectifiers

The operation of the positive full wave rectifier is expressed as

$$V_0 = |V_i|$$

... (1)

and that of the negative rectifier as

$$v_0 = -|V_i|$$

... (2)

Looking at equations 1 and 2 we can say that precision full wave rectifier circuits are precision absolute value circuits.

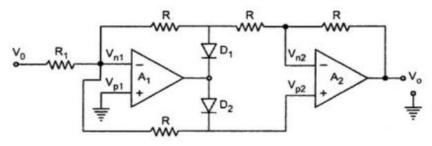

Fig. Full wave rectifier

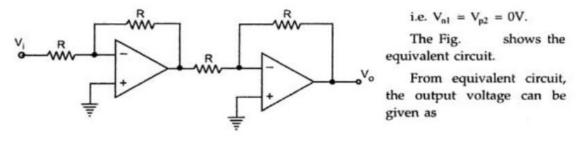

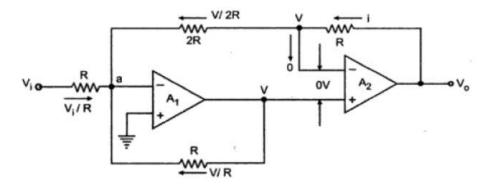

**CASE 1**:  $V_i > 0$ : When  $V_i > 0$ , inverting side of  $A_1$  will force its output to swing negative, thus forward biasing  $D_1$  and reverse biasing  $D_2$ . Since no current flows through resistance R connected between  $V_{n1}$  and  $V_{p2}$ , both are equipotential.

$$V_{o} = \left(\frac{-R}{R}\right) - \left(\frac{R}{R}\right) V_{i} = V_{i} \qquad \dots (3)$$

**CASE 2**:  $V_i < 0$ : When  $V_i < 0$ , negative, the output voltage of  $A_1$  swings to positive, making diode  $D_1$  reverse biased and diode  $D_2$  forward biased.

The Fig. shows the equivalent circuit.

Let the output voltage of op-amp  $A_1$  be V. Since the differential input to  $A_2$  is zero, the inverting input terminal is also at voltage V, as shown in the Fig.

Applying KCL at node 'a' we have

$$\frac{V_i}{R} + \frac{V}{2R} + \frac{V}{R} = 0$$

$$\frac{3V}{2R} = \frac{-V_i}{R}$$

$$V = \frac{-2}{3}V_i \qquad \dots (4)$$

...

To find  $V_{o}$  in terms of V we concentrate on the equivalent circuit of  $A_{2}$  , as shown in the Fig.

$$\therefore \mathbf{V}_{o} = \left(1 + \frac{\mathbf{R}}{2\mathbf{R}}\right) \mathbf{V} = \left(\frac{2\mathbf{R} + \mathbf{R}}{2\mathbf{R}}\right) \mathbf{V} = \frac{3}{2}\mathbf{V}$$

... (5)

Substituting value of V in above equation we get,

$$V_o = \frac{3}{2} \left( \frac{-2}{3} V_i \right) = -V_i$$

... (6)

Hence for  $V_i < 0$  the output is positive. This is illustrated in Fig.

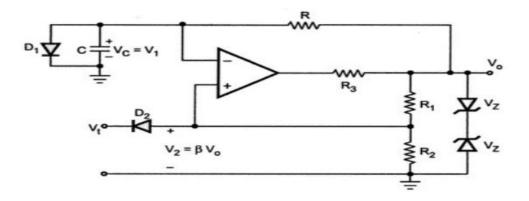

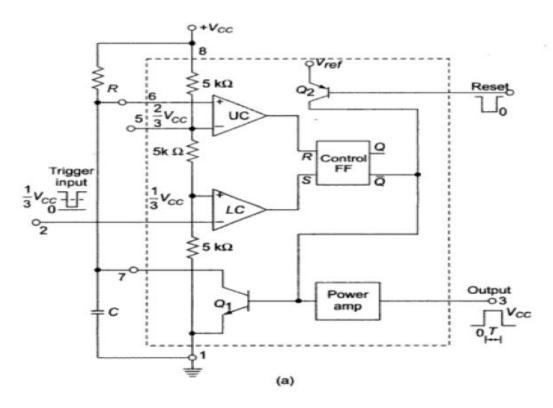

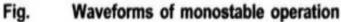

## 2.8 Monostable Multivibrator

- The monostable multivibrator is also called as the one-shot multivibrator.

- The circuit produces a single pulse of specified duration in response to each **external trigger** signal. For such a circuit, only one **stable state** exists.

- When an external trigger is applied, the output changes its state. The new state is called as a quasi-stable state.

- The circuit remains in this state for a fixed interval of time. After some time it returns back to its original stable state.

- In fact, an internal trigger signal is generated which drives the circuit back to its original stable state.

- Usually, the **charging and discharging of a capacitor** provide this internal trigger signal.

Fig: 2.13 Monostable Multivibrators

- The diode  $D_1$  connected across the capacitor is called clamping diode. It clamps the capacitor voltage to 0.7 V when the output is at +  $V_{sat}$ .

- A negative triggering pulse is applied to the Non-inverting terminal of Op-amp through RC differentiator circuit and diode D<sub>2</sub>.

## **Operation of the Circuit**

(i).To understand the operation of the circuit, let us assume that the output Vo is  $at + V_{sat}$ , i.e. in its stable state.

(ii). The diode  $D_1$  (Connected across Capacitor) conducts and the voltage across the capacitor  $C = V_C$  gets clamped to 0.7 Volts.

(iii). The voltage at the non-inverting terminal is controlled by voltage divider circuit of  $R_1$  and  $R_2$

• Voltage at non-inverting terminal  $(V_2) = +\beta V_0$

$$\beta = \frac{R_2}{R_1 + R_2}$$

(iv). If  $V_T$ , a negative trigger of amplitude  $V_T$  is applied to the non-inverting terminal, so that the effective voltage at this terminal is less than 0.7 V=>then the output of the Op-amp changes its state from +  $V_{sat}$  to -  $V_{sat}$ .

(v). The diode is now reverse biased and the capacitor starts charging exponentially to -  $V_{sat}$  through resistance R. The voltage at the non-inverting terminal is now -  $\beta V_{sat}$ . When the capacitor voltage becomes just slightly more negative than -  $\beta V_{sat}$ , the output of the Op-amp changes its state back to +  $V_{sat}$ .

(vi).The capacitor now starts charging towards +  $V_{sat}$  through R until  $V_C$  reaches 0.7V as capacitor gets clamped to the voltage.

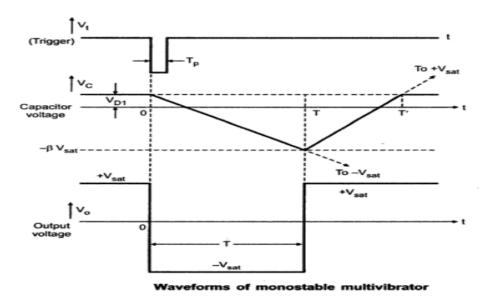

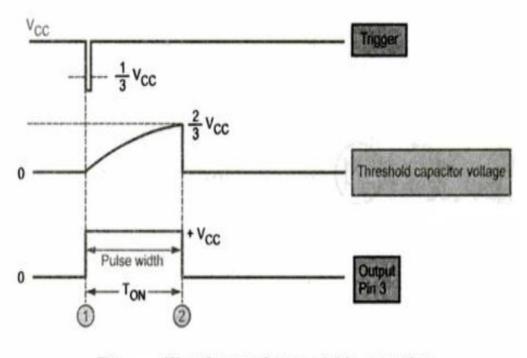

The waveforms are shown in the Fig.

Fig: 2.14 Monostable Multivibrator Waveform

#### Expression for Pulse Width T

```

For a low pass RC circuit let,

```

$V_i$  = initial value of the voltage  $V_f$  = final value of the voltage

Then the general solution is given by,

$$V_o = V_f + (V_i - V_f) e^{-t/RC}$$

... (1)

Now for the monostable multivibrator discussed above, the values of Vf and Vi are,

$$V_{f} = -V_{sat} \text{ and } V_{i} = V_{D1} \text{ (diode forward voltage)}$$

while

$$V_{o} = \text{ output} = \text{ capacitor voltage} = V_{C}$$

$$\therefore \qquad V_{C} = -V_{sat} + (V_{D1} - [-V_{sat}]) e^{-t/RC} \qquad \dots (2)$$

at  $t = T$ ,

$$V_{C} = -\beta V_{sat} \qquad \dots (3)$$

$$\therefore \qquad -\beta V_{sat} = -V_{sat} + (V_{D1} + V_{sat}) e^{-T/RC} \qquad \dots (4)$$

$$\therefore \qquad (V_{D1} + V_{sat}) e^{-T/RC} = V_{sat} (1 - \beta)$$

$$\therefore \qquad e^{-T/RC} = \frac{V_{sat} (1 - \beta)}{(V_{D1} + V_{sat})}$$

$$\therefore \qquad T = RC \ln \left[\frac{1 + V_{D1} / V_{sat}}{1 - \beta}\right] \qquad \dots (5)$$

This is obtained by absorbing negative sign inside the natural logarithm.

The potential divider decides the value of ß given by,

$$\beta = \frac{R_2}{R_1 + R_2} ... (6)$$

If  $V_{sat} >> V_{D1}$  and  $R_1 = R_2$  so that  $\beta = 0.5$ , then  $T_1 = 0.69 \text{ BC}$

$$T = 0.69 RC$$

... (7)

For monostable operation, the trigger pulse width T<sub>p</sub> should be much less than T, the pulse width of the monostable multivibrator.

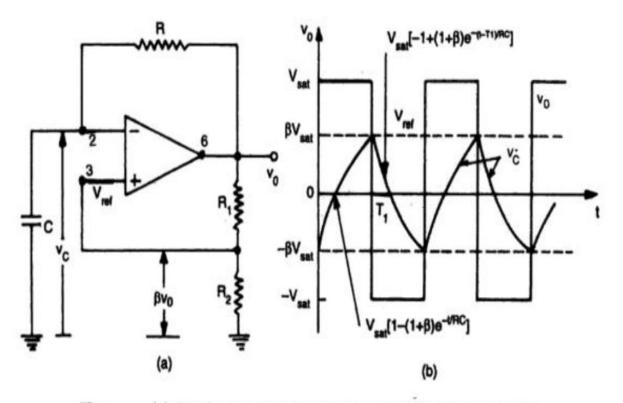

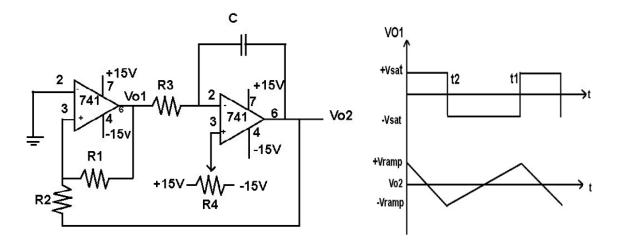

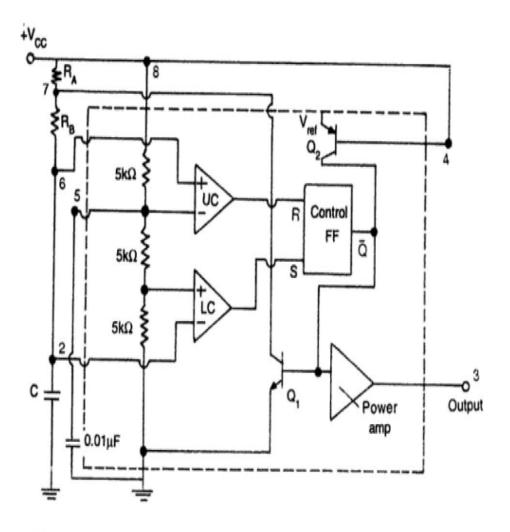

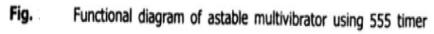

# 2.9 ASTABLE MULTIVIBRATOR

- A simple op-amp square wave generator is shown in Fig (a). Also called a free running oscillator, the principle of generation of square wave output is to force an op-amp to operate in the saturation region.

- In Fig. (a) Fraction  $\beta = R_2/(R_1+R_2)$  of the output is fed back to the (+) input terminal. Thus the reference voltage Vref is  $\beta$ Vo, and may take values as +  $\beta$ Vsat or  $\beta$ Vsat.

- The output is also fed back to the (-) input terminal after integrating by means of a low-pass RC combination. Whenever input at the (-) input terminal just exceeds Vref switching takes place resulting in a square wave output.

- In Astable multivibrator, both the states are quasi stable.

- Consider an instant of time when the output is at +Vsat. The capacitor now starts charging towards +Vsat through resistance R, as shown in Fig (b).

- The voltage at the (+) input terminal in held at  $+\beta$ Vsat by R<sub>1</sub> and R<sub>2</sub> combination. This condition continues as the charge on C rises, until it has just exceeded +  $\beta$ Vsat the reference voltage.

- When the voltage at the (-) input terminal becomes just greater than this reference voltage, the output is driven to Vsat.

- At this instant, the voltage on the capacitor is  $+\beta$ Vsat. It begins to discharge through R. that is charges toward Vsat.

- When the output voltage switches to -Vsat, the capacitor charges more and more negatively until its voltage just exceeds - BVsat. The output switches back to +Vsat. The cycle repeats itself as shown in Fig.

(a) Simple op-amp square wave generator (b) waveforms

Fig: 2.15 Astable Multivibrator

The frequency is determined by the time it takes the capacitor to charge from  $-\beta V_{\text{sat}}$  to  $+\beta V_{\text{sat}}$  and vice versa. The voltage across the capacitor as a function of time is given by,

$$v_c(t) = V_f + (V_i - V_f)e^{-t/RC}$$

where, the final value,  $V_{\rm f} = + V_{\rm sat}$ and the initial value,  $V_{\rm i} = -\beta V_{\rm sat}$

Therefore,

or

$$v_{c}(t) = V_{sat} + (-\beta V_{sat} - V_{sat}) e^{-t/RC}$$

$$v_{c}(t) = V_{sat} - V_{sat} (1 + \beta) e^{-t/RC}$$

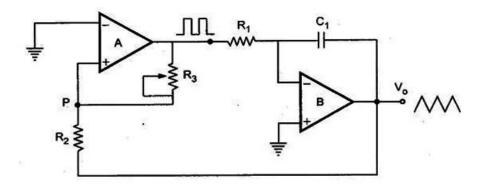

#### 2.10 TRIANGULAR WAVE GENERATOR

It consists of a comparator (A) and an integrator (B) as shown in Figure 1.1. The output of comparator A is a square wave of amplitude  $\pm$ Vsat and is applied to the inverting (-) input terminal of the integrator B. The output of integrator is a triangular wave and it is feedback as input to the comparator A through a voltage divider R<sub>2</sub>R<sub>3</sub>.

Fig: 2.16 Triangular Wave Generator

To understand circuit operation, assume that the output of comparator A is at +  $V_{sat}$ . This forces a constant current (+  $V_{sat}$ /  $R_1$ ) through C to give a negative going ramp at the output of the integrator, as shown in the Fig. Therefore, one end of voltage divider is at a voltage + $V_{sat}$  and the other at the negative going ramp. When the negative going ramp reaches a certain value - $V_{ramp}$ , the effective voltage at point p becomes slightly below 0V.

As a result, the output of comparator A switches from positive saturation to negative saturation ( $-V_{sat}$ ). This forces a reverse constant current (right to left) through C to give a positive going ramp at the output of the integrator, as shown in the Fig. 2.89. When positive going ramp reaches +  $V_{ramp}$ , the effective voltage at point p becomes slightly above 0V. As a result, the output of comparator A switches from negative saturation to positive saturation (+ $V_{sat}$ ). The sequence then repeats to give triangular wave at the output of integrator B.

#### **Amplitude and Frequency Calculations:**

The frequency and amplitude of the Triangular Wave Generator Using Op amp wave can be determined as follows:

When comparator output is at  $+V_{sat}$ , the effective voltage at point P is given by

$$-V_{ramp} + \frac{R_2}{R_2 + R_3} \left[ + V_{sat} - (-V_{ramp}) \right] \qquad ... (1)$$

When effective voltage at P becomes equal to zero, we can write above equation

$$-V_{ramp} + \frac{R_2}{R_2 + R_3} \left[ +V_{sat} - (-V_{ramp}) \right] = 0$$

$$-V_{ramp} + \frac{R_2}{R_2 + R_3} (V_{ramp}) + \frac{R_2}{R_2 + R_3} (+V_{sat}) = 0$$

$$\frac{-R_3}{R_2 + R_3} (V_{ramp}) = -\frac{R_2}{R_2 + R_3} (+V_{sat})$$

$$\therefore \qquad -V_{ramp} = \frac{-R_2}{R_3} (+V_{sat}) \qquad \dots (2)$$

Similarly, when comparator output is at -V  $_{\text{sat}}$  , we can write,

$$V_{ramp} = \frac{-R_2}{R_3}(-V_{sat})$$

... (3)

The peak to peak amplitude of the triangular wave can be given as

$$V_{o(pp)} = +V_{ramp} - (-V_{ramp}) \qquad ... (4)$$

=  $\frac{-R_2}{R_3}(-V_{sat}) - (\frac{-R_2}{R_3})(+V_{sat})$

If  $|+V_{sat}| = |-V_{sat}|$  then, we can write

35 37

$$V_{o(pp)} = \frac{R_2}{R_3} V_{sat} + \frac{R_2}{R_3} V_{sat} = \frac{2R_2}{R_3} V_{sat} \dots (5)$$

The time taken by the output to swing from  $-V_{ramp}$  to  $+V_{ramp}$  (or from  $+V_{ramp}$  to  $-V_{ramp}$ ) is equal to half the time period T/2. Refer Fig. 2.89. This time can be calculated from the integrator output equation as follows :

$$V_{o(pp)} = -\frac{1}{R_1 C_1} \int_0^{T/2} (-V_{sat}) dt = \left(\frac{V_{sat}}{R_1 C_1}\right) \frac{T}{2} \qquad ... (6)$$

$$T = \frac{2 R_1 C_1 V_{o(pp)}}{V_{sat}} \qquad ... (7)$$

Substituting value of  $V_{o(pp)}$  we get,

.

$$T = \frac{2R_1 C_1 \left(\frac{2R_2}{R_3} V_{sat}\right)}{V_{sat}} = \frac{4R_1 C_1 R_2}{R_3} \qquad \dots (8)$$

Therefore, the frequency of oscillation can be given as,

$$f_o = \frac{1}{T} = \frac{R_3}{4 R_1 C_1 R_2}$$

... (9)

# 2.11 SAWTOOTH WAVE GENERATOR

- Saw tooth waveform can be also generated by an asymmetrical astable multivibrator followed by an integrator.

- The saw tooth wave generators have wide application in time-base generators and pulse width modulation circuits.

- The difference between the triangular wave and saw tooth waveform is that the rise time of triangular wave is always equal to its fall of time

- while in saw tooth generator; rise time may be much higher than its fall of time, vice versa.

Fig: 2.17 Saw tooth Wave Generator

- The triangular wave generator can be converted in to a saw tooth wave generator by injecting a variable dc voltage into the non inverting terminal of the integrator. In this circuit a potentiometer is used (47K).

- when the wiper moves towards -V, the rise time of the saw tooth become longer than the fall time. If the wiper moves towards +V, the fall time becomes more than the rise time.

- Reason is when comparator output is at -ve saturation. When wiper moves to -ve supply, a negative voltage is added to inverting terminal.

- This causes the potential difference across R1 decreases and hence the current through the resistor and capacitor decreases. Then slope of the output, I/C decreases and in turn rise time decreases.

- When the comparator output goes positive, due to presence of negative voltage at the inverting terminal, potential difference of across the resistor R1 increases and hence current increases. Then slope increases and fall time decreases. And obtained output as saw tooth wave.

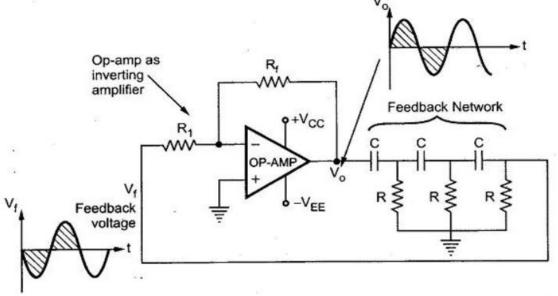

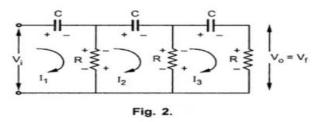

# 2.12 SINE WAVE GENERATORS R-C phase shift oscillator

- R-C phase shift oscillator using op-amp uses an op-amp in inverting amplifier mode. Thus it introduces the phase shift of 180° between input and output.

- The feedback network consists of 3 RC sections each producing 60° phase shift. Such an RC phase shift oscillator using op-amp is shown in Fig.

- The output of the amplifier is given to the feedback network. The output of the feedback network drives the amplifier.

- The total phase shift around a loop is 180° of the amplifier and 180° due to 3 RC sections, thus 360°. This satisfies the required condition for positive feedback and circuit works as an oscillator.

Fig: 2.18 R-C Phase shift oscillator using op-amp

Let us find the transfer function of the RC feedback network :

Applying KVL to various loops we get,

$$I_1\left(R + \frac{1}{j\omega C}\right) - I_2 R = V_i \qquad \dots (15)$$

$$-I_1 R + I_2 \left(2R + \frac{1}{j\omega C}\right) - I_3 R = 0 \qquad \dots (16)$$

$$0 - I_2 R + I_3 \left( 2R + \frac{1}{j\omega C} \right) = 0 \qquad \dots (17)$$

Replacing j $\omega$  by s and writing the equations in the matrix form,

$$\begin{vmatrix} R + \frac{1}{sC} & -R & 0 \\ -R & 2R + \frac{1}{sC} & -R \\ 0 & -R & 2R + \frac{1}{sC} \end{vmatrix} \begin{bmatrix} I_1 \\ I_2 \\ I_3 \end{bmatrix} = \begin{bmatrix} V_i \\ 0 \\ 0 \end{bmatrix} \qquad \dots (18)$$

Using the Crammer's rule to obtain  $I_3$

$$D = \begin{vmatrix} \frac{1+sRC}{sC} & -R & 0\\ -R & \frac{1+2sRC}{sC} & -R\\ 0 & -R & \frac{1+2sRC}{sC} \end{vmatrix}$$

$$= \frac{(1+sRC)(1+2sRC)^2}{s^3 C^3} - \frac{R^2(1+2sRC)}{sC} - \frac{R^2(1+sRC)}{sC}$$

$$= \frac{(1+sRC)(1+4sRC+4s^2 C^2 R^2) - R^2 s^2 C^2 [1+2sRC+1+sRC]}{s^3 C^3}$$

$$= \frac{1+5sRC+8s^2 C^2 R^2 + 4s^3 C^3 R^3 - 3s^3 R^3 C^3 - 2R^2 s^2 C^2}{s^3 C^3}$$

$$= \frac{1+5sRC+6s^2 C^2 R^2 + s^3 C^3 R^3}{s^3 C^3} \qquad \dots (19)$$

$$D_3 = \begin{vmatrix} \frac{1+sRC}{sC} & -R & V_i \\ -R & \frac{1+2sRC}{sC} & 0 \\ 0 & -R & 0 \end{vmatrix}$$

$$= V_i R^2 \qquad \dots (20)$$

$$I_3 = \frac{D_3}{D} = \frac{V_i R^2 s^3 C^3}{1 + 5 sRC + 6s^2 C^2 R^2 + s^3 C^3 R^3}$$

Now

...

$$V_o = V_f = I_3 R = \frac{V_i R^2 s^3 C^3}{1 + 5 sRC + 6 s^2 C^2 R^2 + s^3 C^3 R^3} \dots (21)$$

*.*:.

. ..

...

*.*..

$$\beta = \frac{V_o}{V_i} = \frac{R^3 s^3 C^3}{1 + 5 s C R + 6 s^2 C^2 R^2 + s^3 C^3 R^3} \qquad \dots (22)$$

Replacing s by  $j\omega$ ,  $s^2$  by  $-\omega^2$ ,  $s^3$  by  $-j\omega^3$

$$\beta = \frac{-j\omega^{3}R^{3}C^{3}}{1+5j\omega CR - 6\omega^{2}C^{2}R^{2} - j\omega^{3}C^{3}R^{3}}$$

Dividing numerator and denominator by  $-j\omega^3 R^3 C^3$  and replacing  $\frac{1}{\omega RC}$  by  $\alpha$  we get,

$$\beta = \frac{1}{1+6j\alpha-5\alpha^2-j\alpha^3}$$

$$\beta = \frac{1}{(1-5\alpha^2)+j\alpha(6-\alpha^2)} \qquad \dots (23)$$

To have phase shift of 180°, the imaginary part in the denominator must be zero.

$$\alpha (6 - \alpha^2) = 0$$

$$\alpha^2 = 6$$

$$\alpha = \sqrt{6}$$

$$\frac{1}{\omega RC} = \sqrt{6}$$

$$\omega = \frac{1}{RC\sqrt{6}}$$

$f = \frac{1}{2\pi RC\sqrt{6}} \qquad \dots (10)$

This is the frequency with which circuit oscillates. At this frequency,

$$\beta = \frac{1}{1 - 5 \times (\sqrt{6})^2} = -\frac{1}{29}$$

Negative sign indicates phase shift of 180°

$$|\beta| = \frac{1}{29}$$

... (11)

Now to have the oscillations,  $|A\beta| \ge 1$

$$|A| |\beta| \ge 1$$

$$|A| \ge \frac{1}{|\beta|} \ge \frac{1}{\left(\frac{1}{29}\right)}$$

$$|A| \ge 29 \qquad \dots (12)$$

**Key Point**: For the oscillations to occur, the gain of the op-amp must be equal to or greater than 29, which can be adjusted using the resistances  $R_f$  and  $R_i$ .

- Thus circuit will work as an oscillator which will produce a sinusoidal waveform if the gain is 29 and total phase shift around a loop is 360°.

- This satisfies the Barkhausen criterion for the oscillator. These oscillators are used over the audio frequency range i.e. about 20 Hz up to 100 kHz.

### **Advantages**

- The advantages of R-C phase shift oscillator are,

- The circuit is simple to design.

- Can produce output over the audio frequency range.

- Produces sinusoidal output waveform.

- It is a fixed-frequency oscillator.

### **Disadvantages**

- By changing the values of R and C, the frequency of the oscillator can be changed. But the values of R and C of all three sections must be changed simultaneously to satisfy the oscillating conditions. But this is practically impossible. Hence the phase shift oscillator is considered as a fixed frequency oscillator, for all practical purposes.

- And the frequency stability is poor due to the changes in the values of various components, due to the effect of temperature, ageing etc.

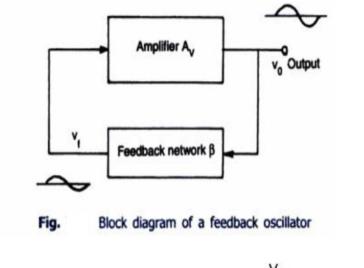

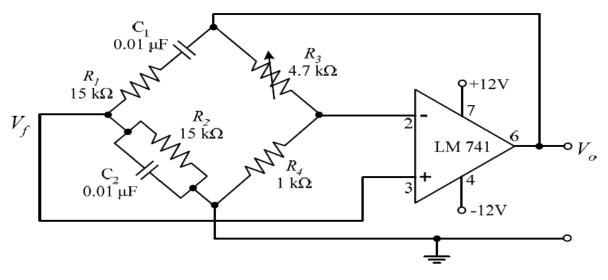

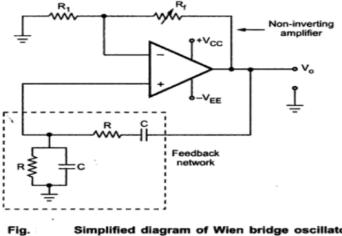

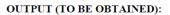

# 2.13 Wien Bridge Oscillator Using Opamp

An oscillator is a circuit that produces periodic electric signals such as sine wave or square wave. The application of oscillator includes sine wave generator, local oscillator for synchronous receivers etc.

An oscillator consists of an amplifier and a feedback network.

1. Active device i.e. opamp is used as an amplifier.

2. Passive components such as R-C or L-C combinations are used as feedback network.

To start the oscillation with the constant amplitude, positive feedback is not the only sufficient condition. Oscillator circuit must satisfy the following two conditions known as

### **Barkhausen conditions:**

- 1. Magnitude of the loop gain (Av  $\beta$ ) = 1,

- where, Av = Amplifier gain and

$\beta$  = Feedback gain.

2. Phase shift around the loop must be  $360^{\circ}$  or  $0^{\circ}$ .

Fig 2 Circuit diagram of Wien bridge oscillator using opamp.

- Wien bridge oscillator is an audio frequency sine wave oscillator of high stability and simplicity.

- The feedback signal in this circuit is connected to the non-inverting input terminal. so that the op-amp is working as a non-inverting amplifier. Therefore, the feedback network need not provide any phase shift.

- The circuit can be viewed as a Wien bridge with a series combination of R1 and C1 in one arm and parallel combination of R2 and C2 in the adjoining arm. Resistors R3 and R4 are connected in the remaining two arms.

- The condition of zero phase shift around the circuit is achieved by balancing the bridge.

- The series and parallel combination of RC network form a lead-lag circuit.

- At high frequencies, the reactance of capacitor C1 and C2 approaches zero. This causes C1 and C2 appears short. Here, capacitor C2 shorts the resistor R2. Hence, the output voltage Vo will be zero since output is taken across R2 and C2 combination. So, at high frequencies, circuit acts as a 'lag circuit'.

- At low frequencies, both capacitors act as open because capacitor offers very high reactance. Again, output voltage will be zero because the input signal is dropped across the R1 and C1 combination. Here, the circuit acts like a 'lead circuit'.

- But at one particular frequency between the two extremes, the output voltage reaches to the maximum value. At this frequency only, resistance value becomes equal to capacitive reactance and gives maximum output. Hence, this frequency is known as oscillating frequency (*f*).

Consider the feedback circuit shown in fig 3 On applying voltage divider rule,

$$V_f(s) = \frac{V_o(s) \times Z_P(s)}{Z_P(s) + Z_S(s)}$$

where,  $Z_S(s) = R_1 + \frac{1}{sC_1}$  and  $Z_P(s) = R_2 \parallel \frac{1}{sC_2}$

Let,  $R_1 = R_2 = R$  and  $C_1 = C_2 = C$ . On solving,

feedback gain,

$$\beta = \frac{V_f(s)}{V_o(s)} = \frac{RsC}{\left(RsC\right)^2 + 3RsC + 1}$$

(1)

$$Z_{s} \begin{cases} \frac{1}{sC_{1}} \\ R_{I} \\ R_{I}$$

Since the op-amp is operated in the non-inverting configuration the voltage gain,

$$A_{\nu} = \frac{V_o(s)}{V_f(s)} = 1 + \frac{R_3}{R_4}$$

(2)

Applying the condition for sustained oscillations,  $A_{\nu}\beta = 1$

Substitute equations (1) & (2), we get,

$$\left(1 + \frac{R_3}{R_4}\right) \left(\frac{RsC}{\left(RsC\right)^2 + 3RsC + 1}\right) = 1$$

Substitute  $s = j\omega$

$$\left(1 + \frac{R_3}{R_4}\right) \left(\frac{j\omega RC}{-R^2 C^2 \omega^2 + 3j\omega RC + 1}\right) = 1$$

$$\left(1 + \frac{R_3}{R_4}\right) j\omega RC = \left(-R^2 C^2 \omega^2 + 3j\omega RC + 1\right)$$

$$j\omega \left[\left(1 + \frac{R_3}{R_4}\right) RC - 3RC\right] = 1 - R^2 C^2 \omega^2$$

To obtain the frequency of oscillation equate the real part to zero.

$$1 - R^2 C^2 \omega^2 = 0$$

$$\omega = \frac{1}{RC}$$

$$f = \frac{1}{2\pi RC}$$

#### SIMPLIFIED DESIGN:

Frequency of oscillation,  $f = \frac{1}{2\pi\sqrt{R_1C_1R_2C_2}}$

Let,  $R_1 = R_2 = R$  and  $C_1 = C_2 = C$

$$f = \frac{1}{2\pi RC}$$

# Advantages

The various advantages of Wien bridge oscillator are,

- 1. By varying the two capacitor values simultaneously, by mounting them on the common shaft, different frequency ranges can be obtained.

- 2. The perfect sine wave output is possible.

- 3. It is useful audio frequency range i.e. 20 Hz to 100 kHz.

### SCHOOL OF BIO AND CHEMICAL ENGINEERING

DEPARTMENT OF BIOMEDICAL ENGINEERING

UNIT – III – BIOSIGNAL CONDITIONING – SBMA1504

## **Unit 3 Filters**

## **3.1 Introduction**

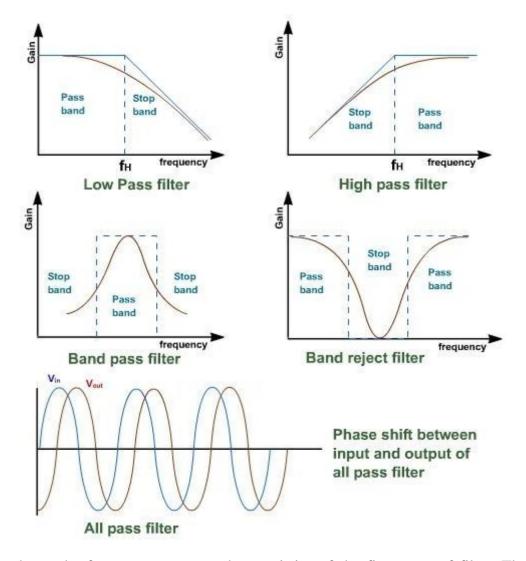

A filter is a frequency selective circuit that, passes a specified band of frequencies and blocks or attenuates signals of frequencies outside this band. Filter may be classified on a number of ways.

- 1. Analog or digital

- 2. Passive or active

- 3. Audio or radio frequency

Analog filters are designed to process only signals while digital filters process analog signals using digital technique. Depending on the type of elements used in their consideration, filters may be classified as passive or active.

Elements used in passive filters are resistors, capacitors and inductors.

Active filters, on the other hand, employ transistors or OPAMPs, in addition to the resistor and capacitors. Depending upon the elements the frequency range is decided. RC filters are used for audio or low frequency operation. LC filters are employed at RF or high frequencies.

The most commonly used filters are these:

- 1. Low pass filters

- 2. High pass filter

- 3. Band pass filter

- 4. Band reject filter.

- 5. All pass filter

A low pass filter has a constant gain from 0 Hz to a high cut-off frequency  $f_H$ . Therefore, the bandwidth is  $f_H$ . At  $f_H$  the gain is down by 3db. After that the gain decreases as frequency increases. The frequency range 0 to  $f_H$  Hz is called pass band and beyond  $f_H$  is called stop band.

Similarly, a high pass filter has a constant gain from very high frequency to a low cut-off frequency  $f_L$ . Below  $f_L$  the gain decreases as frequency decreases. At  $f_L$  the gain is down by 3db. The frequency range  $f_L$  Hz to  $\infty$  is called pass band and below  $f_L$  is called stop band.

**Fig. 1**, shows the frequency response characteristics of the five types of filter. The ideal response is shown by dashed line. While the solid lines indicates the practical filter response.

# 3.2 Low Pass filter

A **low-pass filter** (LPF) is a **filter** that **passes** signals with a **frequency lower** than a selected cut off **frequency** and attenuates signals with frequencies higher than the cut off **frequency**.

Wing Laplace Transform

$$\frac{V_{0}(s)}{V_{i}(s)} = \frac{A_{0}}{1 + RCs}$$

$$W_{h} = \frac{1}{RC} \therefore H(s) = \frac{V_{0}(s)}{V_{i}(s)} = \frac{A_{0}}{1 + \frac{s}{W_{h}}} = \frac{A_{0}W_{h}}{s + W_{h}} - (2)$$

$$Sub s = jw in (2) \qquad H(jw) = A_{0} \qquad 1 + jW_{w_{h}} = \frac{A_{0}}{1 + j(f_{f_{h}})}$$

$$= \frac{A_{0}}{1 + jW_{RC}} \quad \text{where} \qquad f = \frac{W}{2\pi}$$

$$f_{h} = \frac{1}{2\pi RC}$$

1) At Very low grequency

(ie)

$$f \leq f \leq f_h |H(jw)| \geq A_0$$

2) At  $f = f_h |H(jw)| = \frac{A_0}{1+(j+f_h)} = \frac{A_0}{1+j}$

$\left[|H(jw)| = \frac{A_0}{\sqrt{2}} = 0.707A_0$

3) At Very high grequency  $f >> f_h$

$|H(jw)| = \langle A_0 \approx 0$

$\Rightarrow LPF$  has maximum gain,  $A_0 = f_{f=0} = H_2$

the maximum gain  $A_0$ .

$\Rightarrow The grequency range from o to  $f_h$

$is called the pass band$

$\Rightarrow At 2 > 7$$

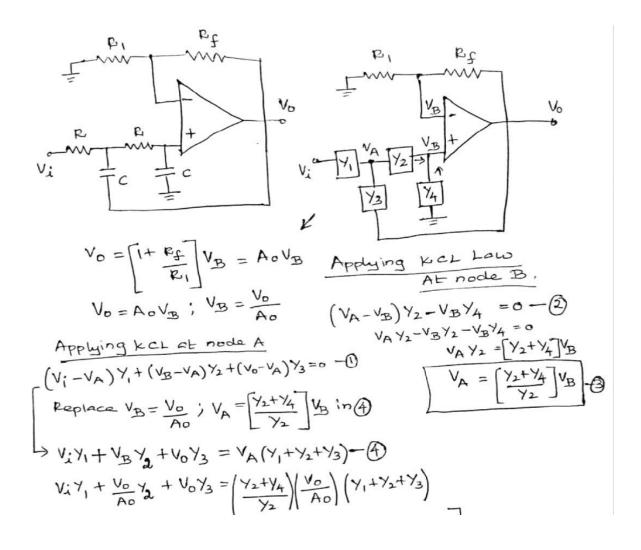

#### **3.3 Second Order Low Pass Filter**

A second order LPF having a gain 40dB/decade in stop band. A First order LPF can be converted into a II order type simply by using an additional RC network.

SECOND ORDER LOW PASS FILTER: [Sallen-Kay filter] OAn improved filter response can be obtained by using A second order active filter.

@A second order filter consists of two RC pausand has a roll-off rate of -40 dB/decade.

& the op-amp is connected as non-inverting amplifier.

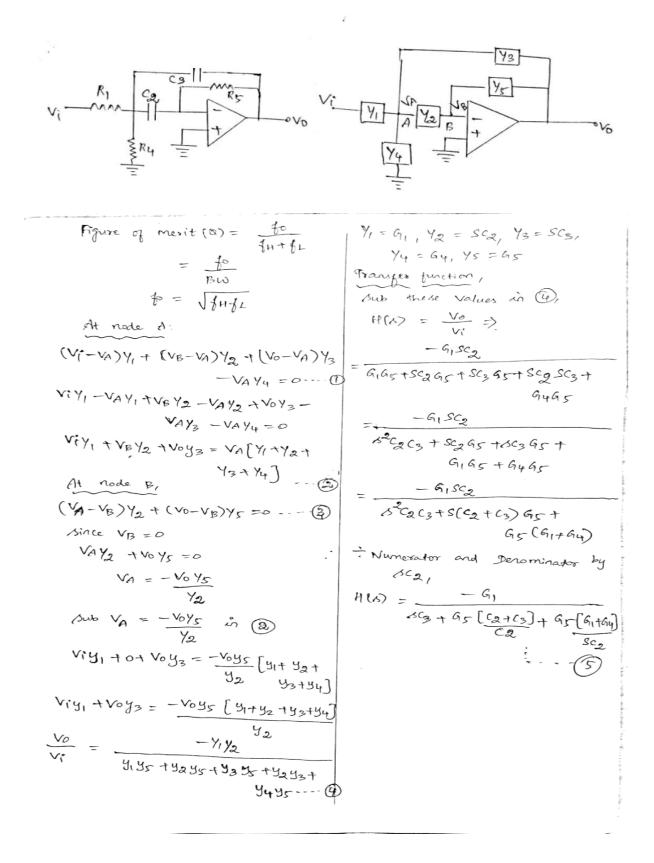

$$\begin{aligned} V_{i}Y_{1} + \frac{V_{0}Y_{2}}{A_{0}} + V_{0}Y_{3} &= \frac{V_{0}}{A_{0}Y_{2}} \left[ (Y_{2}+Y_{4})(Y_{1}+Y_{2}+Y_{3}) \right] \\ V_{i}Y_{1} &= V_{0} \left[ (\frac{Y_{2}+Y_{4})(Y_{1}+Y_{2}+Y_{3})}{A_{0}} - \frac{Y_{2}}{A_{0}} - \frac{Y_{3}}{A_{0}} \right] \\ V_{i}Y_{1} &= V_{0} \left[ (\frac{Y_{2}+Y_{4})(Y_{1}+Y_{2}+Y_{3}) - A_{0}Y_{2}Y_{3} - \frac{Y_{2}Y_{2}}{A_{0}} \right] \\ \frac{V_{0}}{V_{i}} &= \left[ \frac{A_{0}Y_{1}Y_{2}}{(Y_{2}+Y_{4})(Y_{1}+Y_{2}+Y_{3}) - A_{0}Y_{2}Y_{3} - \frac{Y_{2}Y_{2}}{Y_{3}} \right] \\ \frac{H(s) = V_{0}(s)}{V_{i}(s)} &= \frac{A_{0}Y_{1}Y_{2}}{Y_{1}Y_{2} + Y_{4}(Y_{1}+Y_{2}+Y_{3}) + (1 - A_{0})Y_{2}Y_{3}} \right] \end{aligned}$$

Sub

$$N_1 = Y_2 = 1/R$$

$Y_3 = Y_4 = SC$

$$= \frac{A_0(1/R)^2}{(Y_R)^2 + SC [^2/R + SC] + (1 - \Lambda_0) \frac{SC}{R}}$$

$$= \frac{A_0(1/R)^2}{(Y_R)^2 + \frac{2SC}{R} + (1 - \Lambda_0) \frac{SC}{R} + S^2 c^2}$$

$$= \frac{A_0(1/R)^2}{(Y_R)^2 + \frac{SC}{R} (3 - \Lambda_0) + S^2 c^2}$$

$$= \frac{A_0(1/R)^2}{Multiply R^2 in Numk Deno}$$

$$H(s) = \frac{Ao}{1+(3-Ao)SCR+S^{2}c^{2}R^{2}}$$

$$H(s) = \frac{Ao}{S^{2}c^{2}R^{2}+(3-Ao)SCR+1}$$

$$IeE w_{h} = Rc$$

$$H(s) = \frac{Ao}{S^{2}/w_{h}^{2}+(3-Ao)} = \frac{A}{2}$$

$$\begin{aligned} H(s) &= \frac{A_0 \cup h^2}{s^2 + (3 - A_0) s \cup h + (\omega_h)^2} \\ &= \frac{A_0}{(j \cup /\omega_h)^2 + (3 - A_0) j (\omega / \omega_h) + 1} \\ &= \frac{A_0}{(j \cup /\omega_h)^2 + (3 - A_0) j (\omega / \omega_h) + 1} \\ &= \frac{A_0}{(j \cup /\omega_h)^2 + (3 - A_0) j (\omega / \omega_h) + 1} \\ &= \frac{A_0}{(j \cup /\omega_h)^2 + (j \cup /\omega_h)} \\ &= \frac{A_0}{(j \cup /\omega_h)^2 + (j \cup /\omega_h)} \\ &= \frac{A_0}{(j \cup /\omega_h)^2 + (j \cup /\omega_h)} \\ &= \frac{A_0}{(j \cup /\omega_h)^2 + (j \cup /\omega_h)^2} \\ &= \frac{A_0}{(j \cup /\omega_h)^2 + (j \cup /\omega_h)^2} \\ &= \frac{A_0}{(j \cup /\omega_h)^2 + (j \cup /\omega_h)^2} \\ &= \frac{A_0}{(j \cup /\omega_h)^4} \\ &= \frac{A_0}{(j \cup /\omega_h)^4}$$

$$\frac{Pb}{l} i \cdot Designa second order Buttencontt

Low Pass gilter having upper cut off

frequency 1kHz.

$$f = \frac{1}{2\pi \epsilon_c}; c = 0 \cdot lyF; A_0 = 1 + \frac{R_f}{R_1}$$

$$d = 3 - A_0 \quad let d = 1 \cdot 414$$

$$1 \cdot 414 - 3 = -A_0; A_0 = 1 \cdot 586$$

$$A_0 = 1 + \frac{R_f}{R_1}$$

$$1 \cdot 586 = 10 + \frac{R_f}{R_1}$$

$$1 \cdot 586 = 10 + \frac{R_f}{10}$$

$$1 \cdot 586 = 10 + \frac{R_f}{R_1}$$

$$1 \cdot 586 = 10 + \frac{R_f}{R_1}$$$$

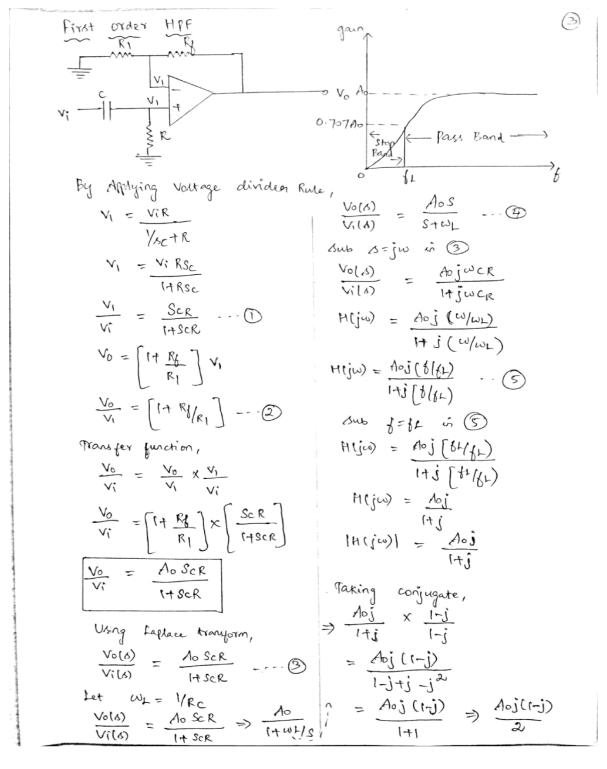

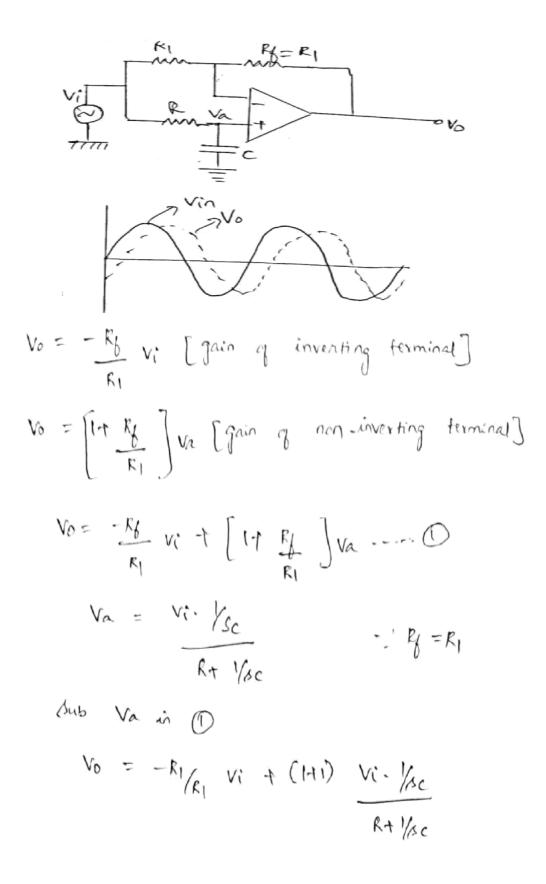

### **3.4 HIGH PASS FILTER**

#### **First Order HPF**

A High Pass Filter is the exact opposite to the low pass filter. High pass filters are often formed simply by interchanging frequency-determining resistors and capacitors in low-pass filters.

$$= \frac{A_{0}j - A_{0}j^{2}}{z}$$

$$= \frac{A_{0}j^{2}}{z}$$

.

$$= \frac{A_{0}\delta^{2}}{\delta^{2} + \delta\omega_{L}[3 - \Lambda_{0}] + \omega_{L}^{2}}$$

$$\Rightarrow \text{ the numerator and denominator by} \\\delta^{2}, \\ \frac{\Delta\delta^{2}}{\delta^{2}/\delta^{2}}$$

$$\Rightarrow \frac{A\delta^{2}/\delta^{2}}{\delta^{2}/\delta^{2} + \frac{\delta\omega_{L}[3 - \Lambda_{0}]}{\delta^{2}} + \frac{\omega_{L}^{2}}{\delta^{2}}$$

$$= \frac{A\delta}{1 + \frac{\omega_{L}[3 - \Lambda_{0}]}{\delta} + \frac{\omega_{L}^{2}}{\delta^{2}}}$$

$$= \frac{A\delta}{1 + \frac{\omega_{L}[3 - \Lambda_{0}]}{\delta} - \frac{\omega_{L}^{2}}{\delta^{2}}}$$

$$= \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}} = \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}}$$

$$= \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}} = \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}}$$

$$= \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}} = \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}} = \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}}$$

$$= \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}} = \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}} = \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}} = \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}}$$

$$= \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}} = \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}} = \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}} = \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}} = \frac{A\delta}{1 + \frac{\omega_{L}}{\delta}}$$

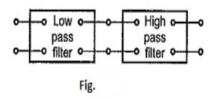

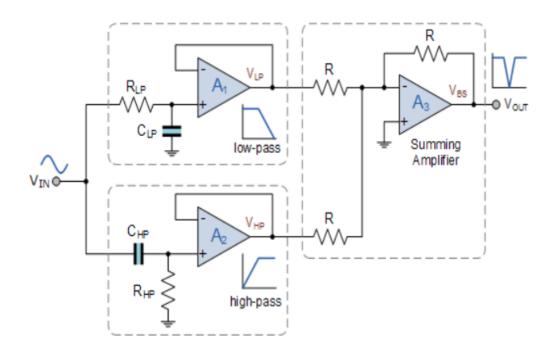

# 3.5 Band Pass Filter

Band pass filter pass a certain range of frequencies (called as **pass band**) while attenuate all other frequencies. Such band pass filters can be obtained by connecting low pass filter sections in cascade with high pass filter sections as shown in Fig.

In above type of connection, the cut-off frequency of low pass filter section must be selected higher than that of high pass filter section.

Although cascade connection of low pass filter and high pass filter sections functions properly as band pass filter, it is more economical to combine both sections in one single filter section.

- Narrow Band Pass Filter Q > 10

- Wide Band Pass Filter Q< 10

#### Second Order Narrow Band Pass Filter

-

Bundwidth:

$$B_{LD} = \frac{f_{0}}{R_{0}} = \frac{L_{D}}{2\pi\pi\omega_{0}R_{c}} = \frac{1}{2\pi\pi\kappa_{c}}$$

$$B_{LU} = \frac{f_{0}}{R_{0}} = \frac{G_{5}\left(\frac{c_{2}+c_{5}}{2}\right)}{2\pi\pic_{2}c_{3}}$$

$$C_{4} = c_{3} = c$$

$$G_{4in}, = H(A) = -\left[\frac{G_{1}}{G_{5}}\right]c_{2}$$

$$C_{4} = c_{4}c$$

$$H(A) = -\left[\frac{G_{1}}{G_{5}}\right]c$$

$$C_{4} = -\frac{G_{1}}{G_{5}}c$$

$$C_{5} = -\frac{G_{5}}{G_{5}}c$$

$$C_{5} = -\frac{G_{$$

$$= \int \left[ \frac{Ab}{(\omega e^{2} - \omega^{2} + j \alpha \omega)} \right]^{2}$$

$$= \int \left[ \frac{Ab}{(\omega e^{2} - \omega^{2} + j \alpha \omega)} \right]^{2}$$

$$M(j\omega) = \frac{Ab}{(\omega e^{2} - \omega^{2} + j \alpha \omega)}$$

$$\frac{M}{(\omega e^{2} - \omega^{2} + j \alpha \omega)}$$

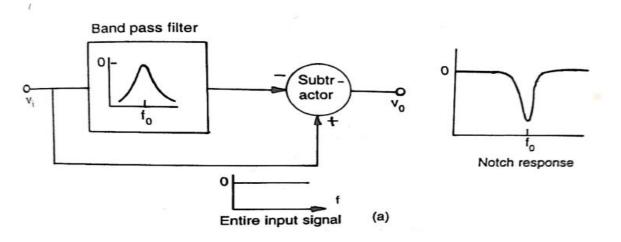

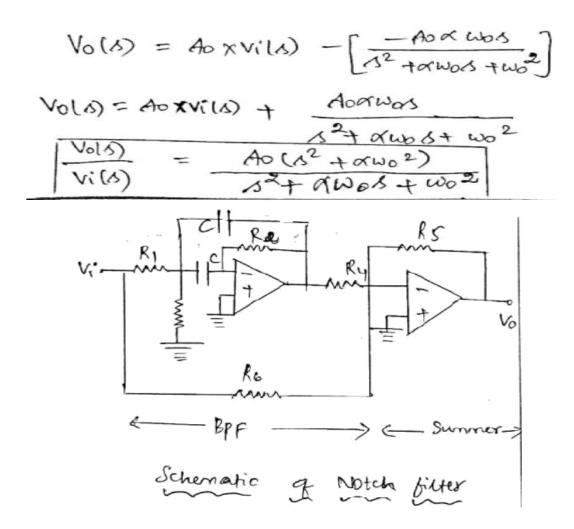

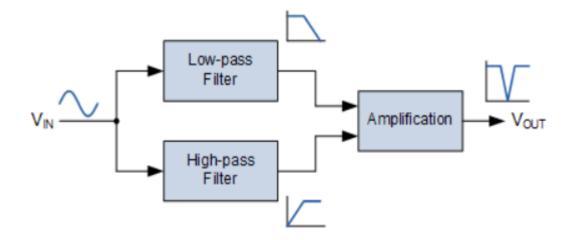

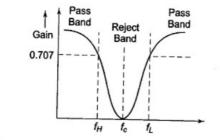

#### 3.6 Band Stop / Reject Filter

A band Stop Filter known also as a Notch Filter, blocks and rejects frequencies that lie between its two cut-off frequency points passes all those frequencies either side of this range

- Also called a band stop or band elimination

- 1. Narrow band reject (Q>10)

- 2. Wide band reject (Q<10)

#### Narrow band reject filter

• Narrow band reject filter is commonly called a notch filter- useful for the rejection of a single frequency such as 50Hz power line frequency.

Wide band reject filter

Figure (a) shows wide band reject filter using a low pass filter, a high pass filter and a summing amplifier. For a proper band reject response, the low cutoff frequency f<sub>L</sub> of the high pass filter must be larger than the high cutoff frequency f<sub>H</sub> of the low pass filter. Also, the pass band gain of both high pass and low pass sections must be equal.

(b) Frequency Response of a Wide Band Reject Filter

## **3.7 All Pass Filter**

An all-pass filter is that which passes all frequency components of the input signal without attenuation but provides predictable phase shifts for different frequencies of the input signals. The **all-pass filters** are also called delay equalizers or phase correctors.

$$= -Vi + 2Vi (1/kc)$$

$$= -Vi + 2Vi (kc)$$

$$= -Vi + 2Vi (kc)$$

$$\frac{SeR+1}{Sc}$$

$$= -Vi + 2Vi (kc)$$

$$\frac{SeR+1}{Sc}$$

$$= -Vi + 2Vi$$

$$\frac{SeR+1}{Sc}$$

$$V_0 = -Vi + 2Vi$$

$$\frac{SeR+1}{Sc}$$

$$V_0 = -Vi + 2Vi$$

$$\frac{SeR+1}{Sc}$$

$$V_0 = -Vi + 2Vi$$

$$\frac{SeR+1}{Sc}$$

$$\begin{aligned} \mathcal{A} = \tilde{g}\omega \\ \left[\frac{V_0}{V_1}\right] &= \frac{[-\tilde{g}\omega c_R]}{[+\tilde{g}\omega c_R]} \times \frac{[-\tilde{g}\omega c_R]}{[+\tilde{g}\omega c_R]} \\ \Rightarrow \frac{[\tilde{f} + \tilde{g}^2 \omega^2 c_n^2 R_n^2]}{[\tilde{f} + \tilde{g}^2 \omega^2 c_n^2 R_n^2]} + \frac{2\tilde{g}\omega R_n}{[\tilde{f} + \omega^2 c_n^2 R_n^2]} \\ &= \frac{[-\omega^2 c_n^2 R_n^2]}{[+\omega^2 R_n^2 c_n^2]} + \frac{(-2\tilde{g}\omega R_n)}{[+\omega^2 R_n^2 c_n^2]} \\ &= \frac{((-\omega^2 R_n^2 c_n^2)^2}{[+\omega^2 R_n^2 c_n^2]} \\ &= \frac{((-\omega^2 R_n^2 c_n^2)^2}{(1+\omega^2 R_n^2 c_n^2)^2} \\ &= \frac{(-\omega^2 R_n^2 c_n^2 + \omega^2 R_n^2 c_n^2)}{(1+\omega^2 R_n^2 c_n^2)^2} \\ &= \frac{(1+\omega^2 R_n^2 c_n^2)^2}{(1+\omega^2 R_n^2 c_n^2)^2} \end{aligned}$$

From equations given above it is obvious that the amplitude of  $v_{out} / v_{in}$  is unity, that is  $|v_{out}| = |v_{in}|$  throughout the useful frequency range and the phase shift between the input and output voltages is a function of frequency.

# SCHOOL OF BIO AND CHEMICAL ENGINEERING DEPARTMENT OF BIOMEDICAL ENGINEERING

UNIT - IV -BIOSIGNAL CONDITIONING- SBMA1504

# 4. A/D AND D/A CONVETERS

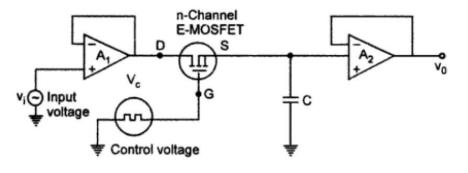

# 4.1 Sample and Hold Circuit

- A sample and hold circuit is a circuit which samples an input signal and holds onto its last sampled value until the input is sampled again.

- Sample and hold circuits are commonly used in analogue to digital converts, communication circuits, PWM circuits etc.

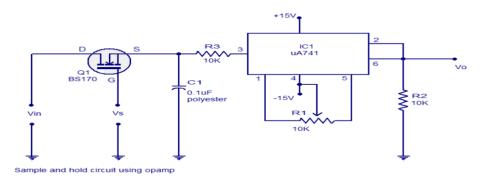

- The circuit shown is based on uA 741 opamp, n-channel E MOSFET BS170 and few passive components.

Fig. (a) Sample and hold circuit

- MOSFET BS170 (Q1) works as a switch while opamp uA741 is wired as a voltage follower.

- The signal to be sampled (Vin) is applied to the drain of MOSFET while the sample and hold control voltage (Vs) is applied to the source of the MOSFET.

- The source pin of the MOSFET is connected to the non inverting input of the opamp through the resistor R3.

- C1 which is a polyester capacitor serves as the charge storing device. Resistor R2 serves as the load resistor while preset R1 is used for adjusting the offset voltage.

- During the positive half cycle of the Vs, the MOSFET is ON which acts like a closed switch and the capacitor C1 is charged by the Vin and the same voltage (Vin) appears at the output of the opamp.

- When Vs is zero MOSFET is switched off and the only discharge path for C1 is through the inverting input of the opamp. Since the input impedance of the opamp is too high the voltage Vin is retained and it appears at the output of the opamp.

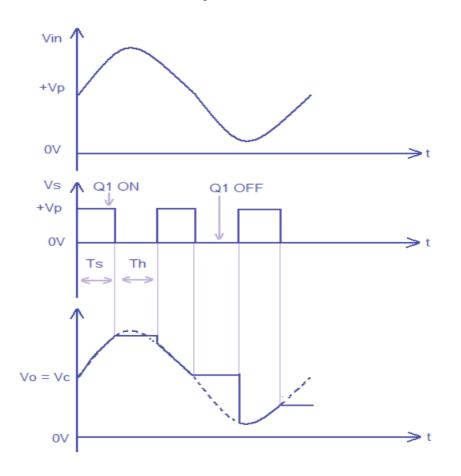

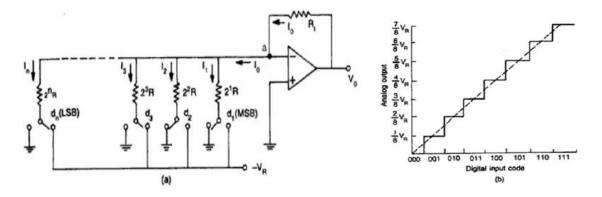

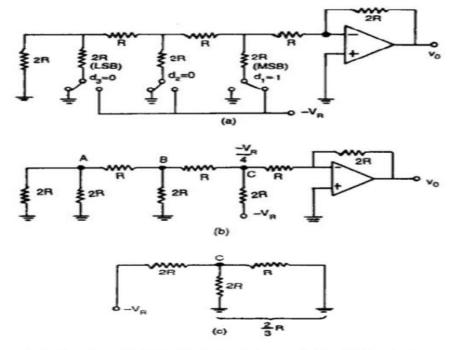

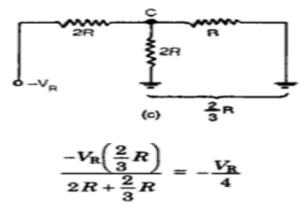

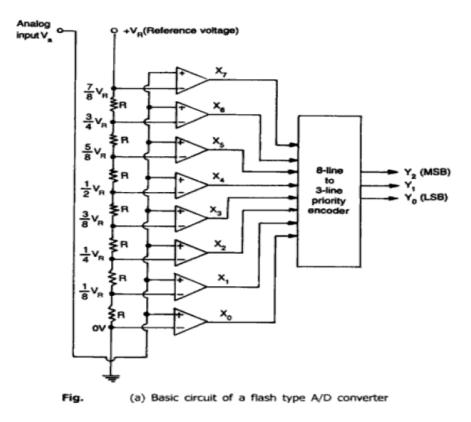

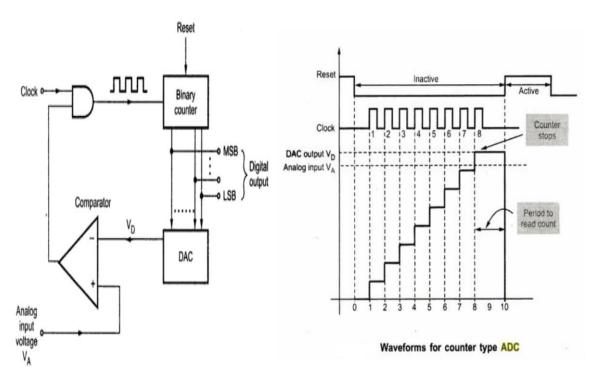

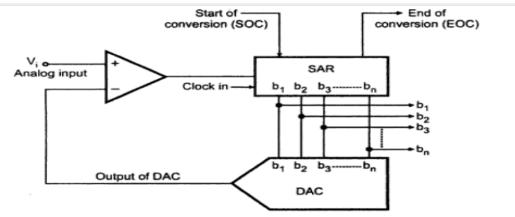

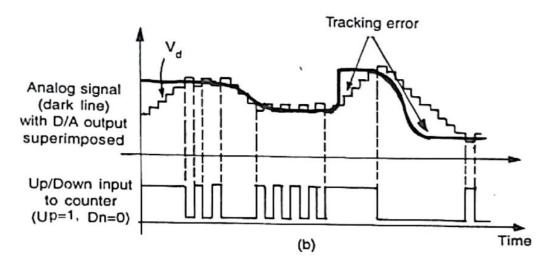

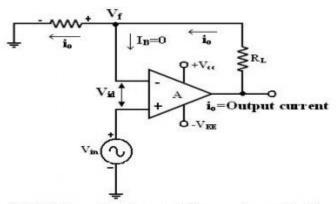

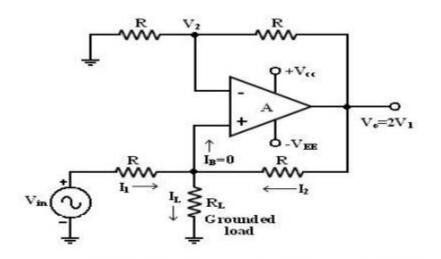

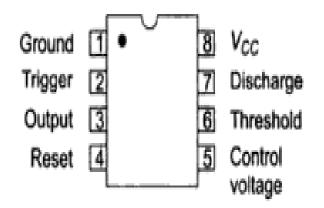

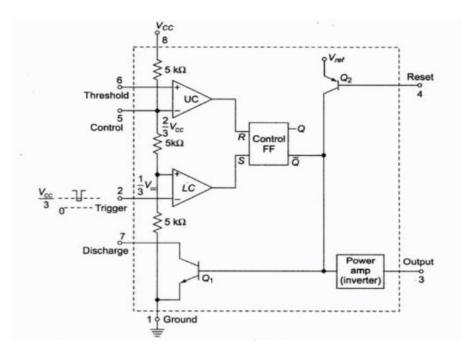

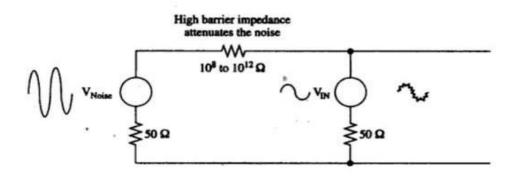

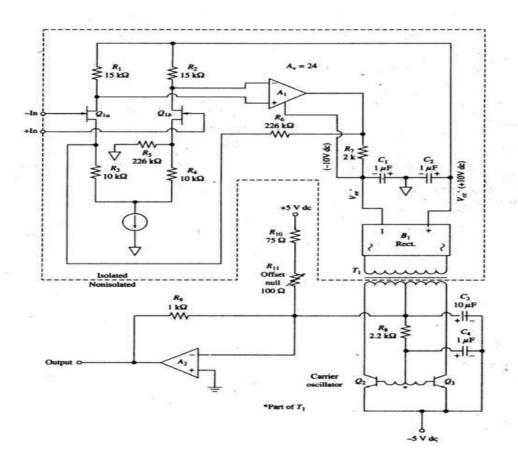

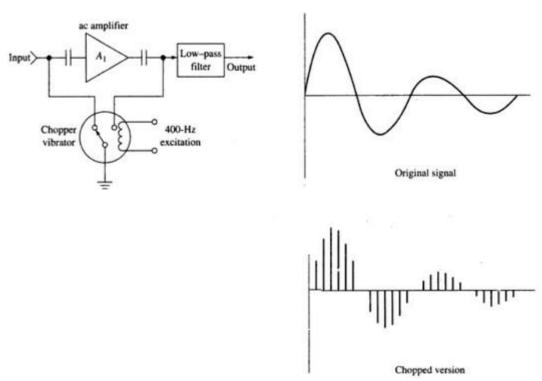

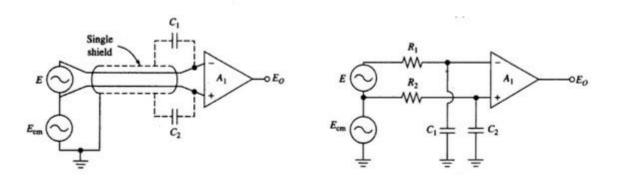

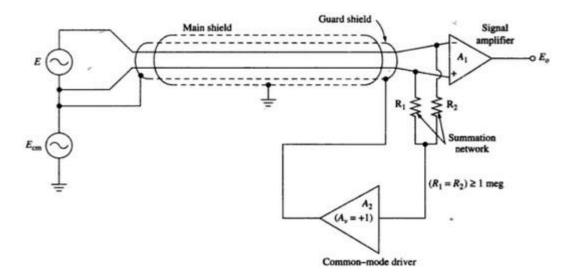

- The time periods of the Vs during which the voltage across the capacitor (Vc) is equal to Vin are called sample periods (Ts) and